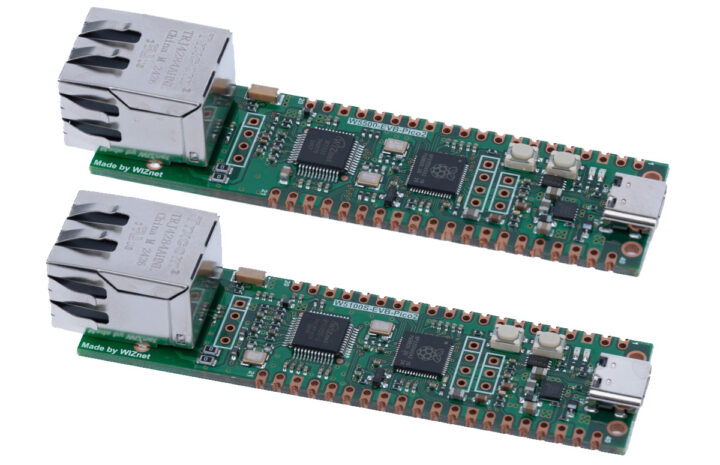

WIZnet has recently launched two new Raspberry Pi RP2350-based Ethernet boards – W5100S-EVB-Pico2 and W5500-EVB-Pico2 – based on different Ethernet controllers. The entry-level W5100S-EVB-Pico2 is built around the W5100S controller that features 4 independent sockets and 16 Kbytes of buffer memory. On the other hand, the W5500-EVB-Pico2 is built around the W5500, which features 8 sockets, 32 Kbytes of buffer memory, and improved security features such as OTP memory, Secure Boot, and Arm TrustZone technology. These make the W5500-EVB-Pico2 ideal for projects with robust network handling and advanced security measures.

After the recent announcement of the $5 Raspberry Pi Pico 2 we have seen many development boards built around the RP2350 MCU, including the Challenger+ RP2350 WiFi6/BLE5, the Solder Party’s RP2350 Stamp, the Seeed Studio XIAO RP2350, the Cytron MOTION 2350 Pro, and more. Feel free to check those out If you are interested in RP2350-based dev boards.

W5100S-EVB-Pico2 and W5500-EVB-Pico2 specifications

- Microcontroller – Raspberry Pi RP2350A

- CPU – Dual-core Arm Cortex-M33 processor @ 150MHz (RISC-V cores are not mentioned, so they are likely not used at all)

- Memory – 520KB internal RAM

- 8KB OTP Storage

- Storage – 16Mbit SPI flash

- Ethernet

- W5100S-EVB-Pico2 (10/100 Mbps Ethernet with Auto-Negotiation (Full/Half Duplex) and RJ45 connector)

- W5100S Hardwired TCP/IP CHIP

- Supports TCP, UDP, WOL over UDP, ICMP, IGMPv1/v2, IPv4, ARP, PPPoE

- 4 Independent Hardware SOCKETs

- Internal 16 Kbytes Memory for TX/ RX Buffers

- W5500-EVB-Pico2 (10/100 Mbps Ethernet with Auto-Negotiation (Full/Half Duplex) and RJ45 connector)

- W5500 Hardwired TCP/IP CHIP

- Supports TCP, UDP, ICMP, IGMP, IPv4, ARP, PPPoE

- 8 Independent Hardware SOCKETs

- Internal 32 Kbytes Memory for TX/ RX Buffers

- Both – High-Speed Serial Peripheral Interface (SPI MODE 0, 3)

- W5100S-EVB-Pico2 (10/100 Mbps Ethernet with Auto-Negotiation (Full/Half Duplex) and RJ45 connector)

- USB – 1x USB C-Type port for power, data, and reprogramming Flash

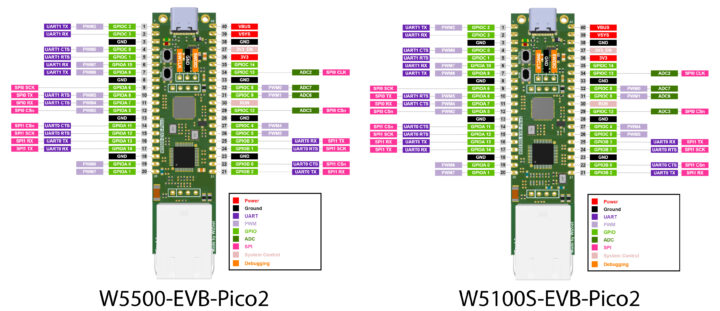

- I/Os

- 40 pin 0.1″ through-hole pins and edge castellations with

- 2x UART, 2x SPI, 2x I2C

- 16x PWM

- 4x 12-bit 500ksps Analogue to Digital Converter (ADC)

- 3x Programmable IO (PIO) blocks, 12 state machines total

- HSTX peripheral

- 1x Timer with 4 alarms,

- 1x Real Time Counter

- 40 pin 0.1″ through-hole pins and edge castellations with

- Security – OTP, Secure Boot, Arm TrustZone

- Debugging – SWD headers

- Power Supply

- Built-in Switch-mode DC-DC converter (replacing LDO for enhanced power efficiency)

- VBUS – DC 5V (+/- 10%)

- VSYS – 4.3V to 5.5V

- Built-in Switch-mode DC-DC converter (replacing LDO for enhanced power efficiency)

- Dimensions – 80 x 20mm

- Operation Conditions

- Max Operating Temperature – 85°C (including self-heating)

- Min Operating Temperature: -20°C

- Recommended max ambient temperature: 70°C

- Certification – CE, FCC, AWS Qualification, Microsoft Azure Certification

One thing to note is that GPIO16-21 is dedicated to Ethernet on both boards. More information about the W5100S-EVB-Pico2 and W5500-EVB-Pico2 can be found on their respective Wiki Pages including C/C++ code samples for Ethernet, AWS, Azure, and LwIP.

As of this writing, the board has just been released on Mouser and DigiKey. On Mouser, the W5100S-EVB-Pico2 and W5500-EVB-Pico2 are priced at $19.24 in single quantities. The W5100S model is also listed on DigiKey, but there is a minimum order requirement of 20 units, bringing the total cost to $280.59, which translates to a per-unit price of $14.03.

Debashis Das is a technical content writer and embedded engineer with over five years of experience in the industry. With expertise in Embedded C, PCB Design, and SEO optimization, he effectively blends difficult technical topics with clear communication

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I can also see the W6100-EVB-Pico2 on Mouser and the documentation website:

https://docs.wiznet.io/Product/iEthernet/W6100/w6100-evb-pico2

Basic info for W6100:

Thanks for the link! I was a bit curious about this “X sockets …” that made me think that the stack is entirely offloaded to the chip and that only commands are exchanged with it. From the link above I found the datasheet and that’s exactly this. See page 57, “4.2.3 command register”. You have OPEN/CLOSE, LISTEN, CONNECT, SEND, RECV etc. It also supports raw sockets in IPv4 and IPv6. I think the amount of effort needed to use such stacks in existing software should be minimal.

As always with TCP/IP offloading, one must be careful about not using that over the internet for sensitive stuff as TCP is always a tradeoff between security and reliability, and when implemented in a closed solution you cannot update nor tweak it. But this can have plenty of use cases in automation and monitoring.

TCP isn’t really about security and it’s not really about making it tradeoffs. With that said it does have some inherent to the protocol such as the initial handshake which can be used to do a denial of service attack or a number of things.

Some of those also exist in UDP too, like how you can fake the second IP fragment onwards.

Either way, I believe that offload is kinda needed in this chip because they only offer the basic SPI and if you added the protocol overheads, it would probably be too slow. From their own website, they only get 3.5 mbps even with 36MHz SPI.

A esp32 with Ethernet seems capable to almost saturate a 100mbit link according this information: https://esp32.com/viewtopic.php?t=2013

Wonder if this also includes some offloading?

Seems like to depend on the hardware chosen: https://medium.com/@jithmi.samodya1/comparison-ethernet-on-esp32-with-w5500-or-esp32-internal-mac-with-external-phy-chip-4e3350a76e27

It’s using ESP32 MAC + External PHY.

The MAC does include some offload capabilities. Among the mentioned in the manual

> Support for the offloading of received IPv4 and TCP packets encapsulated by an Ethernet frame in the reception function

> Support for checking IPv4 header checksums, as well as TCP, UDP, or ICMP (Internet Control Message Protocol) checksums encapsulated in IPv4/IPv6 packets in the enhanced reception function

> Calculating the IPv4 header checksum, as well as the TCP, UDP, or ICMP checksum, and then inserting them into frames transmitted in store-and-forward mode.

So basically it can do checksum offload for Rx and Tx from what I gather, except for IPv6.

I believe that for the first one, it basically just removes the IPv4 and TCP packets from the ethernet one before delivering it to the software.

It’s not like the W5500 chip where you command it like a software socket

But it does not have the slow interface bottleneck.

Yes both are different. With ESP32 you need to bring your TCP stack (one is provided in the SDK). But if you want to write your own RTOS from scratch, you need to do everything yourself. With W5500 you can use this already available stack in your high-level application so it’s much easier to use, but with more limitations, of course.

I can’t find any reason not to prefer a esp32 based ethernet board over this one…

Can you?

Price, number of pins and availability of PIO.

The last esp32 with Ethernet onboard I stocked sold for less then $10 each (free shipping included).

Plenty of GPIO’s (never saturated them but could be easily extended with a port multiplier).

And about the availability of a public information officer (PIO) – I got no idea 😂

PIO is Programable Input Output blocks in the Rasperry Pi MCUs. Those are programmable state machines that you can use to implement a variety of interfaces and protocols (within the small space you have).

Essentially you can bitbang but at much faster and reliable way.

The new W55RP20-EVB-Pico looks very interesting, particularly if it has the ability to support additional modules including PoE as hinted at on the Pi Hut store page:

https://thepihut.com/products/wiznet-w55rp20-evb-pico

Also that it’s 100% software/pin compatible with the W5500-EVB-PICO!

I really want more info on the PoE module plans…