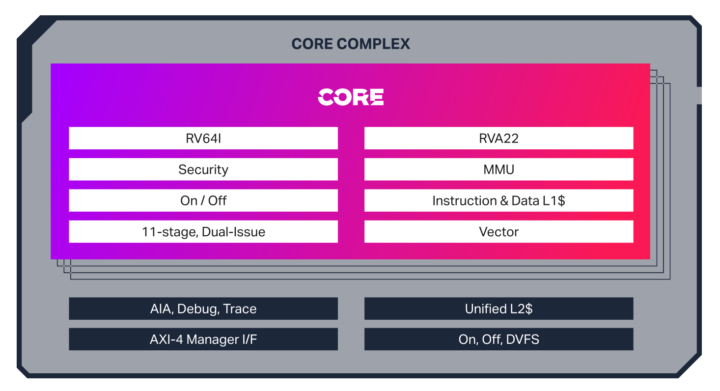

Imagination has expanded its Catapult product portfolio to include a new RISC-V core, the Imagination APXM-6200 CPU. The APXM-6200 is a 64-bit, in-order application processor with an 11-stage, dual-issue pipeline.

There isn’t much information on the new Imagination RISC-V core on the product page but we know it offers “best-in-class” performance density, a minimal silicon footprint, and industry-standard security features.

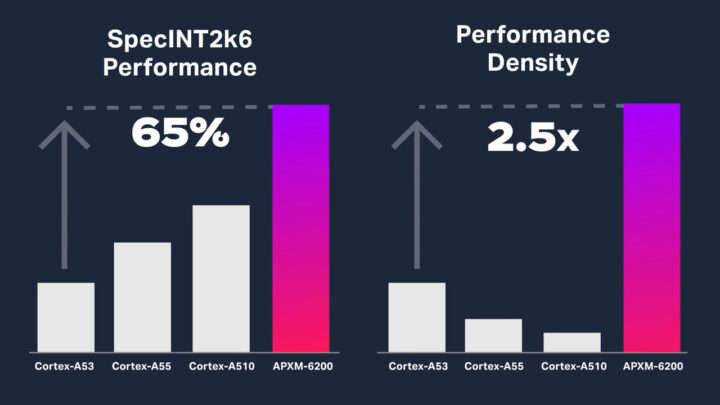

The CPU is targeted at intelligent consumer and industrial applications and delivers a 2.5x improvement in performance density and a 65% improvement in normalized performance over comparable Arm Cortex-A53 and other cores on the market. It’s also faster than the Cortex-A510 Armv9 core in SpecINT2k6.

Imagination claims that combining the APXM-6200 CPU with their GPUs will ensure a 2x increase in bus utilization and a 2x reduction in memory traffic. It also comes with RISC-V vector extensions, and AI compute libraries and supports fast data coupling with AI accelerators for improved performance with artificial intelligence workloads.

There are options for single, dual, and quad-core configurations for customers depending on their requirements. The cores share the same memory hierarchy (cache coherence) and the system offers per-core power control for maximum efficiency. For security, the APXM-6200 core uses the RISC-V Supervisor Domains Access Protection architecture extension for memory isolation and address space protection in multi-domain use cases.

Imagination APXM-6200 CPU specifications:

- Key Features

- Instruction Set Architecture – RISC-V, 64-bit

- Pipeline – 11 Stage, Dual Issue

- Core Complex – Up to 4 cores with cache coherency

- Cluster – Per-core power control

- Security – Static Supervisor Domain Isolation, Vector Cryptography

- RISC-V Extensions

- Profile – RVA22

- Base Extensions – RV64I

- Floating Point – Single Precision Floating Point (F) / Double Precision Floating Point (D)

- Vector – V, Zfh, Zfhmin

- Vector Crypto – Zkr, Zkt

- Memory

- Instruction Cache – Configurable (16KB to 128KB)

- L1 Data Cache – Configurable (16KB to 128KB)

- L2 Cache – Configurable (128KB to 1MB)

- Accelerator – Accelerator Coherency Port (accelerator can share L2 cache)

- Software and Tools

- Catapult SDK – GCC, LLVM, and GBD Support

- Catapult Studio – Visual Studio code-based IDE

- OS Support – Linux, Android

- Models – Functional model, Performance model

- Development Platform – FPGA (including coupling with IMG GPU)

The APXM-6200 CPU is supported by the Catapult software development kit which offers FreeRTOS support, a reference secure boot monitor, and compatibility with tools such as GCC, LLVM compilers, and gdb debugger. The Integrated Development Environment (IDE), Catapult Studio, is based on VS Code and works across Windows, Ubuntu, CentOS, and MacOS. The IDE is compatible with the gem5 simulator and includes the Quick Emulator (QEMU) and Catapult software models for quick development and testing of RISC-V software before the hardware is even available.

The CPU is described as “Android and Linux-ready” and is expected to find applications in smart TVs, smart home hubs, wearables, and digital signage. It is also targeted at industrial applications such as the Industrial Internet of Things (IIoT) and logic and network controllers.

You can learn more about the APXM-6200 CPU via the press release and product page. Accessing the product overview requires filling out a sign-up form. Imagination will also be showcasing the CPU as part of their exhibit at Embedded World from 9-11 April.

Tomisin is a writer specializing in hardware product reviews, comparisons, and explainers. He is very passionate about small form factor and single-board computers.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress