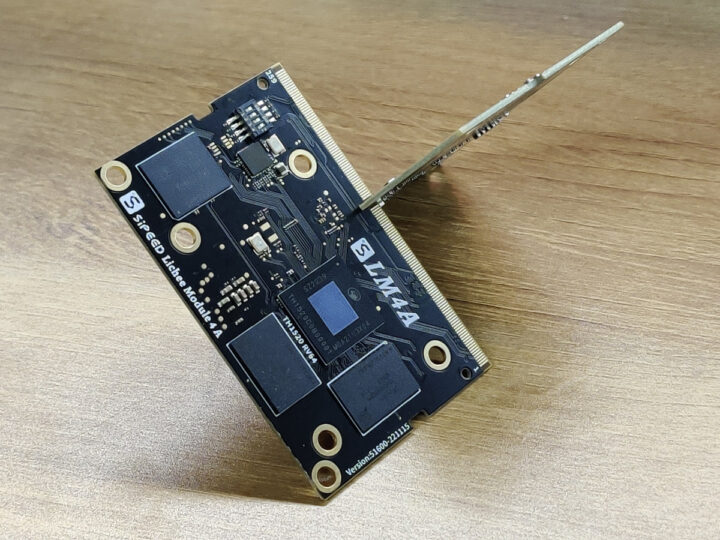

Sipeed LM4A is a quad-core RISC-V system-on-module based on the T-Head TH1520 SoC found in the ROMA laptop and destinated to be found in a Raspberry Pi SBC competitor as well as a cluster board.

The LM4A, which stands for Lichee Module 4 Model A, comes with 4GB to 16GB RAM, and up to 64GB flash, and connects to the carrier board through a 260-pin SO-DIMM connector. The TH1520 is one of the rare RISC-V SoCs with a 3D GPU, and the SBC based on LM4A has been shown to outperform the Raspberry Pi 4 in benchmarks as we’ll see below.

Sipeed LM4A specifications:

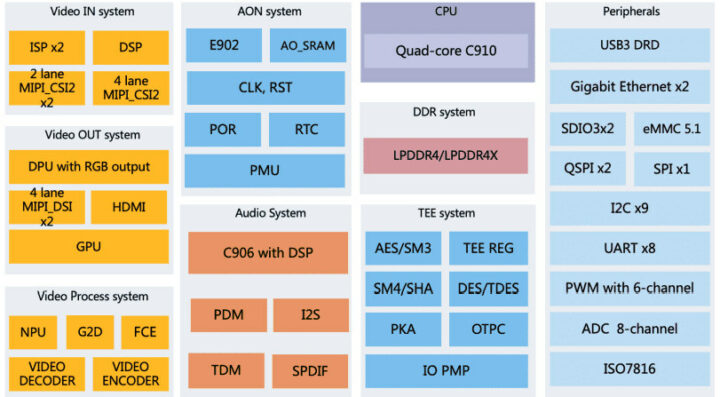

- SoC – Alibaba T-Head TH1520 quad-core RISC-V Xuantie C910 (RV64GCV) processor @ 2.5 GHz, Xuantie C906 audio DSP @ 800 MHz, low power Xuantie E902 core, 50 GFLOPS Imagination 3D GPU, and 4 TOPS NPU

- System Memory – 4GB, 8GB, or 16GB RAM

- Storage – Optional eMMC flash with 16GB, 32GB, or 64 GB capacity

- Networking – Up to 2x Gigabit Ethernet PHY

- Host interface – 260-pin SO-DIMM connector

- Dimensions – 69 x 45mm

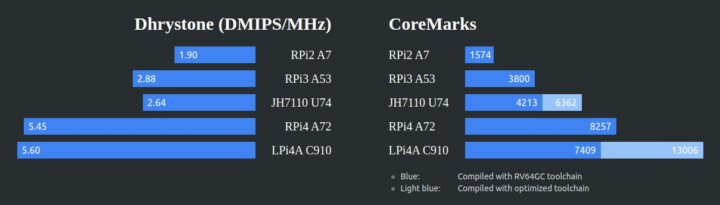

We do not have the full specifications at this time, but the company also shared some benchmarks showing the CPU performance of the upcoming LPi4A SBC @ 1.85 GHz against the Raspberry Pi 2/3/4, and a StarFive JH7110 board, likely the VisionFive 2.

I’m sure some will say the Dhrystone benchmark is outdated and susceptible to compiler flags, and those are true statements, but Dhrystone and CoreMark are the only results we have here for now. The LPi4A’s C910 core is shown to have similar performance or even higher than the Raspberry Pi 4’s Cortex-A72 core. The RISC-V board was only running at 1.85 GHz, so performance should scale if the processor can indeed be clocked at the advertised 2.5 GHz. Both the RV64GC toolchain and an optimized toolchain was used in CoreMark, but it’s unclear what the optimized toolchain does. There may be more details in the Yocto Linux BSP for TH1520 hosted on Gitee.

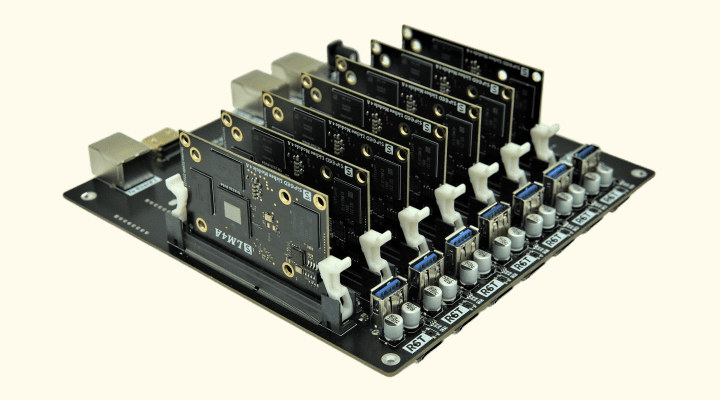

I could not find a photo of the LPi4A SBC, but Sipeed shared a photo of a cluster board with seven LM4A RISC-V system-on-module each with a USB 3.0 port, and I can see what looks like a few RJ45 ports on the back as well as on one HDMI output.

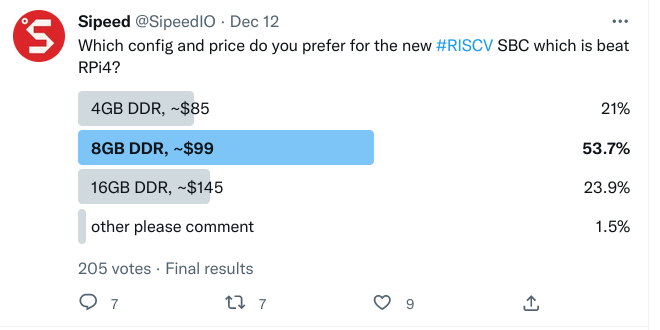

Sipeed says the LM4A TH1520 system-on-module will be available in Q1 2023. There’s no price announcement but the company put up a Twitter poll about pricing and specs for a Raspberry Pi competitor with a RISC-V SBC, so we should not be surprised if the LPi4A SBC launches with 8GB RAM for $99…

There’s limited public information at this time, but you can follow the development progress on Twitter or Weixin.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

At least what could be said is that assuming they used the same toolchain for both the U74 and C910, the latter seems to be roughly twice as fast in this benchmark This indicates that the products are evolving.

Does c910 have vector extension support? On official t-head website it doesn’t. This article seems to suggest c910 does support v extension.

The RV64GCV architecture comes from the post on Weixin.

> assuming they used the same toolchain for both the U74 and C910

The 2.64 DMIPS/MHz for the JH7110 is the exact number from the StarFive presentation back in August and the number in between (the 5.45 for the A72 in RPi 4) is copy&paste from here. According to Wikipedia an A72 scores 6.3-7.3 DMIPS/MHz but these numbers base on 2018 publications as such lacking 4 years of further compiler optimizations.

Just the usual BS generated by marketing departments but not numbers allowing for insights…

(What’s an estimation for 4 years compiler optimization influences on average percentage? ~5-35% for gcc3.4.4(2005)-7.1.0(2017), but not linearly and O0-O3 dependent, low on O0=<5% – higher on O3(~35%) differences possible?)

> What’s an estimation for 4 years compiler optimization influences on average percentage?

Who cares? You can generate any Dhrystone number you want (there’s a reason chip manufacturer’s marketing departments love this ‘benchmark’). To be of any use at least identical environment including same OS, libs, compiler version and settings are needed.

Just read through the list of criticisms collected here.

It’s simple enough, therefore people like it, being a ballpark number comparing cpu performance since decades. DMIPS. Ok, that’s a measurement scale for many, a majority (?).

If benchmark enthusiasts care, Dhrystone could be extended for advanced cache miss testing (?) on these days CPUs, since DMIPS are no random numbers, but justified within range (depending on compiler, libraries, os, (on thermal budget even) production nodes).

All in all, just another number one could have a fast impression from, if values are reasonable at all (50% offset seems justified, with otherwise having no numbers at all, being verfied in detail later, FMPOV).

Another question: Does Dhrystone scale linearly with higher/highest clock speeds (comparable to not being with voltages) and through compiler optimization levels (prob. no, so it could be critisized that compiler optimization numbering does not represent real measured advance in DMIPS values :), about O0~<5%, O1~<15%, O2~<41%, O3~<35% )?

(this for the light side in life, greetings)

> the number in between (the 5.45 for the A72 in RPi 4) is copy&paste from here

Same source as the 2.88 DMIPS/MHz score for the RPi 3 (Wikipedia and other sources rate an A53 with 2.3 DMIPS/MHz). And all the RPi Coremark scores are copy&paste from there.

Seems the only competitor hardware ‘measured’ are the JH7110 Coremarks. Both looking weird/flawed since StarFive showed a 5.09 Coremark/MHz rating which at 1.5GHz results in +7600 Coremarks.

Actually I didn’t look at the dhrystones metric but the other (coremarks) for the sole reason that they used two compilers, and that it’s unusual enough to indicate they did the measurement again. So I’m pretty sure they’ve run it themselves from the same code and compiler options, showing via 13006 vs 6362 that the new devices seems better. Of course I still know nothing about the perf of the former and would definitely not use such benchmarks to compare between various archs. All I’m saying is that they seem to make progress on the same arch.

> showing via 13006 vs 6362 that the new devices seems better.

The 6362 Coremarks for the JH7110 would result in 4.24 Coremark/MHz at 1.5 GHz while StarFive presented a 5.09 Coremark/MHz rating for JH7110/U74 and Wikichip agrees on the latter number also showing a 7.1 number for the C910 (+40% and not +100%) which is more in sync with 13006/1850 (7.03).

Obviously JH7110 was clocked only at 1.25 and not the ‘regular’ 1.5 GHz to create the impression C910 would be twice as fast.

> Obviously JH7110 was clocked only at 1.25

Oh that’s indeed perfectly possible. Until we know more about these chips, everything is in fact possible. After all we remember the espressobin that was supposed to run at 1.2 GHz despite nobody managing to get it to run stable past 800 MHz… Thus the performance in field with the default settings imposed to the user is ultimately what counts (i.e. what the vendor feels confident with).

In fact the 6362 value is run by me on Star64, with ordinary GCC 12, -march=rv64gc and only -O2 for compiler optimization.

There’s a RISC-V router based on LM4A in the works as well…

Cool. Exciting year for risc v.

I like that you can download official risc v Ubuntu images from ubuntu.com instead of downloading a board support package from SBC developer which comes with the crappy highly patched old Linux kernel

I find this board particularly tempting. I hope it will come with an OS running on it… or at least easy to flash. That’s been a problem in the past.

Looks interesting, especially form factor. Too bad it doesn’t have PCI nor eDP interface

Interesting, above 1/2 of interested customers comparing to RPi4 feel limited with below or generally prefer 8GB LPDDR4(x) (on a ~USD4/GB price difference)?

By design or accident emailing support @ sipeed.com is relabeled support @ tinyglobalcdnweb.qiniu.com.w.kunlunar.com and fails to get thru. I wanted to know cooling options. The boxed set has a stick on fan but it doesn’t look rugged enough.