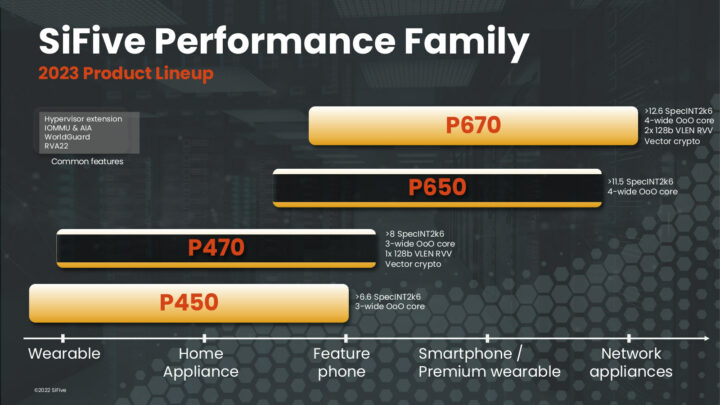

SiFive has announced two new RISC-V Performance cores with the P670 and P470 processors with RISC-V Vector Extension for AI/ML, media and sensor processing, and designed for high volume applications such as wearables, smart home, industrial automation, AR/VR, and other consumer devices.

The P670 is comparable to the Cortex-A78, and the P470 is comparable to the Cortex-A55. Both support the standardized RISC-V RVA22 profile for better OS compatibility and implement RISC-V Vector v1.0 and Vector Cryptography extensions.

The SiFive Performance P470 and P670 share the following features:

- Full RISC-V RVA22 profile compliance

- Full, Out-of-Order, RISC-V Vector implementation, based on the ratified RISC-V Vector v1.0 Specification

- RISC-V Vector Cryptography extensions

- SiFive WorldGuard system security

- Support for virtualization, including a separate IOMMU for accelerating virtualized device IO

- Advanced Interrupt Architecture (AIA) compliant interrupt controller with better support for Message Signal Interrupts (MSI) and virtualization

- Enhanced scalability with fully coherent multi-core, multi-cluster, with support for up to 16 cores

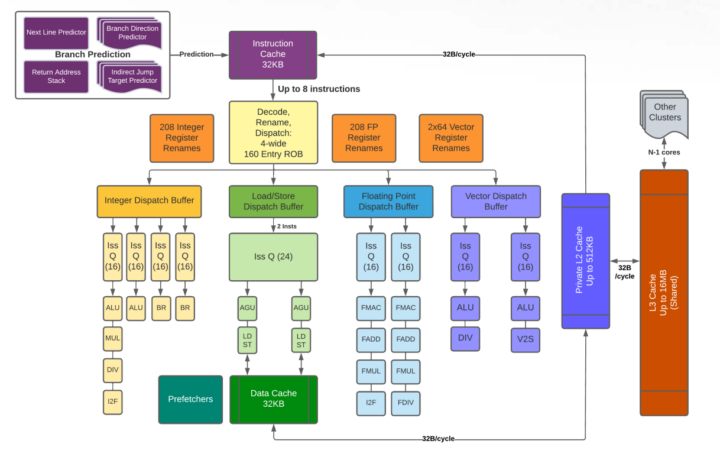

SiFive Performance P670

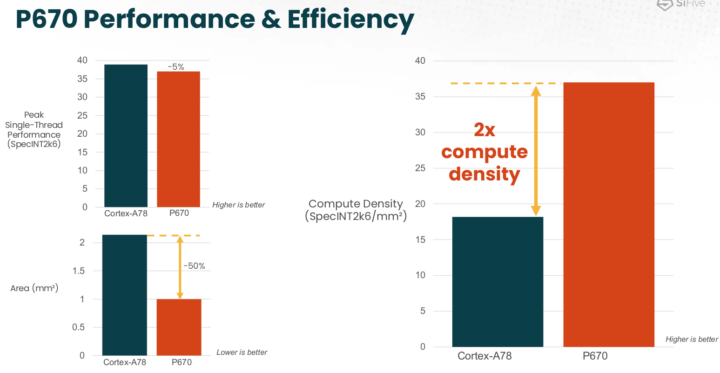

The SiFive Performance P670 core is comparable to the Arm Cortex-A78, can achieve a frequency of up to 3.4 GHz when manufactured with a 5nm process, delivers a performance of more than 12 SpecINT2k6/GHz, as well as higher single thread performance and twice the compute density compared to “legacy solution” (aka Cortex-A78), and embeds two 128-bit Vector ALUs compliant with the ratified RISC-V Vector v1.0 specification. It will be found in premium wearables, networking, robotics, and mobile SoCs, and is an upgrade to the SiFive Performance P650, which lacks the Vector Extensions.

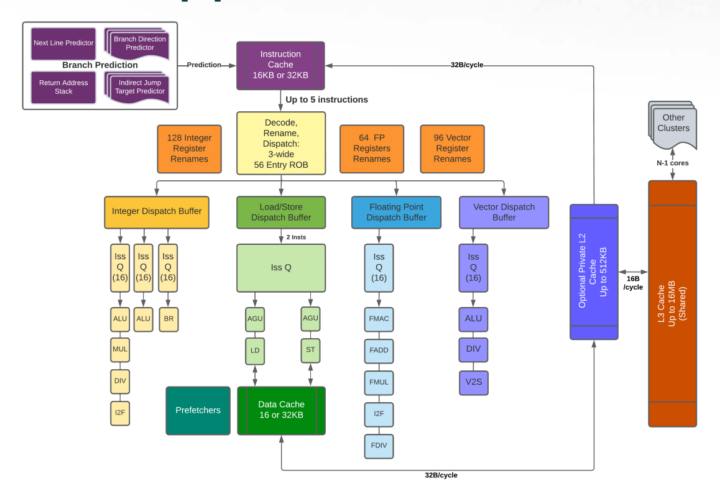

SiFive Performance P470

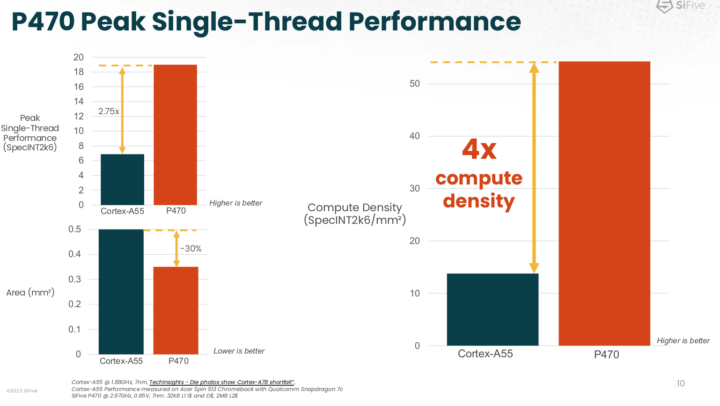

The SiFive Performance P470 core will compete against the Arm Cortex-A55 core, yet it is said to also achieve up to 3.4GHz with a 5nm process. It also offers 8+ SpecINT2k6/GHz within a small area and power envelope, as well as four times the compute density of”a leading competitor” also known as Cortex-A55… While the P670 includes two 128-bit RISC-V Vector ALU, the P470 embeds only one. SiFive will also release the P450 with the similar specifications as the P470 minus the Vector Unit.

Note that the peak single-thread performance above compared a Cortex-A55 @ 1.88 GHz to a SiFive P470 @ 2.97 GHz both using a 7nm process. It’s still faster after adjusting for the frequency, but not as dramatic, and it will likely be clocked lower in products such as wearables for the sake of battery life.

The SiFive P470 and P670 cores will be supported by Android thanks to their standardized RISC-V RVA22 profile, as well as Android Wear OS and Linux. SoCs and products based on the new RISC-V core should be available in 2023. More details can be found on the product page and the press release.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Nice! Really looking forward to a Vision Five with these …in 2025. lol

Wonder what cherry picked test they used to get those performance ratios? Probably something benefiting from the vector extensions. Kudos for completing the Vector extensions spec finally.

But, I agree with @bernstein. Actual chips when? The cortex-A78 shipped in products two years ago.

> Wonder what cherry picked test they used to get those performance ratios?

Well, they use SPEC2006 most probably for a reason (SPEC2017 is the ‘current’ release), the P470 is clocking almost twice as fast as the A55 (3 vs. 1.88 GHz) and those SPEC benchmarks vary massive with compiler flags. Server manufacturers often submit SPEC2017 scores up to 2 or even 3 times higher than those e.g. generated by Anandtech for their reviews.

I missed the legend on the chart. Thanks Thomas. And, yeah, SPEC tests have always been more of a compiler benchmark going way back to my earliest experiences with them in the beginning of the 1990s when RISC began to mean Really In the Silly Compiler.

I don’t remember which one it was, but one of the vendors got caught out tuning their compiler to recognize a specific SPEC subtest and auto set come ‘optimization’ which bypassed most of the actual code resulting in a huge performance increase. And by ‘optimization’ I mean it only worked for the data set that came with the benchmark, the program would produce incorrect results for other data sets. Fun times.

Very impressive results, partucularly on P670. If I read it right it would be somewhere along the Intel SanduBridge uarch results, right? And that would not be bad at all.

Uhm, no, not yet, as SB is 6-issue. https://en.wikichip.org/wiki/intel/microarchitectures/sandy_bridge_(client)

Yeah, but it was really bad at it. 🙂 Haswell, that’s the core to aim for.

So many exagerations coming out of SiFive. 2x compute density – I don’t think so. How about providing the details – were cache sizes equal between the core compared? Were the cores simialrly configured? Heck, were they even implemented in the same process? I’ve seen you do it before – tauting better compute density running Drystone. Yet Dhrystone runs fully out of L1$ and you compared against a core with over 2x the L2$ – adding to the area but not DMIPs. Fool me once….

[ Yes, if they introduce a measure for integer benchmark per CPU area, shouldn’t they mention that number (mm2) for A76’s and P470’s/P670’s?

Approximately, a top-line HiSilicon Kirin 990 SoC (2xA76_HP, 2xA76_MP, 4xA55, GPU, NPU, Caches (L1d_L1i_L2) 4x64_4x64_4x512(k)/4x32_4x32_4x128(k), peripherals IO) is ~113mm2

just seen: it’s about A78, so it would need to ~compare to a e.g. Snapdragon 888 ]

[ Dhrystone/area, seems being an introduced measure

‘https://community.arm.com/resized-image/__size/1040×0/__key/communityserver-blogs-components-weblogfiles/00-00-00-21-42/A78-blog-image4.JPG’

A Snapdragon 888 (8cx platform) SoC ~112mm2 ]