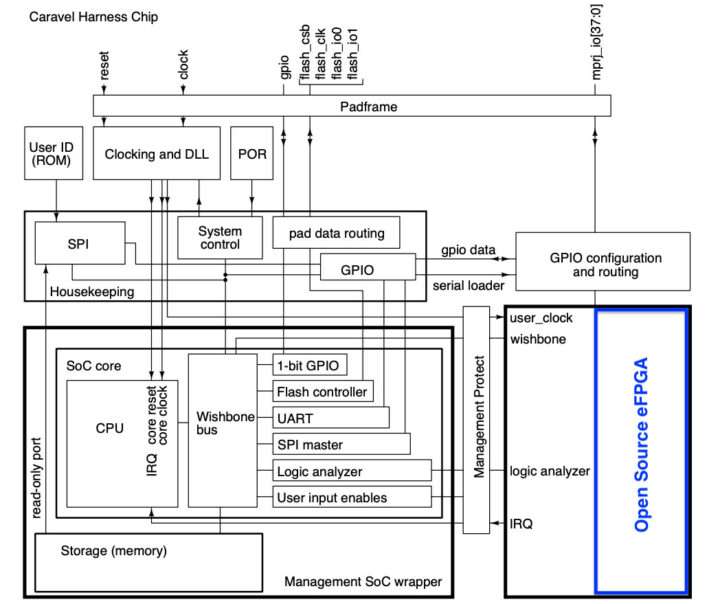

Open-source SoC designs are available to run on FPGA hardware, but few make it to silicon due to the costs involved. That’s why a couple of years ago the Google SkyWater PDK (process design kit) was released together with an offer to manufacture up to 100 pieces for free to selected designs in collaboration with Efabless.

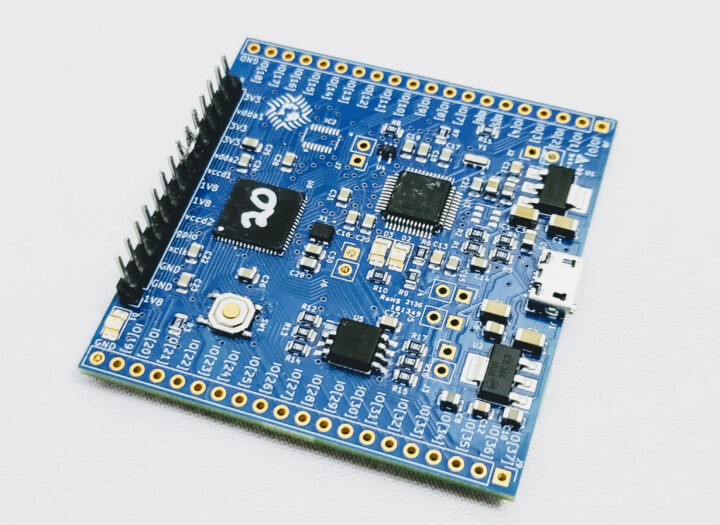

Efabless chipIgnite is an evolution of that offer with $9,750 being enough funds to manufacture 100 QFN or 300 WCSP parts, or alternatively 1,000 parts for $20 each ($20,000). Based on the company’s Caravel template SoC and the openFPGA generator framework, CLEAR open-source FPGA ASIC design is meant to promote and demonstrate the chipIgnite “paid IC creation” solution. You can participate by joining a group buying campaign on GroupGets to get a development board based on CLEAR for $74.99 plus shipping.

CLEAR open-source FPGA ASIC features:

- FPGA – Small 8×8 (64) CLB eFPGA

- CPU – VexRISCV-based CPU

- Memory – 3 kilobytes of on-chip RAM (2 kB of OpenRAM and 1 kB of DFFRAM)

- Storage – external QSPI flash

- Peripherals – SPI master, UART, 39x software configurable GPIO, Counter/Timers, Logic Analyzer

- Misc – Programmable internal clock frequency

Efabless will provide information to reproduce the workflow for all steps of development:

- Generate an embedded FPGA macro based on the OpenFPGA generator framework

- Integrate the eFPGA macro into Caravel which makes it an FPGA ASIC – Clear

- Manufacture the ASIC through chipIgnite program through SkyWater Technology

- Package and mount the ASIC on its development board

- Test the boards with the open-source FPGA programming software

The goal is here is to show how it can be done, and help people get started with their own custom ASIC without spending a large amount of money for design and manufacturing. The first prototypes are already working as shown by the simple demo below.

The group buying campaign is open until April 29, 2022, with the goal of selling at least 200 boards. As I understand it, delivery is scheduled for September, but the exact time depends on the successful launch of the April chipIgnite shuttle (2204C) which requires a minimum number of projects (there are 40 slots available for projects).

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I don’t get it – it is a chip fabrication project AND an FPGA?

I understand Efabless designed an SoC with a built-in FPGA, and they are manufacturing it too.

Neither do I. !

The Efabless chipIgnite solution enables anyone to design and prototype their own custom chip using a fully open-source RISC-V SoC design template. CLEAR is an example of a chip using that solution and implements an eFPGA as part of the SoC. The board lets someone try out the SoC as part of the template which they can customize for their own design.

eFabless failed to get funding, and has now shut down operations:

https://x.com/chr1sa/status/1895659001188401474

And short official announcement:

https://efabless.com/notice