Renesas has just unveiled the ForgeFPGA family of low-cost low-power FPGA’s to go for under 50 cents in (large) volumes following their acquisition of Dialog Semiconductors last August, who previously designed the GreenPAK programmable mixed-signal matrix.

The company says its FPGAs consume half the power of competing FPGAs with a standby current of under 20uA, the price point will enable the use of FPGA in new markets and IoT products, and the tools will be free, at least as in beer, without any license to acquire or install.

The full specifications are not available yet, but the ForgeFPGA Family will come with a maximum of 5,000 gates of logic, and the first devices ship with 1K and 2K Look Up Tables (LUTs), and as just mentioned, will operate at ultra-low power as low as 20 microamps in standby. ForgeFPGA is expected to target the same market as GreenPAK notably embedded sensors and IoT devices.

Contrary to most other FPGA vendors, the Renesas development tools will be completely free, and without the hassle of having to install license keys. The “Go Configure Software Hub” will allow engineers to work on FPGA design depending on the experience levels with two modes of development that can be switched on the flu while the software is running:

- “HDL Mode” for experienced FPGA

- “Macro-cell Mode” uses schematic-capture-based development flow

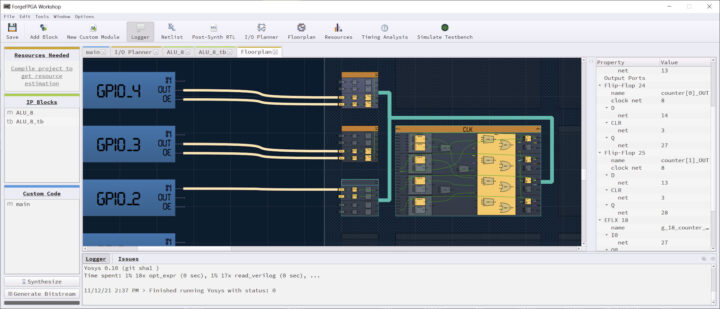

The software hub can be used to launch GreenPAK Designer and ForgeFPGA Workshop programs, with the latter – as the screenshot below shows – appearing to rely on Yosys open synthesis suite whose code is available on Github.

You can even try the beta now, after registration, with the software running on Windows 7/8.1/10 32-/64-bit, macOS v10.13 or higher, Ubuntu 18.04/20.04 64-bit, and Debian 10/11/Testing 32-/64-bit. You don’t need a powerhouse to develop software for such low-end FPGA either as the minimum hardware requirements include a 2,500 MHz processor, at least 512MB RAM, 128MB graphics RAM, and 750MB of free hard disk space. Note the download link will be provided immediately, so you don’t need to share a working email.

I had to install it as follows since some packages were missing from my Ubuntu 20.04 system:

|

1 2 |

sudo dpkg -i Go_Configure_Software_Hub_v6.27.001_Ubuntu-18.04_amd64_Setup.deb sudo apt --fix-missing install |

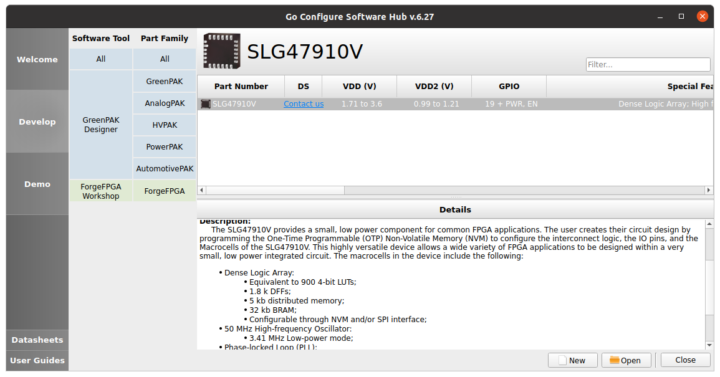

The good thing is that we can find some details about the first ForgeFPGA part in the software with Renesas SLG47910V FPGA to launch with the following specifications:

- Dense Logic Array

- Equivalent to 900 4-bit LUTs

- 1.8 k DFFs

- 5 kb distributed memory

- 32 kb BRAM

- Configurable through NVM and/or SPI interface

- 50 MHz High-frequency Oscillator

- 3.41 MHz Low-power mode

- Phase-locked Loop (PLL) – Input from external source or internal oscillators;

- Power Supply

- VDDIO: 1.71 V to 3.6 V;

- VDDCore: 1.1 V ± 10%;

- Power-On-Reset (POR)

I can remember I used a CLPD in a product many years ago to emulate a CF card reader, that was programmed with VHDL, so I suppose this FPGA family targets similar applications but its internal structure is different and should offer more flexibility.

Renesas says the ForgeFPGA FPGA engineering samples are available now together with a prototype development kit, probably only available to partners at this stage. The 1K LUT device, which should be the SLG47910V model described above, is expected to be in mass production in Q2 2022. You may find a few more details in the press release, and the product page.

Thanks to TLS for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

One thing I don’t quite get is why make own Yosys-based software, which is ISC-licensed, instead of contibuting directly to Yosys with patches for this new product series?

Might just be a matter of timing and privacy. They might not have wanted news of the parts to release through the code they’re committing. At least I would *hope* that is it and that they upstream their code.

You don’t really need to commit code before you announce, e.g. Quicklogic just dropped a support library for Yosys, which then got integrated. I do really hope that they will upstream properly, but the first steps don’t seem to show any intent to do so.

Knowing Renesas, there is too little chance, that this chip will not become exclusive for one manufacturer, like Apple. I would stay away from this “offer”.

What do you base this on?

These ForgeFPGA parts are dirt-cheap, very low power, and (obviously) highly customizable, making them ideal for targeted end-user inclusion in densely-packed high-volume products such as cell phones. In-fact UK-based Dialog-Semiconductor (purchased by Renesas-Japan in September 2021 [1]) pitches the ForgeFPGA as follows: “Allows for using FPGAs in high-volume consumer applications previously inaccessible to FPGAs due to cost.”[2] I can see Dialog targeting Apple with ForgeFPGA. Since 2007, Dialog Semiconductor has been the exclusive supplier of power management integrated circuits (PMICs) for the Apple iPhone, iPad, and Watch. Apple comprised 74% of Dialog’s sales in 2016.[3] So Dialog’s PMICs are firmly rooted in Apple’s products, why not Dialog’s ForgeFPGA as glue-logic and bridges too?

Given this likely ForgeFPGA market profile and the history of both Renesas and Dialog-Semiconductor exhibiting a lack of interest in anything except high volume customers, there is a good chance it’s going to be difficult for us low-volume peeps to get our hands on the ForgeFPGA parts, that is unless someone wants to arrange a 10,000 piece group-buy.

But you never know… Maybe the ForgeFPGA parts will eventually show up on the likes of Digi-Key and/or Mouser in small prototype-friendly quantities. If that happens, it will only be a matter of time before someone releases an open ForgeFPGA breakout/dev-board that the Chinese will immediately copy and sell for peanuts. Then we might finally get something like an Arduino Uno, but with an FPGA instead of a Microcontroller as the star of the show. Of-course the key to that happening requires a free, uncrippled toolchain that isn’t a hassle to use and isn’t cloud dependant. Hints of the Yosys Open SYnthesis Suite being part of the toolchain bodes well. Finally, don’t hold your breath for “sub 50 Cent” prices in small volumes; prolly like a couple-few bucks per part, but that’s still OK.

Dialog/Renesas has a real opportunity here to make the ForgeFPGA line into a community-supported product. There’s great value in that for them. Let’s hope the Marketing/MBA bobble-heads understand and take advantage of that.

Digi-Key has been distributing Renesas products for a long time, but a lot of times availability is spotty.

IIRC, Dialog sold their PMIC business to Apple (basically forced to).

@TonyT said: “Dialog sold their PMIC business to Apple”. I did know that, thanks.

Sorry, I feel like I need to clear the air. These Renesas devices, which everyone seems to want (include Renesas themselves) to identify as Dialog devices, are actually from a prior acquisition of Dialog’s, Silego. I have some of their GreenPAK devices, purchased back when they were independent. They’re pretty neat, but I could never find a killer use for them. If this ForgeFPGA is cheap, actually available to design engineers to play with, and if Renesas commits to upstreaming support to Yosys, they’ll definitely have a winner because of the greater versatility those extra LUTs give you.

I always avoided Xilinx, Altera, Lattice and Atmel, because their software either wouldn’t work with my system *or* the software wasn’t free.

“Purchase our products … In order to get our products – which you already own – to work, you have to pay extra.”

Renesas / Dialog did the right thing here. Making a Linux release is a great step forward, but I do wish they would make the source open (so it could run on whichever CPU architecture you like the most).

50MHz might not be extremely fast, but it’s definitely usable for very many applications.

I do wish for something like a 200 MHz or even 500 MHz FPGA with free (or open-source) software – maybe that’s just a matter of time now.

The device description in “Go Configure Software Hub” is exactly as reported here. However, we have different values in other places: The description of the “FPGA Core” block in ForgeFPGA Workshop claims that each CLB (Configurable Logic Block) has 2x LUT5 (which can be combined to one LUT6 with two outputs) and 2 registers. The “Resources needed” in the FPGA Editor says “CLB LUTs: 28/1120; CLB FFs: 16/1120” for the example project. Other vendors also have creative ways of counting LUTs so I already expected that the device doesn’t actually have 900 real LUTs. I’m a bit surprised that it might have more. In addition, I can’t explain the difference in register count.

Regarding Yosys: The README next to yosys.exe says “This is Yosys 0.9 for Win32.” and the build script uses

synth_xilinx -flatten -nodsp. The share folder contains files for gowin, efinix and ice40. This might be upstream yosys with little or no changes. The changes for this FPGA might be in later steps only.There is an eda-placer directory next to yosys (under “external”). I can’t find any tool with that name. Do you have any ideas?

The IO mapping file mentions EFLX_IOB, which I find in some PDFs from flex-logic.com and indeed, they claim that the Renesas/Dialog/Silego chip contains their eFPGA.

This PDF says that their “Gen 2” architecture has 2x LUT5 / LUT6 (which would match the description of the FPGA Core) but we don’t know (yet) whether these chips use that architecture: https://flex-logix.com/wp-content/uploads/2019/04/EFLX-as-an-Accelerator-on-AHB_AXI-Bus-072817-v1p6.pdf

This only mentions Yosys, next to unnamed tools for the other steps (place&route, timing, …) so I fear this might be in-house tools that are not open-source: https://flex-logix.com/wp-content/uploads/2019/10/2019-11-EFLX-eFPGA-Software-Development-Manager.pdf

The GreenPak tools use ngspice for their simulations so using open-source tools is nothing new for the Silego engineers. Unfortunately, I don’t think they have upstreamed their plugins for the devices. This might be due to trade secrets but many of the details (e.g. bit layout of the “bitstream”) are in the datasheets anyway. They don’t stop you from using their plugins with upstream ngspice but this is very much not supported, of course.

In short: It looks like ForgeFPGA is based on an FPGA core that is very similar to this one with 560 logic tiles: https://flex-logix.com/wp-content/uploads/2020/09/2020-09-EFLX-1K-TSMC-40ULP40LP-AVAILABLE-product-brief.pdf