Intel’s first foray into hybrid processors using Foveros 3D stacking technology did not end well with the company just announcing the end of the life for Lakefield hybrid processors. But the company is not giving up on hybrid technology, and a recent leak shows the Intel Alder Lake family comprised of more powerful mobile hybrid processors will be offered for a wide range of applications from tablets with 5-7W M5 processors and up to “muscle laptops” or mobile workstations (MWS) with H55 processor at 45-55W TDP.

Alder Lake hybrid processors will be comprised of high-performance CPU “Golden Cove” cores and energy-efficient Atom-based “Gracemont” CPU cores, in a way that’s similar to Arm’s Cortex-A7x big cores and Cortex-A5x LITTLE cores with big.LITTLE or DynamIQ processing with the goal of optimizing power consumption.

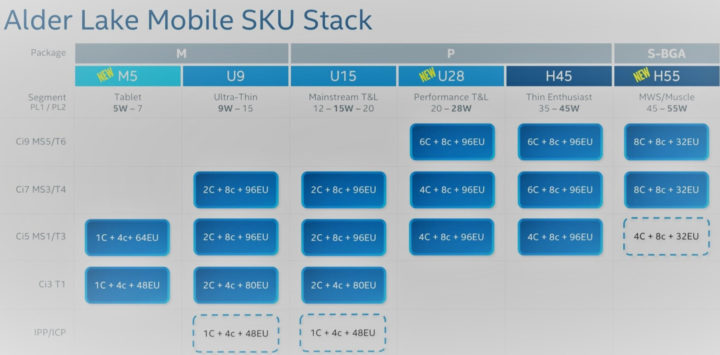

The Intel Alder Lake Mobile SKU stack includes processors for 6 market segments including three “new” segments/TDP ranges according to the slide:

- Alder Lake-M family

- Intel M5 (New) – 5W-7W Core i3/i7 processors for tablets with one big core, four small cores, and 48 or 64 EU graphics

- Intel U9 – 9W- 15W Core i3/i5/i7 processors for ultra-thin laptops with two big cores, four or eight small cores, and 80 or 96 EU graphics. Not quite sure what the dotted lines mean, but the table also shows an additional 1 big + 4 small + 48EU graphics Celeron/Pentium processor

- Alder Lake-P family

- Intel U15 – 12W/15W/20W Core i3/i5/i7 processors for mainstream laptops and tablets with the same configuration as U9, but likely higher clock speeds

- Intel U28 (New) – 20W-28W Core-i5/i7/i9 SoCs for “performance” laptops and tablets in either 4 big + 8 small or 6 big + 8 small configuration with all equipped with 96EU graphics

- Intel H45 – 35W–45W Core i5/i7/i9 chips for “thin enthusiast” laptops using either 4 big + 8 small or 6 big + 8 small cluster configurations, and again 96EU graphics

- Alder Lake-S family (socketed BGA1964 package)

- Intel H55 (New) – 45W-55W Core i7/i9 processors for “muscle” laptops and MWS with eight big cores, eight small cores, but only 32EU graphics, possibly because a discrete card might also be used. A dotted box also shows a Core-i5 model with four big and 8 small cores.

Intel Alder Lake hybrid mobile processors are expected to become available later this year.

Via HXL (Twitter), Liliputing & TechPowerUp

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Wondering what the reason for more than 4 small Gracemont cores could be…

Power efficiency in the case of U9 and U15, raw performance for U28 and up, but with better efficiency than if there were 10-12 big cores.

For a 1+4, 2+4, or 2+8, the Gracemont cores should be running most of the time, but anything that needs to be completed rapidly can use the big core(s). Performance should be much better than a quad-core Atom as long as it is handled better than Lakefield was at launch. A tablet or laptop could turn off the big cores if battery levels are low.

For an 8+8, you could use the 8 big cores for gaming and the 8 small cores for background tasks, streaming software, etc.

Intel will only double down on this approach. They’re rumored to use up to 8 big, 16 small cores for the successor “Raptor Lake”. Since the smaller cores have a performance per area and efficiency advantage, you can expect to see the number of small cores rise faster than the big cores.

> Intel will only double down on this approach. They’re rumored to use up to 8 big, 16 small cores for the successor “Raptor Lake”. Since the smaller cores have a performance per area and efficiency advantage, you can expect to see the number of small cores rise faster than the big cores.

This is becoming absurd. As soon as one small core is saturated you regret not having a larger one because you’re waiting for something to complete. And if it’s not saturated, you don’t need more cores because the other tasks can run fine on it as well using even less energy. There’s been a lot of marketing likes recently from chip makers to justify the large number of cores by “background apps”, but no single low-performance application needs its own core, this is the system’s scheduler job to run them at the right moment.

Tkaiser is right, there’s no use to this large number of small cores. This stupid design already plagues the RK3399. When you have many things to do, you’re constantly waiting, typically with 2 big and 2 little running, and 2 other little ones constantly idling. And sometimes it’s faster to simply disable the small cores so that they don’t grab a task and take too long to complete it. At least it was well understood by amlogic when they did their S922 which features 4 large ones and two small ones. *This* approach makes sense to me.

The proof will be in the third-party benchmarks, as always. Just know that Intel can put around 4 small cores on the die instead of 1 big core.

By manually disabling cores, reviewers could compare 8+0 to 6+8. The 8 small cores would be around the same die space as 2 big cores. That comparison should clue you in to whether this makes sense or not. Another good one would be 2+0 vs. 1+4. That already happened with Lakefield but Intel will get another shot at it with newer designs for both the big and small cores.

> The proof will be in the third-party benchmarks

Vast majority of benchmarks consumers look at are pure BS, especially when taken the use case these SoCs are meant for into account. Consumers are trained to look at irrelevant numbers (e.g. multicore results) so I guess you’re right and the whole ‘little core count’ thing is about marketing only.

> As soon as one small core is saturated you regret not having a larger one because you’re waiting for something to complete.

There’s more to this if we have the use case of these things in mind (high performance and long battery life): even an energy aware scheduler is not enough if it’s about saving power. For example keeping the whole storage subsystem active (little cores busy doing things) might end up with higher consumption compared to the big cores playing ‘race to idle’ for a short time allowing everything storage to be sent to deep sleep for most of the time.

This slide has been floating around since at least March. Here it is on Wccftech on Mar. 7: wccftech.com/intel-12th-gen-core-alder-lake-mobile-lineup-detailed-up-to-8-big-cores-8-small-cores-55w-tdp/

This was the one that clued people in to full 8+8 coming to mobile, not just the 6+8 of H45 which was known for a while before that.