In Arm’s world, heterogeneous processors are pretty common, with for example big.LITTLE / dynamIQ application processors mixing powerful Cortex-A7x cores with power-efficient Cortex-A5x cores., or “industrial” processor such NXP i.MX 8M family with Cortex-A53 application cores combined with Cortex-M4F real-time core.

Maybe I did not follow enough, but I hadn’t really seen anything equivalent in MIPS world, except if we count Ingenic T31 with RISC-V and MIPS cores. That is until today where I was informed about documents related to Ingenic X2000 IoT application processor with two 32-bit MIPS Xburst 2 core, one MIPS Xburst 0 real-time cores, as well as up to 256MB RAM built-into the SoC.

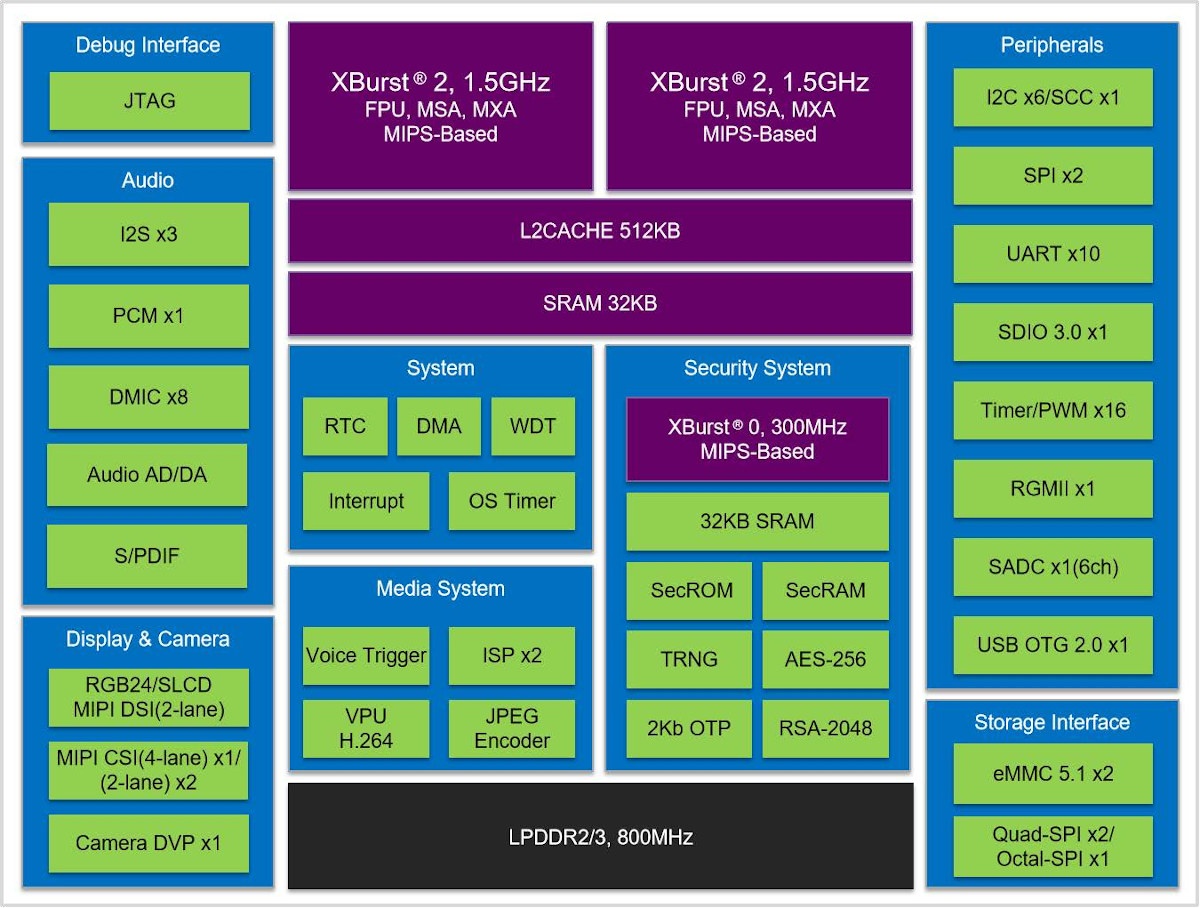

Ingenic X2000 specifications:

- CPU Core – Dual XBurst 2, MIPS ISA based, frequency up to 1.5 GHz with 32KB L1 x2 Cache, 512KB L2 Cache, 32KB SRAM, FPU,128bit SIMD

- MCU Core – XBurst 0 MIPS core @ 300MHz for security and real-time control

- System Memory -128/256MB LPDDR2/3 in package

- Storage I/F

- SPI Flash Controller supporting Quad & Octal SPI

- 2x MMC/SD/SDIO

- Display Interfaces

- MIPI-DSI up to 1920×1080 @ 40Hz

- SLCD up to 640×480 @ 60Hz, 24BPP

- RGB up to 1280×720 @ 60Hz, 24BPP

- Video Processing Unit (VPU)

- H.264 encoder/decoder up 1920x1080p30

- JPEG encoder/decoder up to 70Mega-pixels/s

- Camera Subsystem

- Image Signal Processor

- 8-bit/10-bit/12-bit YUV422 DVP interface up to 1280×720 @ 30 fps

- 4-lane or 2x 2-lane MIPI CSI interface up to 1080p120

- Supports synchronization of dual-camera sensor

- Audio Processor

- Digital Microphone Array Controller supporting 8 mic channels with

voice triggering - 3x I2S, PCM interface, S/PDIF

- Digital Microphone Array Controller supporting 8 mic channels with

- Networking – Gigabit Media Access Controller, in compliance with IEEE 1588-2002

- USB – 1x USB 2.0 OTG

- Security – True Random Number Generator and AES-256/RSA-2048/MD5/SHA/SHA2 part of MCU core sub-system

- Other Peripherals

- 16x PWM

- Interrupt controller supporting 64 sources

- Watchdog, Real-time clock

- 6-channel 10-bit A/D converter

- GPIO

- 6x I2C, 2x Synchronous serial interfaces (SSI)

- 10x UART

- Power Consumption – 300mW typ.

- Package – BGA270 – 12 x 12 x 1.2mm, 0.65mm Pitch

- Process – 28nm

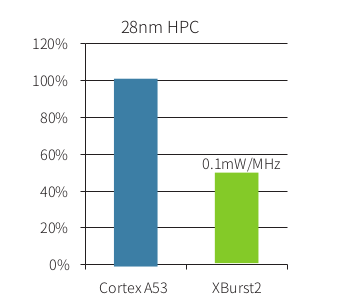

Ingenic X2000 also happens to be the very first processor with XBurst 2 cores, a core that was announced many years ago as a MIPS64 (64-bit MIPS core), but finally, the company decided to completely change the design with MIPS32 ISA R5. Ingenic claims Xbust2 is twice as power-efficient as Arm Cortex-A53 core with the same 28nm process.

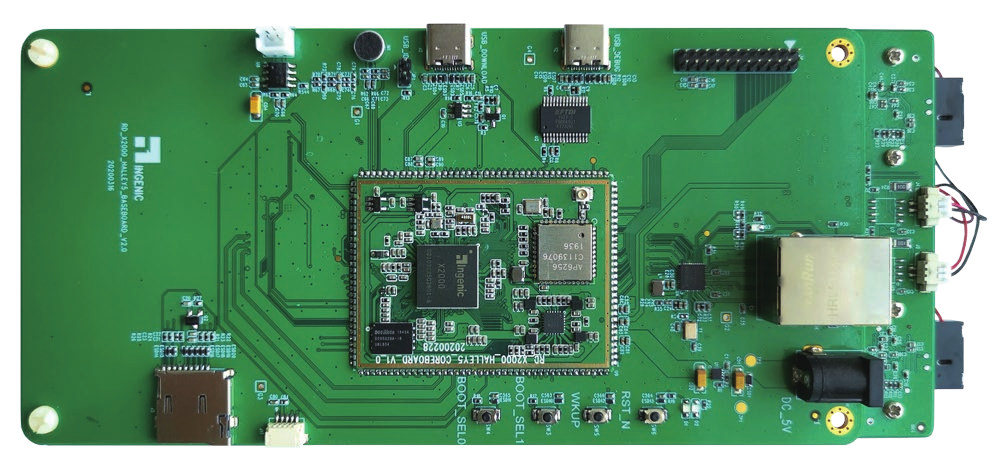

The company can provide a complete software and hardware development kit with a Linux 4.4 BSP and Halley5 development board with an X2000 SoM with a wireless module fitted to a largish carrier board with Ethernet, USB, microphone, MicroSD card slot, I/O header, buttons and so on. The other side of the board is equipped with a dual-camera board and a Full HD AMOLED display.

Last April, we asked whether MIPS was dead, at least outside of China with Linux kernel maintainers leaving, a lawsuit, and bankruptcy. We however still noted some MIPS related changes in Linux 5.7 last month, but with a very minimal changelog. So that should mean you’d have to rely on Ingenic BSP, and IMHO mainline support is very unlikely.

There’s no product page on Ingenic website, but we have something even better in their FTP server with the SoC and board product briefs and a datasheet in English and /or Chinese.

Thanks to Alex for the tip.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

In western ARM SoCs you often find a Cortex M? doing power management or something but in Chinese SoCs it seems to be all over the place: 8051, OpenRISC, apparently RISCV now too… I think some of the TV/STB ARM SoCs even have ARM cores for running the main OS, MIPS for the TV parts, an 8051 for IR decoding and then OpenRISC for power management.

Why not, if licensing doesn’t make a homogeneous choice of cores cheaper. GCC is available for about everything just 8051 can be a pain…

What are the MXA and MSA extensions to the CPU?

simd extension

after their fail with Creator Ci20, sorry, but no!

I hope they launch a version with a GPU on it so the chinese handhelds can have a upgrade

And not a single “modern” device interface…

I guess this is what you call DOA.

This SOC is for making embedded devices, not a desktop. It is meant to make things like an Echo or Echo Show. The peripherals are fine for that purpose.

The key thing here is price. I’ve sent email to them asking for prices, hopefully I will get something tomorrow. If they are below $5 for the 256K RAM version this chip should do well. If it is $4 or less it will do great. $6 or $7 and it will likely fail.

One dollar make that much difference?

$1 makes a huge difference if the chip is going into a product that sells for $20.

For example this $20 camera is based on a different Ingenics chip.

https://wyze.com/wyze-cam.html

Just to be picky, do you mean “below $5 for the 256MB RAM version”?

Please let us know if you do get pricing back from them.

I think making it below $5 for the 256MB version would be very impressive, given that the memory chip in a standalone package (LP-DDR2, 128Mx16) already costs a few cents more than that on mouser.com, 2.6x as much as the memory in the T20 based camera you mention below (DDR2, 32Mx16).

As far as I can tell, they don’t just go for the super-cheap market with this one, but target those users that need both higher performance and efficiency than they can offer on the low end. Using DDR3 instead of LP-DDR2/3 would have been significantly cheaper, so going with low-power memory must have been intentional.

For comparison, Microchip currently lists their (more versatile, but probably slower and less efficient) SAMA5D27 for $5.89 without memory, $8.73 with 64MB DDR2 SiP, and $12.82 with 256MB LP-DDR2.

Memory dies are far cheaper than memory inside a package. The Allwinner S3 has 128MB embedded DDR3 and it is currently selling for under $3.50 in quantity. Olimex is going to ship an S3 board in the near future.

https://www.cnx-software.com/2018/03/30/allwinner-s3-camera-soc-includes-128mb-ram-an-i2s-audio-interface/

Ingenic sent some emails overnight which avoided providing a price. The chip has just started sampling. I’m not sure if they have firm pricing yet. Their T30 is sub-$3.

I doubt those dies have to be A-grade silicon, as latency and clock requirements are not the highest in this field. So most likely not DDR7-9999999 CL2

I wouldn’t be surprised if embedding a DRAM die allows to further cut costs. For example one part that counts (price and access time) are the external drivers required to push the data onto long copper lanes. Once inside a chip with only 3mm long wire bonds you can get rid of this, save size, power and nanoseconds, thus allowing to reach higher speeds from lower grade chips.

They’d have to get specialty LP-DDR2 dies for little more than the cost of mainstream DDR3 dies of the same capacity though, which is the part I’m skeptical about.

A <$3 T30 that includes a $1.90 (retail) memory chip, or a $3.50 S3 that includes a $2.30 memory chip do not surprise me at all, and they could probably each double the RAM for another $0.50.

I’ll tell you the X2000 price as soon as I can get it out of them. And for sure this will be a China manufactured DRAM die. Who makes IMF64M32E3D1CSR-18? It is a 2Gb LPDDR2 for $1.29 on the spot market.

Ah, I hadn’t realized there even still was a spot market for LP-DDR2, the places I looked before seemed to only have LP-DDR3/4 and the standard DDR/DDR2/3/4. I found it now and see that it’s these parts are in fact slightly cheaper than LP-DDR3 there (though of course more expensive than regular DDR2/3).

No idea about that IMF64M32E3D1CSR part, my first thought was it might be an unusual number for a Micron chip from the “IMFT” days, but that seems unlikely as IMFT only produced flash chips, not DRAM.

Also note that Mouser is not a cheap place to buy chips. Various 2Gb DDR3 chips can be purchased in Shenzhen for under $1. Winbond W632GU6NB-12TR at Digikey is $2.32, same chip China sourced is $1.14 (8Y). And those are packaged chips at retail. The internal dies are probably below $0.50 depending on if they are tested or untested.

itchy is correct that they don’t use super high performance DRAM when it is embedded with the SOC.

>$8.73 with 64MB DDR2 SiP

hisilicon have a Cortex A7 + 64MB chip that could potentially be just over $1 when bought in quantity (based on being able to get it for ~$1.5 in singles).

Sigmastar has Cortex A7 + 64MB chip for a bit more (~$1.8 at low quantity with shenzhen broker overhead). There’s apparently a dual A7 + 128MB version for a dollar and a bit more.

The Ingenic SOC is interesting because it has SIMD extensions to the instruction set to implement neural networks. I have not tried this chip, but comparing to the Allwinner V5, the V5 can do neural nets in real-time at 30FPS. Running the same net on Cortex A7 take over 5 seconds. This dual core MIPS design probably 10x faster than A7 for general computing.

Also I have been informed that the Allwinner V831/3 is identical to the V3 except for the addition of a 0.5TOPS AI unit. It is the same die slightly modified to squeeze in the AI unit.