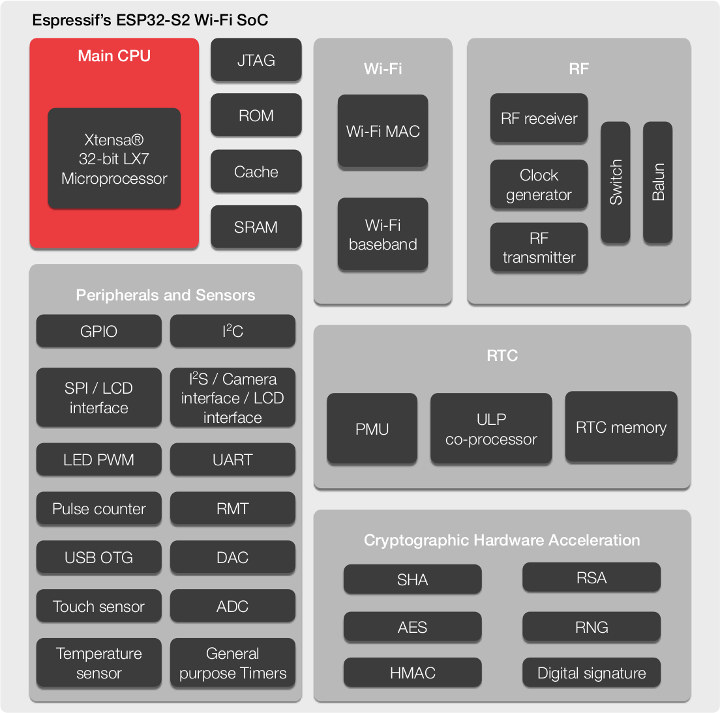

Last may Espressif Systems unveiled ESP32-S2 secure WiFi processor with a single Xtensa LX7 core clocked at 240 MHz, and the first ESP32 processor to come with a built-in USB (OTG) interface, as well as some new features such as WiFi Time-of-Flight (ToF), hardware security, LCD RGB & camera interfaces, and more. Note that contrary to other ESP32 processors launched so far, ESP32-S2 does not support Bluetooth.

ESP32-S2 Datasheet

The processor is still not available, but there has been some interesting development in recent weeks. First the datasheet (PDF) has been released, so we’ve got to check more technical details including the processor diagram below.

The main specifications have not changed, so I won’t reproduce them here, and you can check out ESP32-S2 announcement for specs.

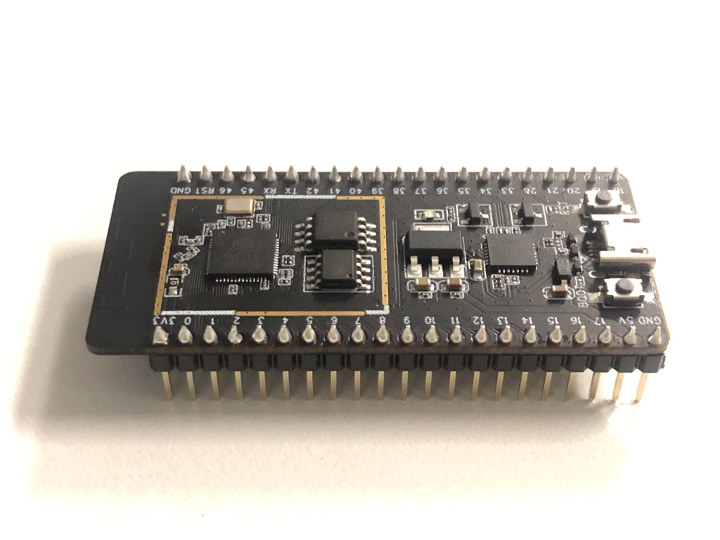

ESP32-S2 Development Boards

The first ESP32-S2 development boards are also available… in Espressif Systems’ offices that is, but not quite publicly.

The board above is based on ESP32-S2 processor with a 56-pin package, and one oddity is the USB to TTL chip. One commenter in Twitter explains that’s because USB is still being worked on for ESP32-S2, so they have to use an external chip for now, which may not be there in the final hardware, or maybe they want to reserve the USB interface for other purposes. There are two 21-pin I/O headers for expansion, but apart from the power signal and reset pins, the only photo available does not reveal which pins are routed. There also seems to be both SPI flash and SPI RAM on the board.

If you have no time for “tinkering”, and want to do some more serious development, Espressif Systems has a full-featured ESP32-S2 evaluation kit with touch buttons and audio (mic) expansion boards.

There’s still no reference to ESP32-S2 in ESP-IDF source code nor the documentation website, so it may take a while before the boards or a variants become available. The company recently sent ESP32-S2 processor samples to developers as they had 50 engineering samples for this purpose.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

Do we know much about the LX7 core they’re using? More generally, does anyone know much about the differences between the LX6 and 7? Since it’s a soft core, there’s not much useful info online that can be trusted–you have to know the settings they used when generating it.

You’ve probably looked at the datasheet already, but if not, here’s what’s inside about the LX7 core:

I remember reading something about FPU in LX7, but not sure whether that’s optional or not.

This is an interesting bit: • Unbuffered GPIO instructions

If memory serves, long latency of buffered-only GPIO was a major headache when developing software-only espusb, and that was also the reason for it to be limited to 1.5mbit/s (i.e. low-speed USB). Having unbuffered GPIO should speed up “turnaround” (i.e. reaction speed from input to output) quite a bit.

If you turn off the WiFi while you’re doing that, then it might show the benefits in real time processing that you expect. But, since this is a single core instead of a dual core processor, you can’t leave the other chip to handle the WiFi, BT, etc. tasks.

Judging by what Jean-Luc quoted above, and the official LX7 brochure, S2 seems like a ‘high-end’ variation of the LX7 base: https://ip.cadence.com/uploads/1099/TIP_PB_Xtensa_lx7_FINAL-pdf

I was pessimistic about the “secure” nature but according to the datasheet they have transparent encryption for the external memories including SRAM so you can actually use them without losing the whole point of signed firmware. They also seem to have something in their “digital signature” module that allows it to use a key that can’t be read out by the CPU. That seems to only be for MAC generation though. Would be nice if everything could be done with that key.

There was recent publication of bypasses for the security features on the ESP32, by LiveOverflow (IIRC), and others. Hopefully the new S2 hardware will have protection against glitching before it is released.

Was it related to this? https://www.esp32.com/viewtopic.php?t=12115

If so I think similar issues probably exist in all chips and at least it wasn’t something really stupid like a broken implementation of the crypto bits.

edit: A run down for anyone that’s interested – https://limitedresults.com/2019/09/pwn-the-esp32-secure-boot/

Not quite true

https://github.com/espressif/esp-idf/tree/feature/esp32s2beta