M.2 SSD’s are now pretty common and rely on either SATA or PCIe interface, but apparently there’s a new form factor with an M.4 SSD showcased at the recent Computex 2019 exhibition, and with Silicon Motion SM2270 controller leveraging a PCIe 3.0 x8 interface for up to 3,200 MB/s sustained sequential reads, 2,800 MB/s sustained sequential writes, as well as up to 800K/200K IOPS for respectively 4K read/write random operations.

Spotted by Anandtech at the event, Agylstor’s M.4 NVMe SSD come with the following specifications:

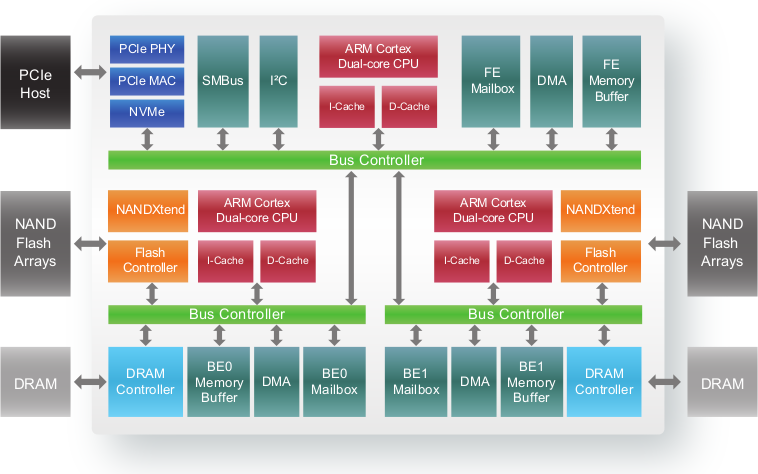

- Silicon Motion SM2270 controller with a three dual-core Arm Cortex-R5 processors with 2KB LDPC error correction and 16 NAND channels with 8 CE per channel (128 CE in total)

- Host Interface – PCIe Gen3 x8

- Command Protocol – NVMe 1.3

- Max Capacity – 16TB

Anandtech explains the M.4 SSD is essentially two M.2 SSDs glued together with (8) NAND packages on each side of the board. The company has now announced when we can expect the new drive to come to market, nor the target applications, but Agylstor’s website highlights the company provides storage solutions that aim at film & video production, energy monitoring, drones, and oil & gas exploration.

You’ll find a few more details about SM2270 controller in the product brief. It will probably take a while before we regularly start seeing M.4 sockets in single board computers or other embedded hardware platforms.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

That’s confusing. It’s got 8x PCIe 3.0 lines, but it performs like a 4x PCIe 3.0 device. What’s the point of the extra lanes if you’re not able to make use of them?

Why go to 8x instead of going to PCI3 4.0 and keeping the same lanes/form factor.

If you want to use 8x lanes, why not go with a normal AIC form factor instead of the hard-to-fit-on-a-board M.2 size (or this M.4 monster)?

Lol maybe its for atom cpus with a 8x pcie 2.0 slot of which 2 lanes are populated…

The SiliconMotion product brief where these performance numbers are obviously copied from reads ‘Performance (U.2)’ and U.2 is PCIe Gen3 x4.

True, that just leads to more confusion as to why they would spec those performance numbers, then. If it can support 8x 3.0, why only show numbers for 4x 3.0 when making an 8x PCI-E variant of it for testing would be easy.

> why they would spec those performance numbers

We don’t know 🙂

Maybe it’s due to some regulations? Anyway: I miss a use case where it makes a difference whether 2, 3 or 5 GB per second can be written/read to/from flash storage. For my use cases low latency and high IOPS at low queue depth are more important. Naively I expect here a lot more from PCIe Gen4 with 16 GT/s per lane than a wider Gen3 implementation.

But I’m a hardware noob anyway and learned early that my naive thoughts usually are wrong. When I started with networking as an adolescent everything seemed to be like ‘water in pipes’ in the beginning (pressure and so on). Then I started to read Radia Perlman’s great books and realized that everything I thought was plain wrong (she’s still one of my personal superheroes).