In a surprise announcement last year, Wave Computing revealed their plans to open source MIPS architecture, and more specifically the new MIPS Release 6 architecture. The company has now started to deliver the goods with the release of the first MIPS Open Program components.

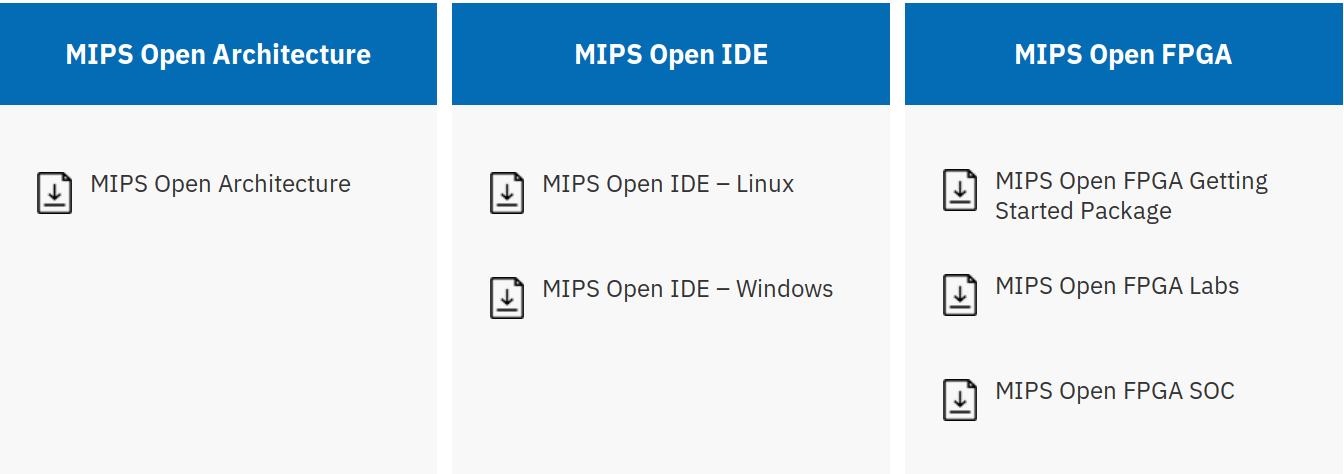

Specific components of the first release include:

- MIPS ISA – The latest R6 version of the MIPS 32-and-64-bit architecture, including extensions such as virtualization, multi-threading, SIMD, DSP and microMIPS code compression

- MIPS Open Tools – Integrated development environment for embedded real-time operating systems and Linux-based systems for embedded products that enable developers to build, debug and deploy applications on MIPS-based hardware and software platforms;

- MIPS Open Field Programmable Gate Arrays (FPGAs)– A complete training program for community members that includes:

- Getting Started Package – Provides the MIPS FPGA system as a set of Verilog files, plus an overview and instructions on how to use the MIPS FPGA system;

- Labs – Includes 25 hands-on labs that help developers explore the MIPS architecture and system-level designs;

- SoC Tutorials – Step-by-step direction on how to build a system-on-chip design based on the MIPS Open FPGA using an open source Linux operating system;

- RTL Code for the MIPS microAptiv core – Sample (non-commercial) code enables developers to explore microarchitecture features.

All resources can be downloaded on MIPS Open website after signing-up, accepting the license agreement, and waiting for approval within 3 working days.

The next release should include “commercial production verified microAptiv uC and uP Cores” with RTL code for the MIPS microAptiv cores as well as new features for the development environment. The company also plans to host MIPS Open Developer Days in the coming months.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

They no longer call it “open source”, because it’s not.

Also, I believe all the components that are made available for download were already available before, without having to accept an EULA.

It looks like the only thing that is really new are the specific license terms for getting the royalty-free MIPSr6 architecture license on https://www.mipsopen.com/resources/download/.

Were the microAptiv uC/uP available as royalty-free before?

As far as I can tell without signing up for an account, https://github.com/MIPSfpga is the same as what has been made available now, but under different royalty-free license terms. The promised “MIPS Open Cores” would be the same CPU cores again, and I have trouble understanding what the exact rights are that are going to be granted here.

Note that microAptiv is MIPSr3, not MIPSr6 (the two are incompatible), so it’s not covered under the MIPS Open architecture license, and their licensing terms for the core seem to be copy-pasted from the new architecture license but don’t actually grant any rights for the core. I assume the licensing terms will be corrected by the time the cores are available.

Good point about the microAptiv — so essentially there’re no r6 free cores at this point.

For reference, I’ve been given access to the “MIPS Open Architecture” files. It just took a few hours to get approved.

One more release part of MIPS Open: