When Linux 4.17 was released last June, we discovered an interesting new STM32 part: STM32MP157C dual core Cortex-A7 processor. It was the first time I saw an STM32 IC not based on Arm Cortex-M microcontroller core, but we knew only very little details at the time.

STMicro has now made it official, and introduced STM32MP1, the first STM32 MPU (Microprocessor Unit) that features one or two Arm Cortex-A7 cores running Linux, as well as an Arm Cortex-M4 real-time core that allows to re-use code from existing STM32 projects.

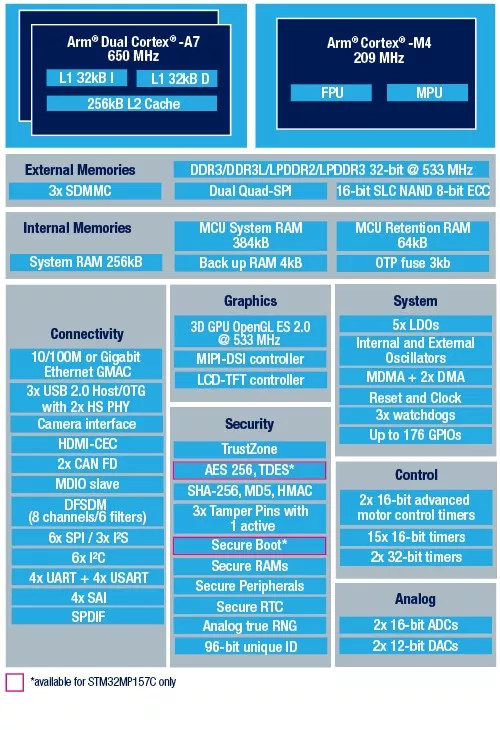

STM32MP1 key features and specifications:

STM32MP1 key features and specifications:

- Cores

- Single or Dual Cortex-A7 core(s) running at 650 MHz with 32-Kbyte L1 Instruction cache, 32-Kbyte L1 Data cache, 256-Kbyte Level 2 cache

- Cortex-M4 core running at 209 MHz with single-precision floating point unit (FPU), digital signal processor (DSP) instructions, and memory protection unit (MPU)

- GPU (STM32MP157 only) – Vivante 3D GPU with OpenGL ES 2.0 support; up to 26 Mtriangle/s, 133 Mpixel/s

- Memory

- External – Up to 1 GB LPDDR2/LPDDR3-1066 16/32-bit or DDR3/DDR3L-1066 16/32-bit

- Internal – 708 KB SRAM: 256 KB of AXI SYSRAM + 384 KB of AHB SRAM + 64 KB of AHB SRAM in backup domain and 4 KB of SRAM in backup domain

- Storage

- 3072-bit fuses including 96-bit unique ID, up to 1184-bit available for user

- Dual mode Quad-SPI memory interface

- Flexible external memory controller with up to 16-bit data bus: parallel interface to connect external ICs and SLC NAND memories with up to 8-bit ECC

- Display I/F

- LCD-TFT controller, up to 24-bit (RGB888), up to WXGA (1366 x 768) @ 60 fps, 2x layers with programmable colour LUT

- STM32MP157 only – 2-lane MIPI DSI up to 1 GHz each

- Networking – 10/100M or Gigabit Ethernet GMAC with IEEE 1588v2 hardware, MII/RMII/GMII/RGMII

- USB (Two options):

- 2x USB 2.0 high-speed Host, 1x USB 2.0 full-speed OTG OR

- 1x USB 2.0 high-speed Host, 1x USB 2.0 high-speed OTG

- Other Peripherals

- Up to 176x I/O ports with interrupt capability including up to 8x secure I/Os, up to 6x Wakeup, 3x Tamper, 1x Active-Tamper

- 3 DMA controllers to unload the CPU

- 6x I2C FM+ (1 Mbit/s, SMBus/PMBus)

- 4x UART + 4 × USART (12.5 Mbit/s, ISO7816 interface, LIN, IrDA, SPI slave)

- 6x SPI (50 Mbit/s, including 3 with full duplex I2S audio class accuracy via internal audio PLL or external clock)

- 4x SAI (stereo audio: I2S, PDM, SPDIF Tx)

- SPDIF Rx with 4 inputs

- HDMI-CEC interface

- MDIO Slave interface

- 3x SDMMC up to 8-bit (SD / e•MMC™ / SDIO)

- 2x CAN controllers supporting CAN FD protocol, out of which one supports time-triggered CAN (TTCAN)

- 8- to 14-bit camera interface up to 140 Mbyte/s

- Analog peripherals

- 2x ADCs with 16-bit max. resolution (12 bits 5 Msps, 14 bits 4.4 Msps, 16 bits 250 ksps)

- 1x temperature sensor

- 2x 12-bit D/A converters (1 MHz)

- 1x digital filters for sigma delta modulator (DFSDM) with 8 channels/6 filters

- Internal or external ADC/DAC reference VREF+

- Up to 29 timers and 3 watchdogs

- Debug mode

- Arm CoreSight trace and debug: SWD and JTAG interfaces

- 8-Kbyte embedded trace buffer

- Security/safety

- Secure boot, TrustZone peripherals, active tamper

- Cortex-M4 resources isolation

- Hardware crypto (AES, HASH), 2x TRNG, 2x CRC calculation units

- Power management

- 1.71 V to 3.6 V I/Os supply (5 V-tolerant I/Os)

- Internal temperature sensors

- Low-power modes: Sleep, Stop and Standby; total current consumption down to 6 μA

- LPDDR2/3 retention in Standby mode

- Controls for PMIC companion chip

- Clock management

- Internal oscillators: 64 MHz HSI oscillator, 4 MHz CSI oscillator, 32 kHz LSI oscillator

- External oscillators: 8-48 MHz HSE oscillator, 32.768 kHz LSE oscillator

- 6 × PLLs with fractional mode

- Packages – 10x10mm (TFBFA257), 12x12mm (TFPBGA361), 16x16mm (LFBGA354), 18x18mm (LFBGA448)

There are currently three pin-to-pin compatible product lines:

There are currently three pin-to-pin compatible product lines:

- STM32MP157 – Dual Cortex-A7 cores @ 650 MHz, Cortex-M4 core @ 209 MHz, 3D GPU, DSI display interface and CAN FD

- STM32MP153 – Dual Cortex-A7 cores @ 650 MHz, Cortex-M4 core @ 209 MHz and CAN FD

- STM32MP151 – Single Cortex-A7 core @ 650 MHz, Cortex-M4 core @ 209 MHz

The traditional STM32Cube firmware can still be used with the Cortex-M4 core in STM32MP1 MPUs, but the company is also offering OpenSTLinux distribution based on Trusted Firmware-A specifications, U-Boot bootloader, and the Linux Kernel 4.19 LTS. The Yocto Project is supported to create custom Linux system, and Android support is coming up a little later.

Engineers can re-use code made for their STM32 cortex-M4 design taking into account the MCU has access to 448 kB of RAM and that the boot and display systems are now handled by the Cortex-A7 core(s), so as long a the code is compact enough, the only changes needed are to the boot and display code.

The platform is highly flexible, as most peripherals listed above can be managed by either the Cortex-M4 or Cortex-A7 cores, as configured by the code at boot time. Some exceptions are the GPU and parallel display interfaces that are always attached to the Cortex A7 core(s).

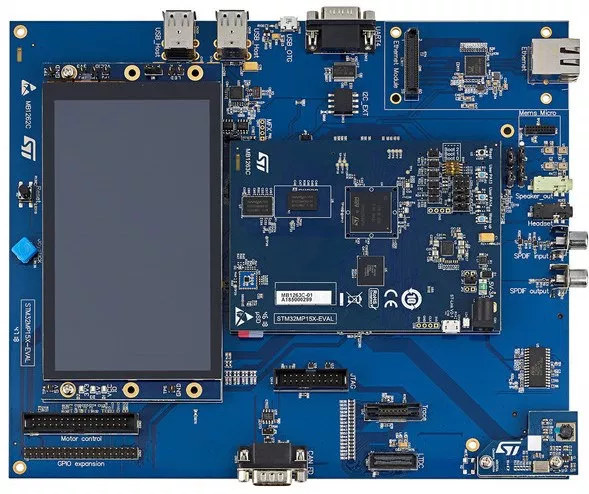

Two STM32MP157C based evaluation / development kits will be offered:

- STM32MP157C-DK1 ($69) / DK2 ($99) discovery kit with 512MB RAM, Gigabit Ethernet, a USB Type-C OTG connector, 4x USB host connectors, an HDMI transmitter, one stereo headset jack with analog microphone, one microSD connector, and expansion connectors for Arduino & Raspberry Pi shields. The DK2 version will add a 4″ LCD touchscreen display, and WiFi + Bluetooth LE connectivity

- STM32MP157A-EV1 / STM32MP157C-EV1 evaluation platform ($399) with 1GB RAM, 4 GB of storage, a 720p 5.7″ display, most of the features of the discovery kit (minus HDMI), plus CAN FD, 4x digital microphones, 4x SPDIF Rx/Tx, Smartcard, and eMMC, NOR and NAND Flash memories.

The boards are expected to become available in a few weeks, and some STM32MP1 SoM’s and a 96Boards hardware platform will be announced/showcased at Embedded World 2019.

I could not see pricing yet for the new STM32MP1 MPU. You can find more details on the product family page, as well as the evaluation kit and discovery kit pages.

Thanks to Dimitris for the tip

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I have high hopes for ST they’re serious and they spend resources to support their products. I can get even forgive them for the HAL API on the STM32 if they do this right.

Any ide about about network performance?

Looking at the STM32MP157C-DK1 PDF, the board has a lot of components for a $69 board.

Realtek RTL8211F Gigabit Ethernet controller, Cirrus Logic 42L51C audio codec, a STM32F103 Cortex M3 MCU, a Lattice/Silicon Labs HDMI transmitter, an SMSC/Microchip USB hub. The optional Wi-Fi module is from Murata. Not exactly cheap bits either.

https://www.st.com/resource/en/data_brief/stm32mp157a-dk1.pdf

That was my first thought when I saw the DK2 photo and the prices as well. They understood how a development kit can make products sell if it’s affordable. You don’t have to engage into an expensive project, you buy one for a test and it can lie a few weeks on your desk until you have time to play with it.

The pricing is available you have to expand the chip section and find correct chip.

Single Core ones are ~4.8$ probably @ 10000pcs

Dual core ones with GPU are ~10$ probably @ 10000pcs

Maybe this chip will be used on the next beaglebone 😉

Will this be the first affordable and properly documented soc on the market? Hopes are high…