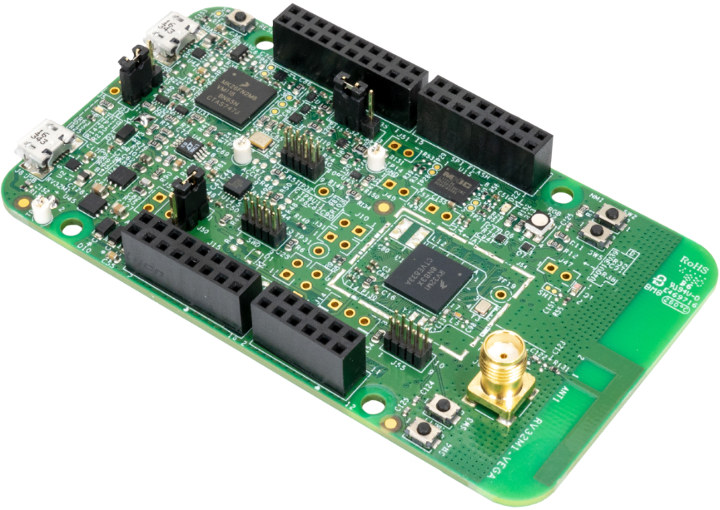

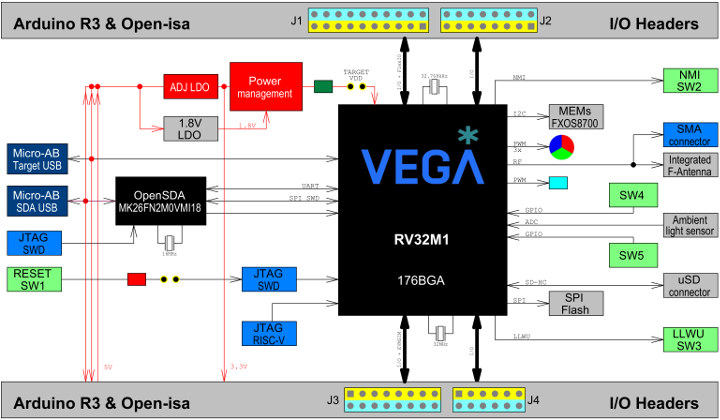

OpenISA has launched an Arduino compatible RISC-V development called VEGAboard that features RV32M1 wireless microcontroller with a RISC-V RI5CY core, a RISC-V ZERO-RISCY core as well as Arm Cortex-M4F and Cortex-M0 cores, and a radio operating in the 2.36 GHz to 2.48 GHz range. An external NXP Kinetis K26 Arm Cortex-M4 MCU is added to the board for OpenSDA (Open-Standard Serial and Debug Adapter) debugging over a single USB cable.

The board was offered for free, I’m just not sure when, but they are already out of stock. Hopefully, they’ll start selling the board soon enough.

VEGAboard (RM32M1-VEGA) board key features and specifications:

- Ultra-low-power RV32M1 Wireless MCU supporting BLE, Generic FSK, and IEEE Std 802.15.4 (Thread) platforms

- IEEE Std. 802.15.4-2006 compliant transceiver supporting 250 kbps O-QPSK data in 5.0 MHz channels, and full spread-spectrum encoding and decoding

- Fully compliant Bluetooth v4.2 Low Energy (BLE)

- Reference design area with small-footprint, low-cost RF node:

- Single-ended input/output port

- Low count of external components

- Programmable output power from -30 dBm to +3.5 dBm at the SMA connector

- Receiver sensitivity is -100 dBm, typical (@1 % PER for 20-byte payload packet) for 802.15.4 applications, at the SMA connector

- Receiver sensitivity is -95 dBm (for BLE applications) at the SMA connector

- Integrated PCB inverted F-type antenna and SMA RF port (requires moving C122 to C121)

- Selectable power sources

- DC-DC converter with Buck and Bypass operation modes

- 32 MHz & 32.768 kHz reference oscillators

- 2.4 GHz frequency operation (ISM and MBAN)

- USB device mode interface with a micro USB connector

- 32-Mbit (4 MB) external serial flash memory for Over-the-Air Programming (OTAP) support

- FXOS8700CQ Digital Sensor, 3D Accelerometer (±2g/±4g/±8g) + 3D Magnetometer

- Integrated Open-Standard Serial and Debug Adapter (OpenSDA)

- 1x RGB LED indicator, 1x red LED status indicator, 1x green LED power indicator, 1x red LED reset indicator, 1x amber LED OpenSDA activity indicator

- 4x push-button switches

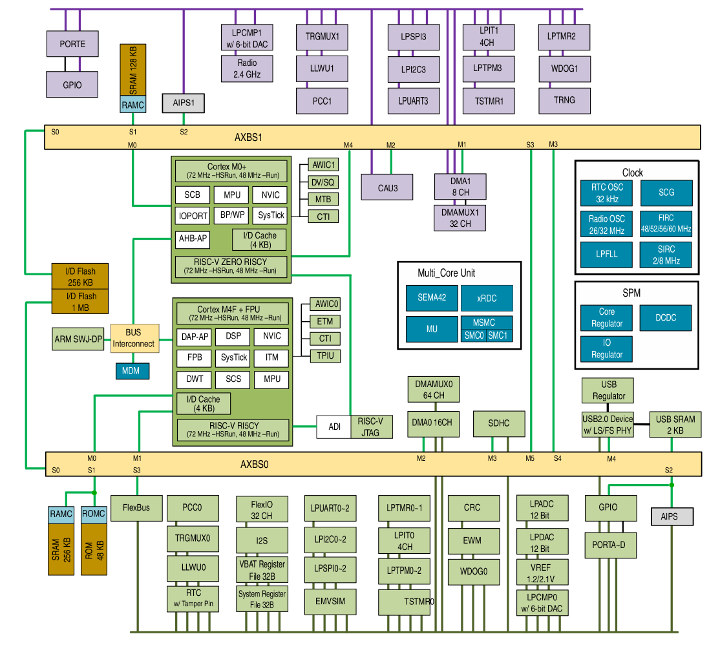

There’s no clear explanation that I could find for the presence of Arm cores inside RV32M1 WiSoC, but maybe it’s just to have a single platform to evaluate Arm and RISC-V core since RV32M1 block diagram shows the Arm Cortex-M0+ and ZERO-RISCY cores in the same block, and the same is true for Cortex-M4F and RI5CY cores.

You can download documentation, Windows/Linux/Mac OS SDK, and toolchains in the Download page, or get everything from release 1.0.0 on Github.

Via HackaDay

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

The giveaway was limited to the USA

VEGABoard is now up for sale for $43.

what is the website to purchase this board?

Directly from VEGABoard official website.