SiFive has recently announced their Core IP 7 Series of RISC-V cores offering better performance, and designed to enable “embedded intelligence” in applications such as 5G, networking, storage, augmented reality, artificial intelligence, SLAM, and sensor fusion.

Three families of the new 7 Series been launched with namely SiFive E7, S7 and U7 Core IP Series, so let’s have a look at each of them.

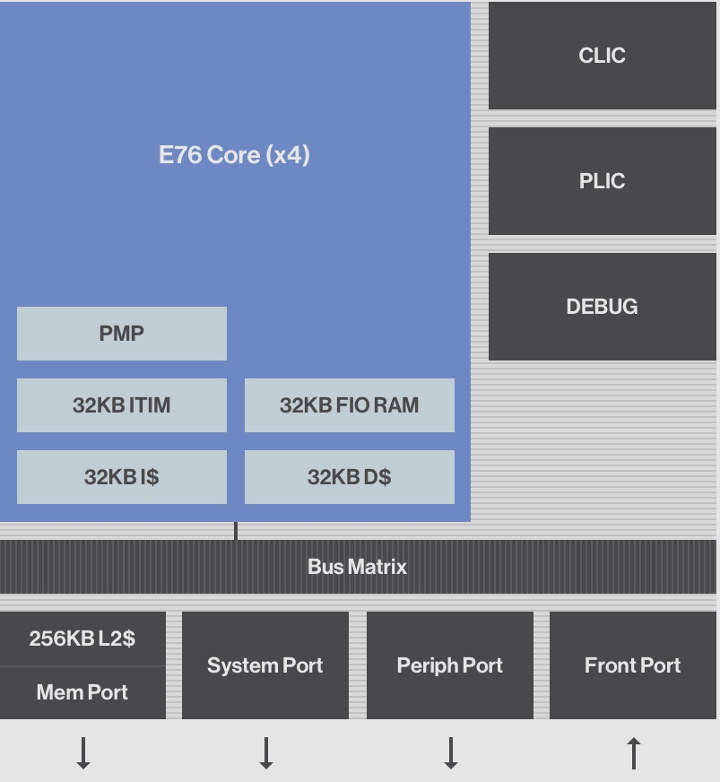

E7 Core IP Series – E76 and E76-MC Cores

The E7 Core IP Series comprises the 32-bit E76 and E76-MC (Multi-core), provides hard real-time capabilities, and compares to Arm’s Cortex M7, Cortex-R7/R8 cores.

E76-MC Key Features

- Fully compliant with the RISC-V ISA specification

- 4x RV32IMAFC E76 Cores

- Machine and User Mode Support

- In-order, 8-stage pipeline

- Advanced Memory Subsystem

- 32KB Instruction Cache

- 32KB Instruction Tightly Integrated Memory (ITIM)

- 32KB Data Cache

- 32KB FIO RAM

- 256KB L2 Cache

- High-performance TileLink Interface

- Benchmark Scores- 2.3 DMIPS/MHz, 4.9 CoreMark/MHz

E76 is basically the same but with one core, no L2 cache, and no PLIC (Platform Level Interrupt Controller).

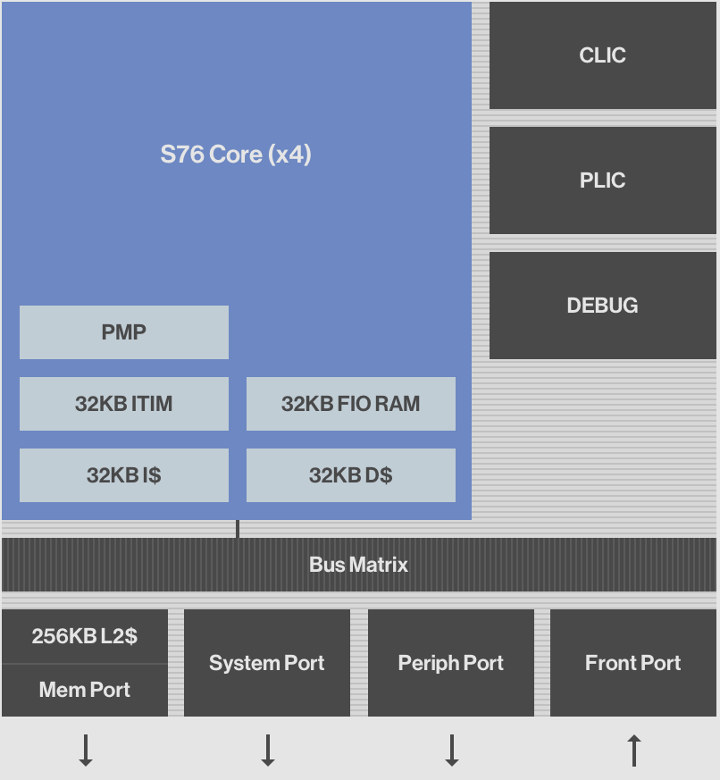

S7 Core IP Series – S76 and S76-MC Cores

The SiFive Core IP S7 Series also compares to Arm’s Cortex M7 and Cortex R7/R8 cores, but S76 and S76-MC cores are based on a high performance 64-bit architecture instead.

- Fully compliant with the RISC-V ISA specification

- 4x RV64GC S76 Cores

- Machine and User Mode Support

- In-order, 8-stage pipeline

- Advanced Memory Subsystem

- 32KB Instruction Cache

- 32KB Instruction Tightly Integrated Memory (ITIM)

- 32KB Data Cache

- 32KB FIO RAM

- 256KB L2 cache

- Efficient and flexible interrupts

- Physical Memory Protection (PMP)

- High-performance TileLink Interface

- Benchmarks – 2.5 DMIPS/MHz, 4.9 CoreMark/MHz

Again the S76 core is the single core version without L2 cache, nor PLIC.

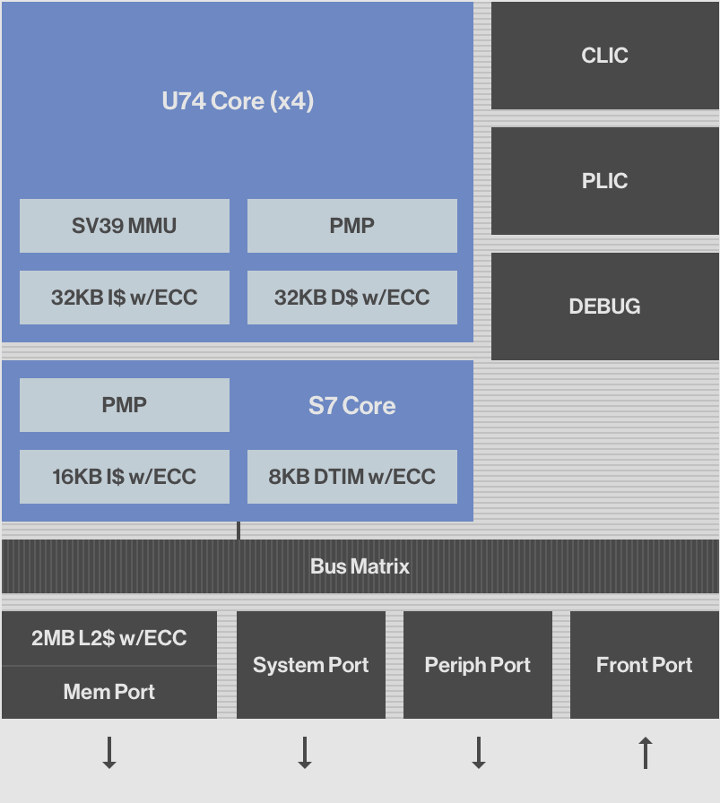

U7 Core IP Series – U74 and U74-MC Cores

Like other SiFive U-series RISC-V processor such as Freedom U540, the SiFive Core IP U7 Series is a Linux-capable applications processor. As such the 64-bit U74 and U74-MC processor cores support Linux, and compare to Arm’s Cortex A55 processor.

U74-MC Key Features:

- Fully-compliant with the RISC-V ISA specification

- 4x RV64GC U74 Application Cores with 32KB L1 I-cache with ECC, 32KB L1 D-cache with ECC, 8x Region Physical Memory Protection, Sv39 Virtual Memory support with 38 Physical Address bits

- 1x RV64IMAC S7 Monitor Core with 16KB L1 I-Cache with ECC, 8KB DTIM with ECC, 8x Region Physical Memory Protection

- U74 and S7 cores are fully-coherent

- Integrated 2MB L2 Cache with ECC

- CLIC for timer and software interrupts

- PLIC with support for up to 128 interrupts with 7 priority levels

- Real-time Capabilities – The L1 Instruction Cache and the L2 Cache can be configured into high-speed deterministic SRAMs

- Debug with instruction trace

- Benchmark Scores – 2.5 DMIPS/MHz, 4.9 CoreMark/MHz

The single core version – U74 – does not include a monitor core, and comes with 128KB L2 cache, instead of 2MB for U74-MC.

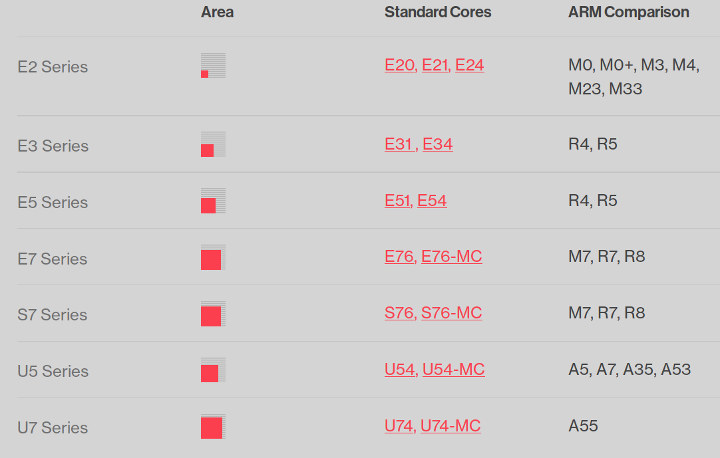

You’ll find further details on SiFive’s Core Designer page. It may be a little confusing to remember all new SiFive parts, so the company has provided a comparison table which you can refer to.

So that means SiFive now offers RISC-V cores competing with most of recent Arm cores, except for the most powerful Cortex-A7x cores like Cortex-A76, but I suppose that’s the next stage.

So that means SiFive now offers RISC-V cores competing with most of recent Arm cores, except for the most powerful Cortex-A7x cores like Cortex-A76, but I suppose that’s the next stage.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

“the SiFive Core IP U7 Series is a Linux-capable applications processor. …. compare to Arm’s Cortex A55 processor.” … so when can we expect SBC’s with a SiFive Core IP U7?

Maybe next year. Keep in mind that AFAIK so far the RISC-V SoCs I’ve seen come without VPU or GPU, but maybe it will change since they talk about AR and VR applications.

Oops, with E76, mistakenly says 256MB of L2 cache, not 256KB.

I saw this announcement earlier this week but could not find proper specifications of the cores — glad we have them now.

Also, it’s good to have realistic comparisons to arm counterparts (and SiFive’s appear realistic so far, in contrast to some by other risc-v proponents that I’ve seen) — that both helps set expectations and shows SiFive are serious in their endeavor to build up a lineup. If only the U5 board did not cost $1K+ at the moment.

I am really interested in the pricing then. Really interesting development there 🙂

Wonder if we will ever see a SIFive Android TV box?

That would require android supporting RISC-V which is doesn’t.

Why? Isn’t there a linux kernel support for RISC-V?

Aas far as I understand the tv box market only ever slightly adjusted reference designs are manufactured. So as long as sifive wont come up with a crippled ref design and a android bsp based on a fully blobbed 2.4 kernel no one will throw one on the market…

Producing one would give them a mass market device, if they produce a good device with a current Linux kernel. Good sales would make the Soc cheaper.

I tought kernel no one is interested in, just price and latest Android version…

> Isn’t there a linux kernel support for RISC-V?

Isn’t this absolutely irrelevant for Android? No VPU support, no GPU support right now with RISC-V (is there even display support?) and Google moving away from Linux to something called Zircon…

If you use expansion board you can plug SSD and AMD GPU, then install Fedora 29 GNOME. You can use it as a desktop system, but not a fast one.

Instructions: https://github.com/westerndigitalcorporation/RISC-V-Linux

Maybe one day

https://hub.packtpub.com/a-libre-gpu-effort-based-on-risc-v-rust-llvm-and-vulkan-by-the-developer-of-an-earth-friendly-computer/

https://www.phoronix.com/scan.php?page=news_item&px=Libre-GPU-RISC-V-Vulkan

You’re referring to this, right: http://libre-riscv.org/3d_gpu/

This is such a pie-in-the-sky idea that I don’t know here to begin with. Frist, a more viable approach would be to step on the (nearly) finalized risc-v SIMD extension, as that, in contrast to other ‘I have an idea’ extensions does have fairly good chances at wide compiler support. Second, start with a software implementation, run (or simulate) that on a properly parallel (16+) small cores setup, featuring the required extensions, see where you spend most of the tima at, optimize, rinse, repeat. Once you have that covered, _only_then_ it makes sense to start hypothesizing about this or that custom extension. Last but not least, $250K is peanuts for such a project. At the end of the day, licensing a Vivante core and using etnaviv would be a _much_ more viable approach to providing a gpu to a risc-v SoC.

True

Also bear in mind Phone sales are falling year on year. So other GPU venders need to find markets other than phone. Most low price TV boxes and SBC that use the same chips are Mali, not all but many.

So does that create a market GPU competition?

The main barrier seems to be well documented trusted drivers ?

hi,

unfortunately, a GPU is not quite as simple and straightforward as “adding a vectorisation system”. we are going to need to add custom opcodes for 4×32-bit FP ARGB to a single 32-bit pixel ARGB conversion, for example… oh and it needs to be hugely parallel, as well. if you look at how many instructions would be needed to do that using a vector processor, it’s insane numbers.

then, the vectorisation system for RISC-V is completely missing bit manipulation, which is absolutely essential for the *other* task that this processor design will tackle: Video Decode.

yes, we are starting with a software implementation: Kazan. we are already being both guided and constrained by the Vulkan API, and it has already saved us both a huge amount of effort and also from making some severe and costly mistakes.

there’s a huge amount more that could be said here, it’s probably best to follow the updates here https://www.crowdsupply.com/libre-risc-v/m-class