So far, if you needed high speed storage with low pin count in your MCU based board, you could use QSPI (Quad SPI) NOR flash, but earlier this month I wrote about STM32L4+ MCU family, which added two Octo SPI interfaces.

I had never heard about Octo SPI previously. Those two interfaces can be used with single, dual, quad, or octal SPI compatible serial flash or RAM, and support a frequency of up to 86 MHz for Octal SPI memories in STM32L4+ MCU.

STMicro OctoSPI interface also supports Cypress/Spansion Hyperbus mode to connect to HyperFlash or HyperRAM chip, or even HyperFlash + HyperRAM Multi-Chip packages (MCP), and variable or fixed external memory latency as defined by the Hyperbus protocol specification. The latter reveals Hyperbus supports performance up to 400 MB/s (provided the controller support 200 MHz), and relies on either 11 bus signals using 3.0V I/O (Single-ended clock CK), or 12 bus signals using 1.8V I/Os (differential clock CK, CK#).

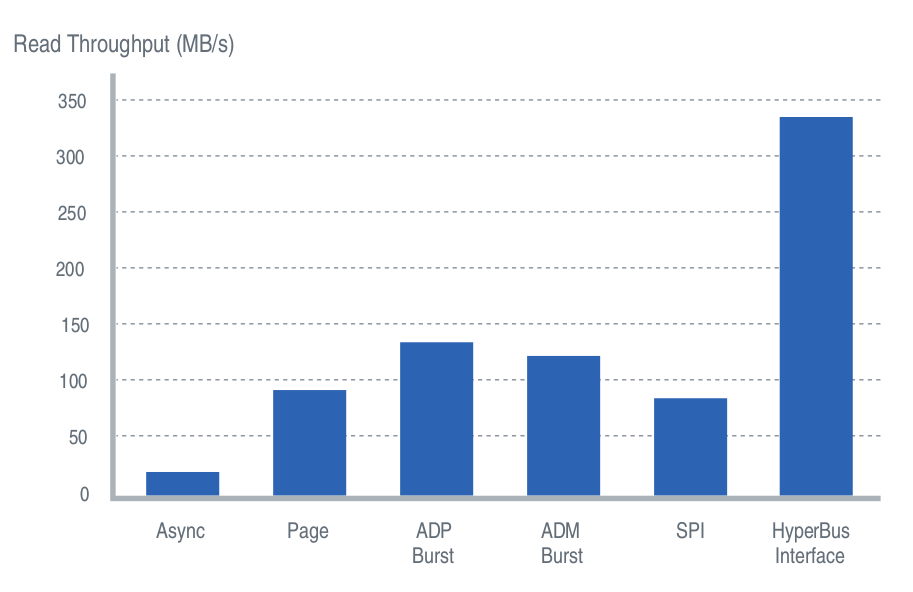

The chart above compared the performance of an actual HyperFlash (333 MB/s) against other NOR flash with legacy parallel interfaces (Async, Page and ADP Burst) and QSPI (It’s written SPI, but they mean SQPI @ 80 MB/s).

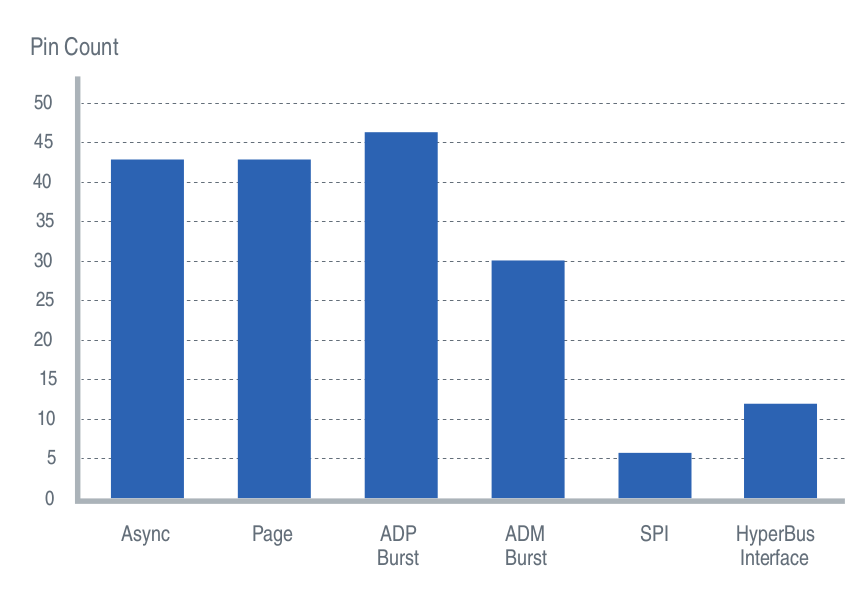

Pin count had to increase from 6 for QSPI to 11/12 for HyberBus, but it’s still low compared to parallel interfaces.

Cypress HyperFlash NOR flash memories have capacities of 128 to 512 Mbit, and throughput of up to 333 MB/s for 1.8V versions, and 200MB/s for 3V versions. The MCP chips come with either 256 or 512 Mbit HyperFlash, and 64Mbit HyperRAM with 1.8V or 3.0V versions in a FBGA-24 package measuring 8 x 6 x 1 mm.

ISSI also sells HyperFlash storage chips (128 to 512 Mbit), and Macronix International (MXIC) has something similar with their OctaBus memory interface and OctaFlash some of which support up to 250 MHz (500MB), and offers a large capacity from 64Mbit to 2Gbit. The press release in 2016 also mentions OctaRAM, and OctaMCP chips, but product pages are not available for the last two, maybe because another company, JSC, launched OctaRAM with 64-bit and 128-bit density. All those products use the same 12-pin interface, but it’s unclear whether they are compatible, and OctaBus specifications are nowhere to be found.

On the MCU side of the equation, beside STM32L4+, we’ll unsurprisingly find some Cypress solutions with FM4 Cortex-M4 micro-controllers, and Traveo Cortex-R5 MCUs, and the recently announced NXP i.MX RT Cortex M7 crossover processors also support it, and i.MX RT1050 Evaluation Kit even includes 512 Mbit Hyperflash. Renesas Car H3 processor also supports HyperBus interface, and they fitted Hyperflash on at least one of their automotive development board.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

This needs to be added to router SoCs so we can see some improved performance on routers not using NAND flash (or eMMC in a handful of cases), as it should help boost boot times significantly, since most routers rely on a compressed image in SPI flash which is extracted into RAM for execution.

QSPI has been a pseudo-standard for too long, so this is a very welcome development. I do still wish they had included a nibble wide QSPI like reduced pin count version, but I understand that they already see themselves as the low pin count version of the competing interface standards.

The W25Q128F already has 50MB/S continuous data transfer rate so…

I don’t understand why Hyperbus can be an improvement over sdcard/emmc. both implement serial 8 bit transfert lines…Maybe an improvement about licence IP price.

SDIO speed should be in the benchmark chart!

@bob

I think it’s difficult to find eMMC flash below 4 or 8 GB(ytes) capacity now, so there’s a role for this type of smaller NOR flash in embedded systems.

Related news “Cypress HyperBus Memory Interface Incorporated into JEDEC xSPI Electrical Interface Standard” -> http://www.cypress.com/news/cypress-hyperbus-memory-interface-instant-applications-incorporated-jedec-xspi-electrical

Not read and checked what it means in details yet.

Hyperbus memory devices such as HyperFlash and HyperRAM are already being used commercially in combination with Intel FPGA devices due to their low pincount and high bandwidth. S/Labs Hyperbus controller IP (https://synaptic-labs.force.com/s/ip-hbmc) is a very compact yet powerful IP that achieves high bandwidth (over 270 Mbytes/s), making it ideal for XIP software, video streaming, ethernet, DMA applications and other.