Open source used to be a software thing, with the hardware design being kept secret for fear of being copied, but companies such as Texas Instruments realized that from a silicon vendor perspective it would make perfect sense to release open source hardware designs with full schematics, Gerber files and SoM, to allow smaller companies and hobbyists, as well as the education market, normally not having the options to go through standard sales channels and the FAE (Field Application Engineer) support, to experiment with the platform and potentially come up with commercial products. That’s exactly what they did with the Beagleboard community, but there’s still an element that’s closed source, albeit documented: the processor itself.

But this could change soon, as SiFive, a startup founded by the creators of the free and open RISC-V architecture, has announced two open source SoCs with Freedom U500 processor and Freedom E300 micro-controller.

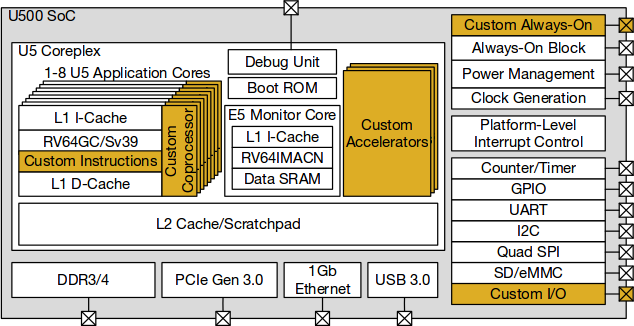

Freedom U500 (Unleashed family) platform key specifications:

- U5 Coreplex with 1 to 8 U54 cores @ 1.6GHz+

- RV64GC Architecture (64- bit RISC-V)

- Multicore, Cache Coherency Support

- High Speed Peripherals: PCIe 3.0, USB3.0, GbE, DDR3/4

- TSMC 28nm

The SoC supports Linux, and targets applications such as machine learning, storage, and networking.

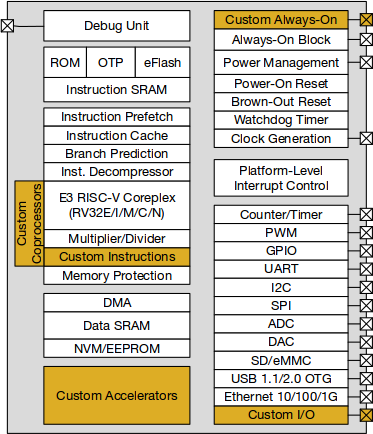

Freedom E300 (Everywhere family) platform key specifications:

- E3 Coreplex

- RV32IMC/RV32EMC Architecture

- On chip Flash, OTP, SRAM

- TSMC 180nm

Three real-time operating systems, including FreeRTOS, have already been ported to Freedom E300 for embedded micro-controllers, IoT, and wearable markets.

Open source SoCs are made to be customizable to match your applications exact needs, instead of picking on existing SoC matching your requirements but with some uneeded features. SiFive also explains that “storage customers talks about custom instructions for bit manipulation so they can use one not 10 instructions for 10x speed up”. But before you get to Silicon, you’d normally ruin and customize the core on FPGA boards and three boards are currently available for development and evaluation:

- Freedom U500:

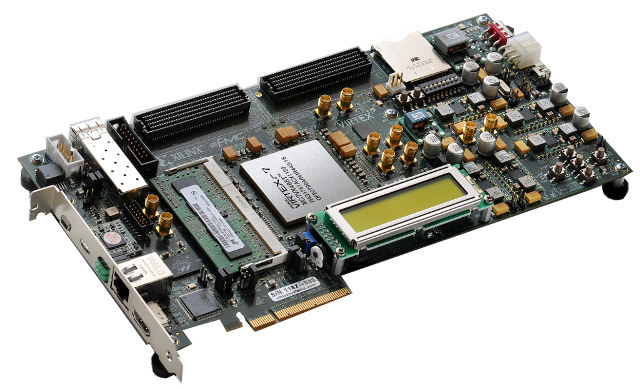

- Xilinx Virtex-7 FPGA VC707 development kit with 1GB DDR3 SODIM Memory up to 800MHz / 1600Mbps, serial connectivity with PCIe Gen2x8, SFP+ and SMA Pairs, UART, IIC, Gigabit Ethernet support, etc… Price: $3,450.

- Microsemi SF2+ FPGA Devkit with LPDDR, SPI Flash, Ethernet, timberwolf Audio Processor, etc… Price: $125

- Freedom E300 – Digilent Arty FPGA development kit powered by Xilinx XC7A35T-L1CSG324I FPGA, with 256 MB RAM, 16 MB flash, and vairous expension ports. Price: $99

You also have detailed documentation about the SoCs, U5 nd U3 coreplex, the development kits, software and tools, as well as developer forums, on SiFive developers website. You can also directly checkout the code and SDK on github.

RISC-V instructions set is royalty-free, so compared to the entry level $40,000 ARM license for startups using Cortex M0 MCU, it should provide some savings. It does not help with manufacturing costs which should remain the same. but SiFive expects that open source SoC could be manufactured through a “moderate” crowdfunding campaign. I have not been able to figure out SiFive business model yet, unless they plan on selling their own chips too, and/or provide customization services to customers.

Lots more information can be found on Sifive website.

Via EETimes

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

> I have not been able to figure out SiFive business model yet

I guess they’re hoping to be the RISC-V hardware equivalent of Red Hat. They’re offering development boards, support and documentation for RISC-V implementers. I suspect they’re also servicing as consultants to optimize performance and such.

Kinda like IBM in OpenPOWER. Only without the servers… For now.

RISC-V is an open ISA.

It is NOT an open implementation – implementations can be open or closed.

SiFive is providing an implementation that you can use in your own ASIC (or maybe FPGA) – IIRC, they claim it is flexible and easy to customize (e.g. add custom instructions, which RISC-V is designed to handle – I believe adding custom instructions to ARM would require an architectural license, which will be much more than $40K).

Good to see RISC-V taking off in silicon form.

Interesting article. Please post more about RISC-V, especially actual CPU implementations and usage.

I found this interesting: https://en.wikipedia.org/wiki/RISC-V

And I’m now follwing RISC-V on twitter: https://twitter.com/risc_v

Just for fun, I’m now running a RISC-V qemu instance on my Ubuntu:

# uname -a

Linux buildroot 3.14.41-g886e5f9 #13 Sat Jan 30 16:54:43 UTC 2016 riscv GNU/Linux

#

# cat /proc/cpuinfo

hart : 0

isa : RV64G