lowRISC is not the only open source processor project based on RISC-V instructions, as researchers at ETH Zurich university and the University of Bologna have developed PULPino open-source processor based on RISC-V instructions set, optimized for low power consumption, and targeting wearables and the IoT applications.

PULPino is a single core processor derived from the PULP project (Parallel Ultra-Low-Power Platform) featuring a quad core RISC-V SoC with new RI5CY Signal Processing ISA extensions designed by the universities.

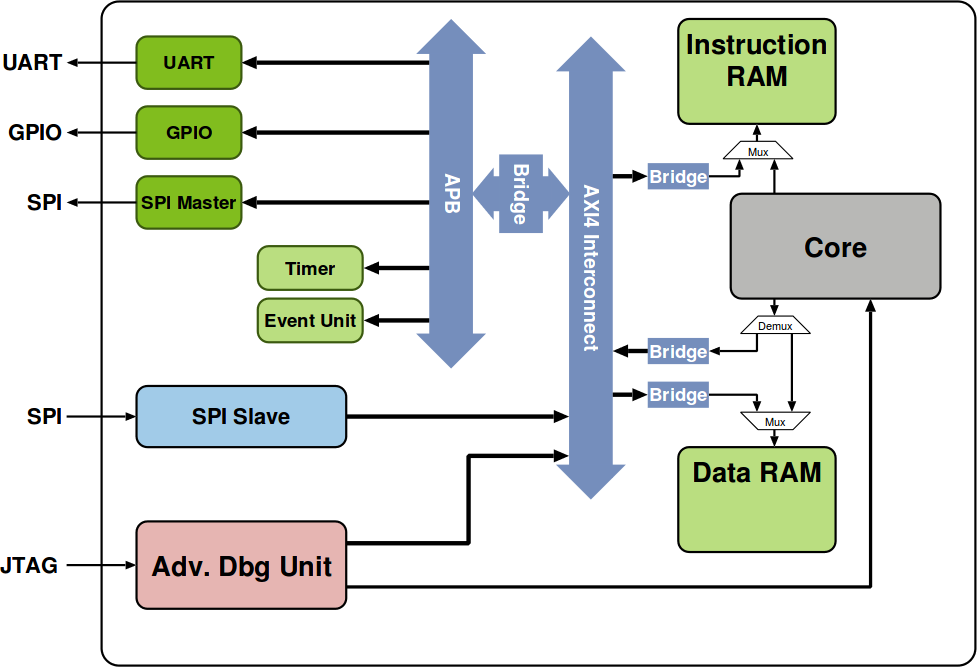

The core has an IPC (instructions per cycle) close to 1, full support for the base integer instruction set (RV32I), compressed instructions (RV32C) and partial support for the multiplication instruction set extension (RV32M). PULPino also features peripherals such as I2S, I2C, SPI and UART.

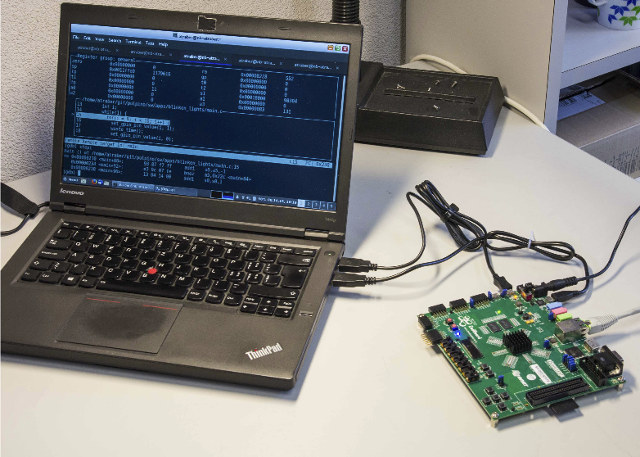

PULPino has already been taped out as an ASIC in UMC 65nm at the beginning of the year, but the RTL code be run on Xilinx Zynq-7010 powered Zedboard, and all source files, test programs, and tools have been released in github under the Solderpad hardware license derived from the Apache 2.0 software license meaning you can basically do what you want with the design.

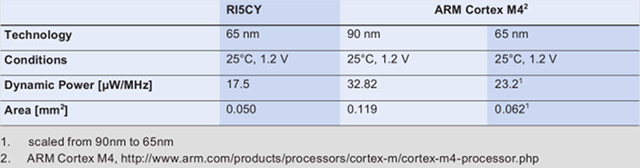

An implementation of FreeRTOS is said to be available for PULPino and PULP processor, but I could not find it. They’ve also compared RI5CY core to ARM Cortex-M4 to show a similar area and power consumption using 65nm process.

You can find more details about PULPino and PULP projects on Pulp Platform website, and PULP page on ETH Zurich university website. lowRISC.org also mentions there are three proposed projects for PULPinfo as part of Google Summer of Code: porting CMSIS-DSP to PULPino, Doom on PULPino, and porting the Arduino libraries to PULPino.

Via EETimes

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

would be nice to know if this chips will be also available for other developers or just stay ‘inside’ the University

@Max

The code is there to run on FPGA boards, and I understand the files to do your own tapeout are available.

But if you mean you’d like to buy SoC made by the university I’m not sure it’s possible.

@cnxsoft

Yes, I got your point and it’s exiting everything is open source and available and ready to run on a FPGA.

What I meant was: if the chip and a developer board would be available, that would be nice.

Should boost RISC-V development as well, especially from SW side

http://www.theregister.co.uk/1999/07/14/what_the_hell/

….is a tapeout :p

Hello all,

After having synthesized Pulpino on a ZedBoard, I tried to run and test an

application (spiload) in pulpino, but I find difficulties ( Compile the

spiload application for the ZYNQ ,Transfer program to the ZYNQ … ) and I did

not find the file spi_stim.txt under the slm_files folder for the application

spiload !!!!

Could you guide me through The steps to follow ? Is it possible to give me an

explanatory file ?

Thanks,