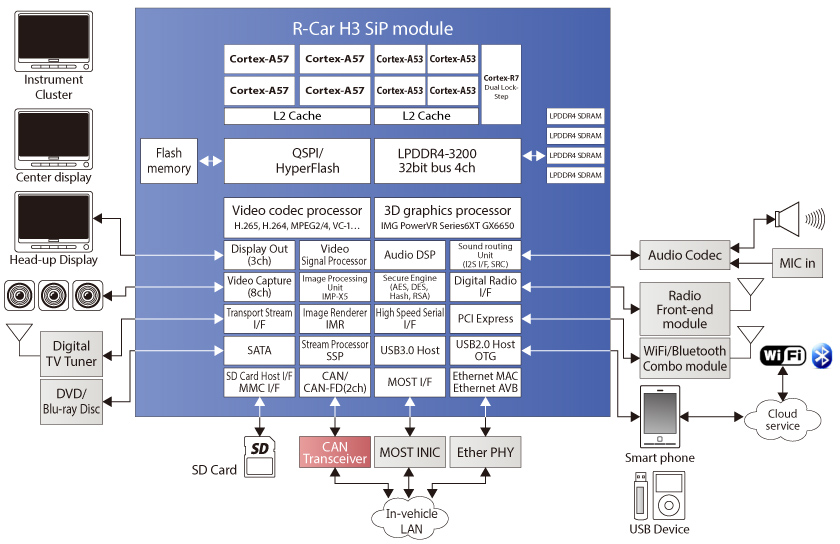

Renesas has recently unveiled R-Car H3 deca-core processor for automotive applications with four Cortex A57 cores, four Cortex A5 cores, and two Cortex-R7 “dual-lock step” cores for real-time processor, and has part the releases showed the expected roadmap for the implementation of driverless / autonomous cars.

Let’s start with the processor (R8A77950) and SiP module (R8J77950) specifications:

- CPU cores – quad core ARM Cortex-A57, quad core ARM Cortex-A53, and dual lock-step ARM Cortex-R7 cores with respectively 48KB/32KB, 32KB/32KB, and 32KB/32KB L1 instructions/operand cache.

- GPU – IMG PowerVR Series6XT GX6650

- External memory – LPDDR4-SDRAM up to 1600 MHz, data bus width: 32 bits x 4 ch (12.8GB/s x 4)

- Expansion bus – 2 ch PCI Express2.0 (1 lane)

- Video

- Out – 3x display output

- Input / camera – 8x video inputs

- Video codec module (H.265, H.264/AVC, MPEG-4, VC-1, etc.)

- IP conversion module

- 2x TS Interfaces

- Stream and Security Processor

- Video image processing (Up and down scaling, Dynamic γ correction, Color space conversion, I/P conversion, Super resolution processing, Rotation, Visual near lossless image compression)

- Distortion compensation module x 4 ch(IMR-LSX4)

- High performance Real-time Image recognition processor(IMP-X5)

- Audio

- Audio DSP

- 10x sampling rate converter, 10x serial sound interface

- MOST DTCP

- Storage – 4x SD host interfaces. 2x MMC interfaces, 1x SATA

- USB – 1x USB 3.0 Host interface (DRD), 2x USB 2.0 Host/Function/OTG interface

- In car network and automotive peripherals

- 3-pin Media local bus (MLB) interface

- 2x Controller Area Network (CAN-FD support) interfaces

- Ethernet AVB 1.0-compatible MAC built in

- RGMII interface

- Security – 2x Crypto engine (AES, DES, Hash, RSA); SystemRAM

- Other peripherals

- 48x SYS-DMAC, 16x Realtime-DMAC, 32x Audio-DMAC, 26x Audio(peripheral)-DMAC

- 26x 32bit timer

- 7x PWM timer

- 7x I2C, 11x Serial communication interface (SCIF)

- 2x Quad serial peripheral interface (QSPI) for boot, HyperFlash support

- 4x SPI/IIS Clock-synchronized serial interface (MSIOF)

- Ethernet controller (IEEE802.3u, RMII, without PHY)

- 4x Digital radio interface (DRIF)

- Interrupt controller (INTC)

- Clock generator (CPG) with built-in PLL

- On chip debugger interface

- Low power mode – Dynamic Power Shutdown, AVS(Adaptive Voltage Scaling), DVFS(Dynamic Voltage and Frequency Scaling), and DDR-SDRAM power supply backup mode

- Supply voltages – 3.3/1.8V (/IO), 1.1V (LPDDR4), 0.8V (core), 2.5V (EthernetAVB)

- Package

- 1384 pin Flip chip BGA (21mm × 21mm, 0.5mm pitch)

- 1255-pin SiP module (42.5mm × 42.5mm, 0.8mm pitch)

- Manufacturing Process – 16nm FinFET+

This impressive system-on-chip supports Linux, Android, QNX Neutrino RTOS, Green Hills Integrity RTOS, and others operating systems. Development tools include an ICE for ARM CPU available from different vendors, and a development board with “car information system-oriented peripheral circuits” that can be used as a software development tool for application software. However, unless you decide to start a car company you probably won’t be able to buy this type of chip or evaluation board… Nevertheless, it could end up in your semi-autonomous car in a few years as while sample are available now, mass production is scheduled to begin in March 2018, with ramping up to 100,000 units per month taking place in March 2019.

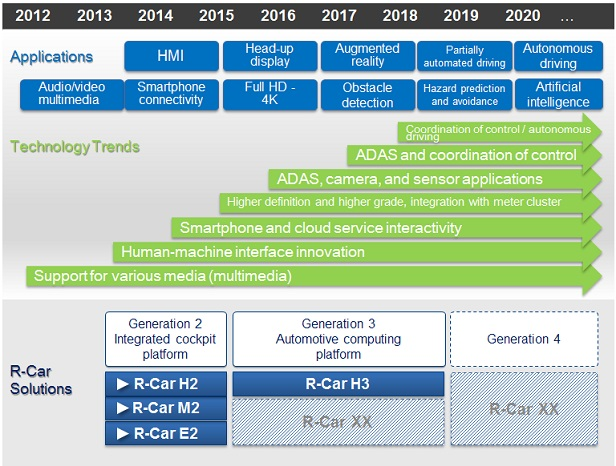

Autonomous car are a sure thing, with Google self-driving cars already on some roads (at slow speeds) and Formula E is even planning for driverless races, so the real question is about the time it may take to solve technical challenges, work out the regulations, and make the public confident enough to sit in autonomous cars. Renesas’ roadmap above shows R-Car H3 will be used for obstacle detection in 2018, semi-automated driving (ADAS = Advanced Driver Assistance Systems) in 2019, while fully autonomous cars may launch around year 2020 and beyond with the next generation (R-Car H4 ?) platform.

You can find more details on Renesas R-Car H3 page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

“Autonomous car are a sure thing, with Google self-driving cars already on some roads…”

I just wonder a couple of things about self driving cars:

(1) If someone gets injured or killed by a self driving car who is responsible? The car?

(2) If the car has to make a split second decision between swerving into a crowd of people or a head-on collision with a semi what choice is made here?

It’s way to soon for these things to be out on the road without somebody having answers for these types of questions.

Too bad it’s only for cars. Could be the base for an awesome PC replacement or a future proof TV box.

@hmayle

No doubt that software developers have full knowledge about your questions. But obviously the companies do not like it to be publicly discussed…