At the end of June, Imagination Technologies unveiled their MIPS Series5 ‘Warrior’ architecture, featuring 32-bit and 64-bit CPU cores, with features such as hardware and software virtualization, and Extended Virtual Addressing (EVA). The company has recently announced the first member of the family with their MIPS P5600 CPU IP core.

The MIPS P5600 core is a 32-bit CPU IP that is said to offer 1.2 to 2x more system performance compared to proAptiv cores, and it supports peak frequencies above 2GHz on TSMC’s 28HPM process node. Performance-wise the core achieves 5 CoreMark/MHz and 3.5 DMIPS/MHz for a single core, which appears to be equivalent to ARM Cortex A15 according to values listed in Wikipedia and EEMBC Coremark results.

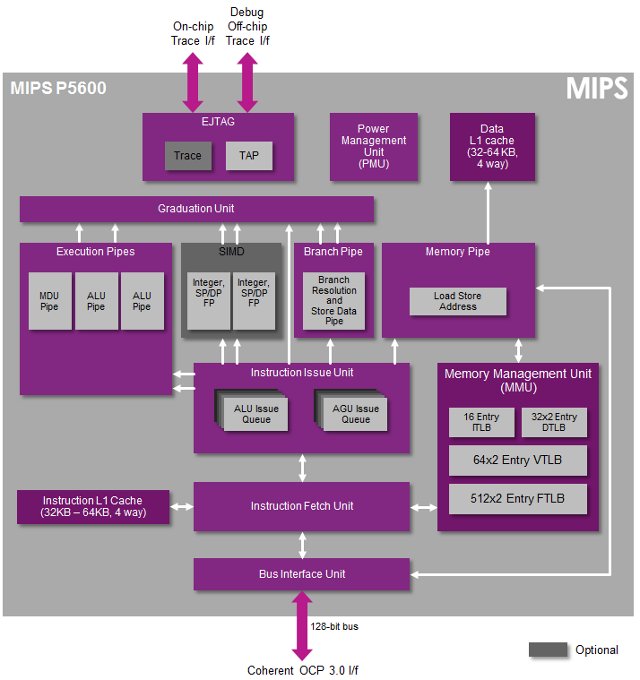

MIPS P5600 features and benefits:

- 32-bit MIPS32 Release 5 Instruction Set Architecture

- 16-stage, wide issue, out-of-order (OoO) pipeline

- Quad instruction fetch per cycle

- Triple bonded dispatch per cycle

- Instruction peak issue of 4 integer and 2 SIMD operations per cycle

- Sophisticated branch prediction scheme, plus L0/L1/L2 branch target buffers (BTBs), Return Prediction Stack (RPS), Jump Register Cache (JRC)

- Instruction bonding – merges two 32-bit integer accesses into one 64-bit access, or two 64-bit floating point accesses into one 128-bit access for up to 2x increase on memory-intensive data movement routines

- L1 cache size for Instruction and Data of 32KB or 64KB each, 4-way set associative

- New dual-issue 128-bit SIMD Unit (optional)

- 32 x 128-bit register set, 128-bit loads/stores to/from SIMD unit

- Native data types – 8-/16-/32-bit integer and fixed point, 16-/32-/64-bit floating point

- IEEE-754 2008 compliant

- Runs at full speed with CPU core

- Full hardware virtualization

- Provides root and guest privilege levels for kernel and user space

- Supports multiple guests, with full virtual CPU per guest = guest OSs run unmodified

- Separate TLBs, COP0 contexts for root and guests –> full isolation, fast context switching, exception and interrupt handling by root

- HW table walk support in TLB for optimal performance

- Complete SoC virtualization support (IOMMU and interrupt handling – see multi-core features)

- Programmable Memory Management Unit (MMU)

- Enhanced Virtual Address (EVA) – Programmable kernel and user segment sizese

- eXtended Physical Address (XPA) – Provides extension to 40-bits of physical address bits (1 TB)

- 1st level micro TLBs (uTLBs) – 16 entry instruction TLB, 32 entry data TLB

- 2nd level TLBs – simultaneous access, variable and fixed page sizes

- 64×2 entry VTLB, 512×2 entry 4-way set associative FTLB

- Hardware table walk for fast page refills

- Power Management Features

- Multi-core cluster power controller (CPC):

- Register-based, visible to/controllable by operating system

- Per CPU voltage domain gating; per CPU clock gating

- Cluster level DVFS capable

- Core level

- Course and fine-grained clock gating throughout core

- Way prediction on data and instruction L1 caches

- Instruction and register-based sleep modes

- Multi-core cluster power controller (CPC):

- EJTAG/PDtrace debug blocks and interface

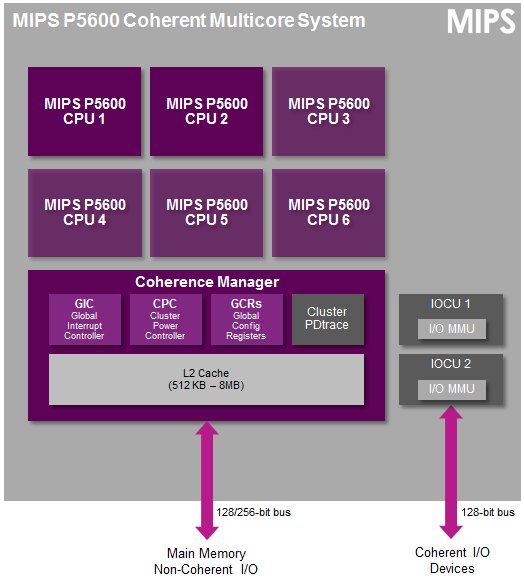

Up to 6 P5600 cores can be bundled together in a single cluster to form a multicore system with some other IP blocks including a coherence manager, 2 I/O Coherence Units (IOCU), … as shown in the diagram below. You can also add video and GPU IP cores to design a multimedia application processor.

In case you wonder why they’re supporting 6 cores, and not just 4 or 8 cores like competitors, the following reason was given on Imagination Technologies blog:

In case you wonder why they’re supporting 6 cores, and not just 4 or 8 cores like competitors, the following reason was given on Imagination Technologies blog:

A six-core cluster enables our partners to build a 4+2/4+1 solution where you have 4 cores running at maximum frequency for crunching down on demanding tasks and 2/1 cores clocked much lower to handle regular tasks. This enables a better scaling in performance while achieving obvious savings in power and area.

Target markets for P5600 include mobile (High-end tablet / smartphone SoCs), digital home (High-end connected DTV / STB application processor), and Networking (802.11ac routers, residential gateways, CPE modems, 3G/4G cell infrastructure control plane, Network appliances and microservers).

The first devices featuring this technology should start to become available in H1 2015.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

I would prefer that chinese company like loongson, instead of imagtion technologies bought MIPS. They made more progress in MIPS IP than MIPS themselve, and their progress are no used by MIPS and ST microelectronics MIPS compatible cores. But the worst, is seeing, what is Imagination Technologies philosophy with their awfull PowerVR. A fully closed world, with bad architecture and drivers. 🙁