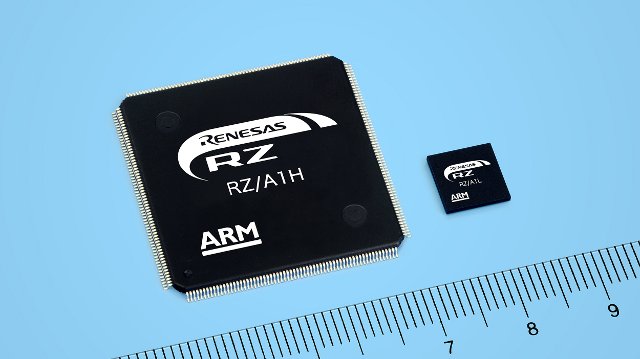

Renesas Electronics has recently introduced the RZ/A1 group of ARM Cortex-A9 microprocessors (MPUs) for automotive, consumer and industrial applications requiring user interfaces with displays with a resolution up to 1280×768 (WXGA). The RZ/A1 series will come in three product groups: RZ/A1H, RZ/A1M and RZ/A1L with respectively 10MB, 5MB and 3MB on-chip RAM. These Renesas SoCs are an upgrade to SH7260 Series.

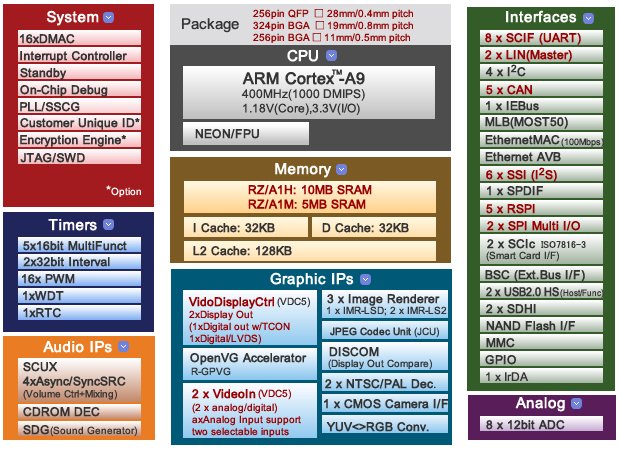

Key Features (Included in A1H and A1M, but not always in A1L):

- Core – ARM Cortex A9 @ up to 400 MHz (with Jazelle and NEON)

- GPU – OpenVG-compliant Renesas graphics processor (2D graphics)

- Cache – 32-Kbyte L1 instruction cache, a 32-Kbyte L1 data cache, and a 128-Kbyte L2 cache.

- Built-in memory – Up to 10-Mbyte large-capacity RAM (128 Kbytes are shared by the data-retention RAM) for A1H, 5MB for A1M, and 3MB for A1L

- External memory

- Up to 66.67 MHz bus

- Direct connection to SRAM, byte select SRAM, SDRAM, and burst ROM (clock synchronous/clock asynchronous) using bus state controller. Address/data multiplexer I/O (MPX) interface supported.

- Address space: 64 MB × 6.

- Data bus width: external 8/16/32 bits

- Graphics Functions:

- OpenVG1.1 2D graphics accelerator

- Video display controller (Up to 2 channels of video input and 2 channels of panel output,

of which 1 channel supports LVDS)

- Video decoder × 2 channels (analog composite direct input is possible)

- Distortion correction engine × 2 channels (requires nondisclosure agreement)

- Distortion correction engine for display (requires nondisclosure agreement)

- Display out compare unit

- JPEG codec unit

- Capture engine unit (CMOS camera interface)

- Pixel format converter × 2 channels

- Audio functions

- SCUX (with built-in asynchronous sampling rate conversion, digital volume & mute, and mixer function)

- Serial sound interface × 6 channels (× 4 channels for A1L)

- Renesas SPDIF interface

- Sound generator × 4 channels

- CD-ROM decoder

- Timer functions

- Multifunction 16-bit timer (MTU2) × 5 channels

- 32-bit OS timer × 2 channels

- Motor control PWM timer × 8 channels

- Watchdog timer

- Real-time clock

- Interfaces:

- USB 2.0 host/function module × 2 channels (host or functon selectable)

- NAND flash interface

- SD host interface × 2 channels (must obtain SD card license)

- MMC host interface

- Ethernet controller (10 Mbps/100 Mbps transfer, IEEE802.3 PHY interface MII)

- Ethernet AVB (IEEE802.1 Audio/Video Bridging) controller (requires nondisclosure agreement)

- SPI multi I/O bus controller × 2 channels (up to 2 serial flash memory connectable to 1 channel, direct execution from CPU supported)

- Serial communication interface with 16-stage FIFO (SCIF) × 8 channels (asynchronous and clock synchronous serial communication possible) Serial communication interface with 16-stage FIFO

- Serial communication interface × 2 channels (smart card interface, IrDA 1.0)

- Renesas serial peripheral interface × 5 channels (× 3 channels for A1L)

- I2C bus interface × 4 channels

- Media Local Bus (MediaLB Ver2.0)

- Controller area network (CAN) × 5 channels (× 2 channels for A1L)

- Local interconnect network interface (LIN) × 2 channels (x 1 channel for A1L)

- System analog functions

- Clock pulse generator (CPG): built-in PLL, maximum 32 times multiplication, built-in SSCG circuit

- Direct memory access controller × 16 channels

- Interrupt controller (with ARM Generic Interrupt Controller [PL390])

- A/D converter (12-bit resolution) × 8 channels

- Debugging interface

- CoreSight architecture

- JTAG standard pin layout

- Optional function – Encryption engine (requires nondisclosure agreement)

Thanks to the integrated on-chip RAM from 3MB to 10MB it’s possible to develop applications without external memory, lowering the BoM cost, EMI, and static power consumption.

Renesas has partnered with several partners including IAR systems, Green Hills Software, ARM, Express Logic, Micrium, and Altia to provide tools and middleware solutions for real-time operating systems (RTOS), networking, USB, graphics and file systems.. In particular, Renesas and ARM are jointly developing a version of RTX CMSIS (Cortex Microcontroller Software Interface Standard)-RTOS for the Cortex-A in order to facilitate transition of application software developed from Cortex-M processors to Cortex-A processors. It’s available in ARM DS-5 for Renesas RZ/A1.

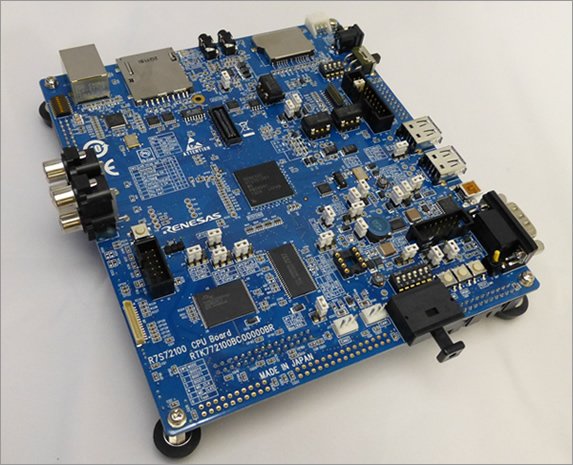

GENMAI CPU Board (R7S72100 CPU Board RTK772100BC00000BR)

To start development early, you can use those software tools on GENMAI CPU Board powered by a 324-pin BGA RZ/A1H processor with 64 MB x 2 NOR flash, 64 MB x 2 SDRAM, 64 MB x 3 Serial flash memory and 16KB EEPROM, as well as most ports supported by the SoC.

The company said samples of select RZ/A1L and RZ/A1H products will be available in July 2013. Further details are available on Renesas RZ/A1 page.

Jean-Luc started CNX Software in 2010 as a part-time endeavor, before quitting his job as a software engineering manager, and starting to write daily news, and reviews full time later in 2011.

Support CNX Software! Donate via cryptocurrencies, become a Patron on Patreon, or purchase goods on Amazon or Aliexpress

The Heading says “10MB On-Board RAM”….

@Nitin Bhaskar

Oops. Sorry, I changed that.

Yes 80Mbit high speed SRAM with 128bit wide internal buses. A formula one class device that can be used almost standalone and very cheap double sided pcb.

Now PIC user’s can move to a real processor without having the headache of DDR3 and LINUX.