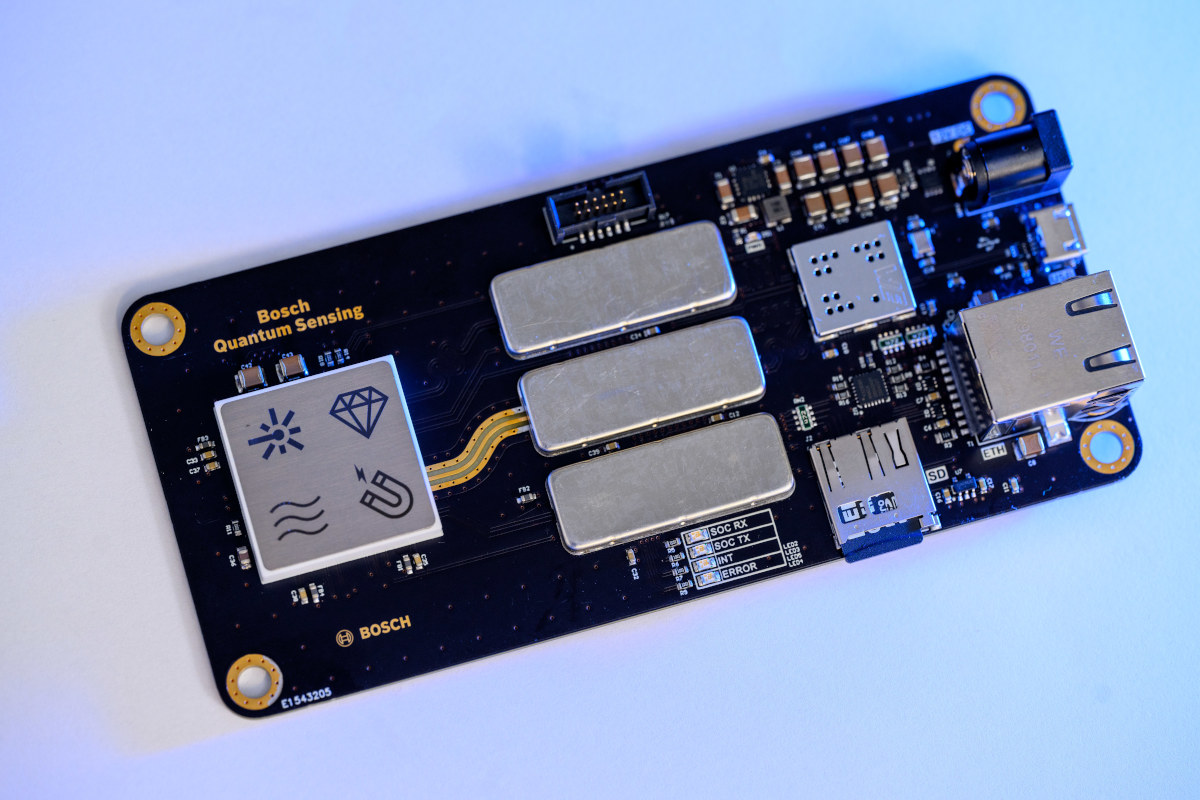

Most people have heard about quantum computers, but quantum sensors? I’ve just come across those as Bosch is developing magnetic-field quantum sensors harnessing “the power of quantum physics to enable measurements with unmatched precision” while being much more compact than other quantum sensors using techniques like SQUIDs (superconducting quantum interference device), vapor cells, or optical traps. Bosch Quantum Sensing (that’s the full company name) further explains its magnetic-field quantum sensors surpass the capabilities of conventional sensors by offering a wider measurement range, higher sensitivity, and higher spatial resolution. They currently have an internal quantum sensor prototype/evaluation board that’s about the size of a smartphone, so they are still quite larger than traditional sensors. Bosch quantum magnetometer can measure tiny magnetic field variations with accuracy, including the Earth magnetic’s field, and even analyze the direction of and magnetude of magnetic fields giving the equivalent of a 3D-point magnetic representation. This notably […]

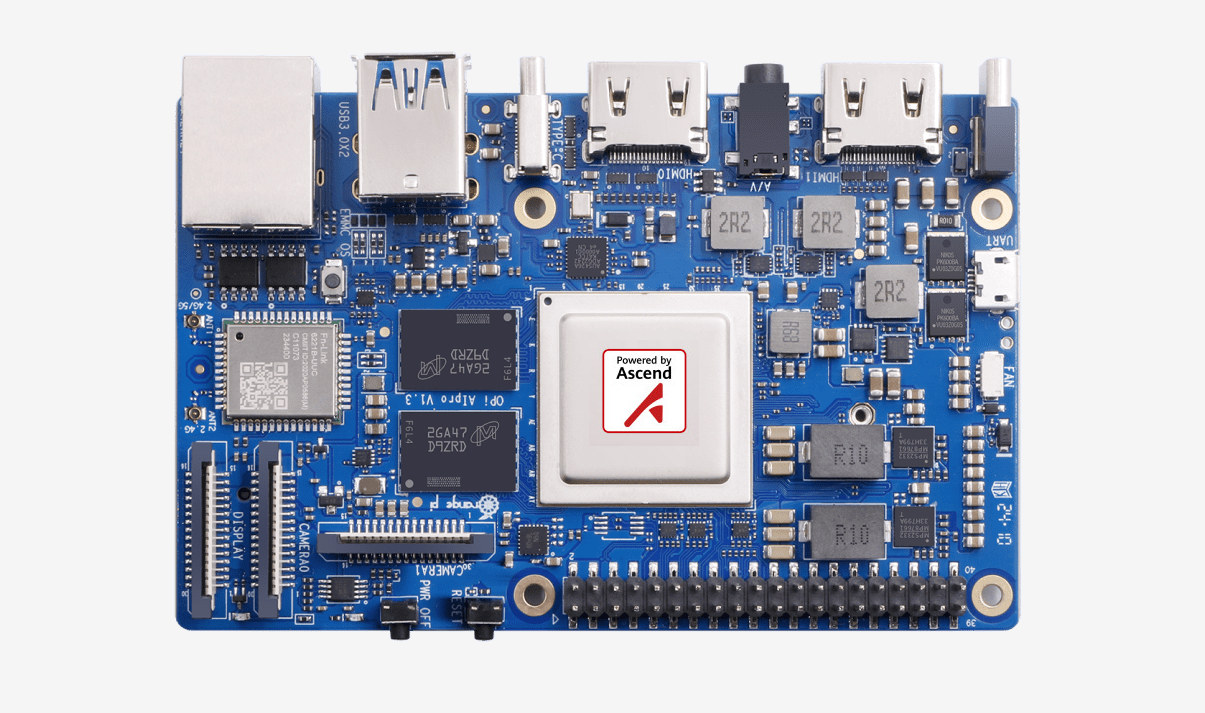

Orange Pi AIPro (8T) SBC features a 8 TOPS Huawei Ascend AI SoC, runs Ubuntu or openEuler

Orange Pi AIPro (8T) is a new single board computer for AI applications that features an unnamed Huawei Ascend AI quad-core 64-bit processor delivering up to 8 TOPS (INT8) of AI inference performance, although there’s also a 20 TOPS (INT8) variant of the SoC. The SBC comes with up to 16GB LPDDR4X and a 32MB SPI flash but also supports other storage options such as a microSD card, an eMMC flash module, and/or an M.2 NVMe or SATA SSD. The board also features two HDMI 2.0 ports, one MIPI DSI connector, a 3.5mm audio jack, two MIPI CSI camera interfaces, Gigabit Ethernet and WiFi 5 connectivity, a few USB ports, and a 40-pin GPIO header for expansion. Orange Pi AIPro specifications: SoC – Huawei Ascend quad-core 64-bit processor delivering up to 8 TOPS (INT8) AI performance and equipped with an unnamed 3D GPU; Likely Ascend 310B with Arm Cortex-A76 equivalent […]

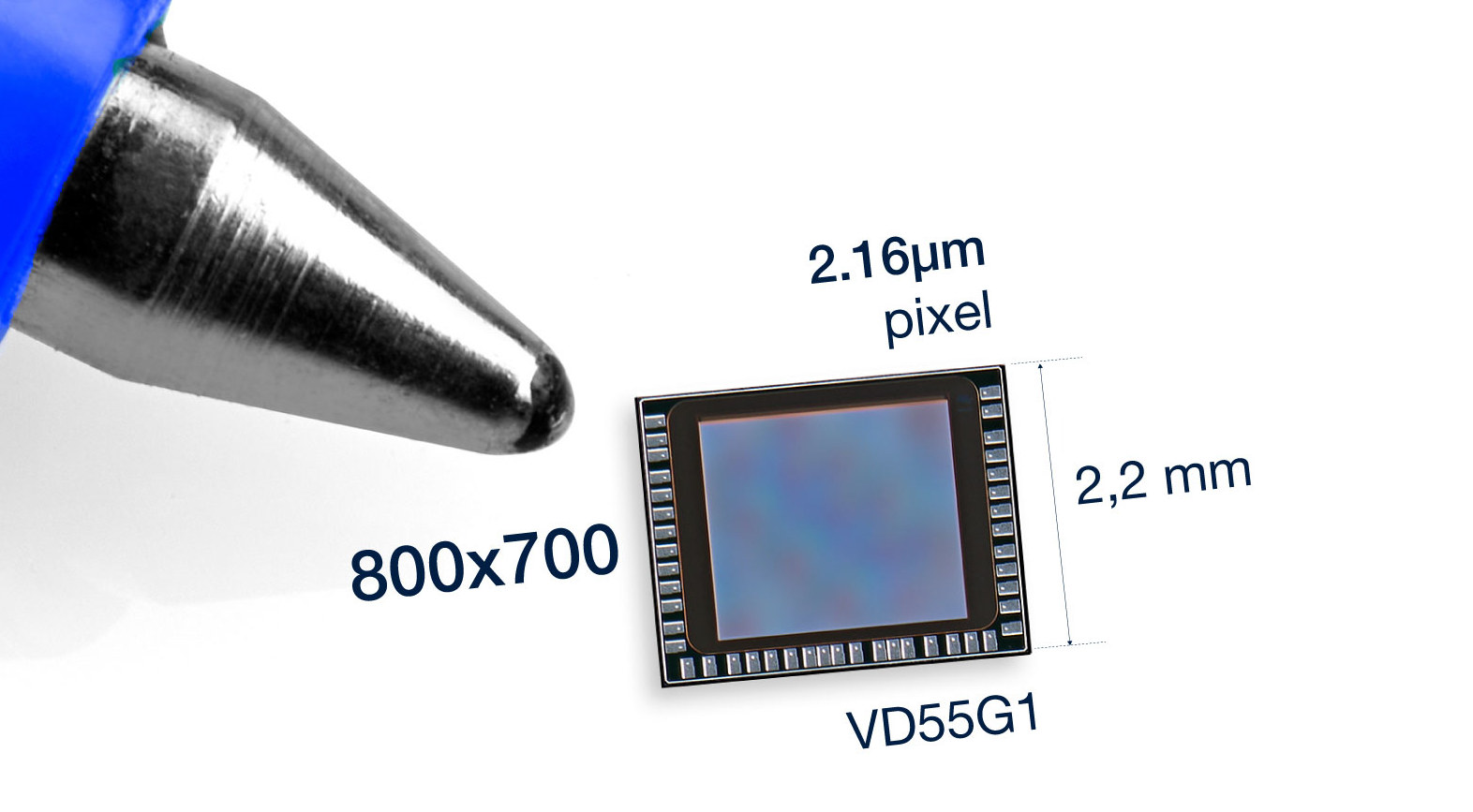

STMicro VD55G1 – A small, low-power global shutter I3C camera sensor for computer vision

STMicro VD55G1 is a new global shutter I3C camera sensor with a small die size of 2.7 x 2.2 mm, 804 x 704 pixels native resolution, and consuming about 1mW in its ‘always-on’ autonomous mode to wake up the host when motion is detected. Camera sensors are available with rolling or global shutter, with most from the former type, but as we’ve seen in our reviews of the e-Con Systems See3CAM_24CUG (USB 3.1) and the Raspberry Pi Global Shutter (MIPI CSI) global shutter cameras, the latter is much better we capturing moving objects clearly at high frame rates with fewer artifacts than with rolling cameras. The VD55G1 global shutter sensor will also benefit from the same advantage but is offered in a smaller package working over MIPI CSI and/or I3C, making it suitable for devices with small batteries used in applications such as eye tracking or motion estimation. STMicro VD55G1 […]

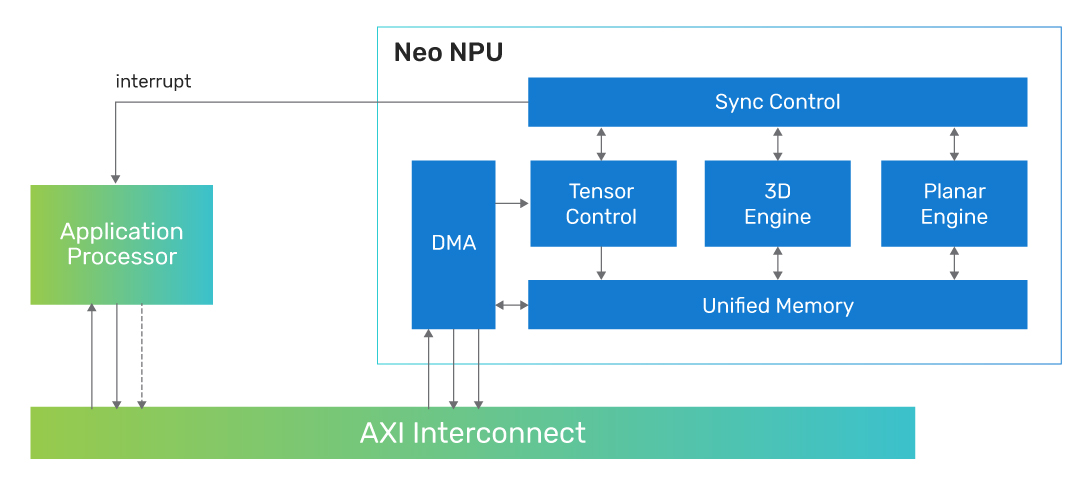

Cadence Neo NPU IP scales from 8 GOPS to 80 TOPS

Cadence Neo NPU (Neural Processing Unit) IP delivers 8 GOPS to 80 TOPS in single core configuration and can be scaled to multicore configuration for hundreds of TOPS. The company says the Neo NPUs deliver high AI performance and energy efficiency for optimal PPA (Power, Performance, Area) and cost points for next-generation AI SoCs for intelligent sensors, IoT, audio/vision, hearables/wearables, mobile vision/voice AI, AR/VR and ADAS. Some highlights of the new Neo NPU IP include: Scalability – Single-core solution is scalable from 8 GOPS to 80 TOPS, with further extension to hundreds of TOPS with multicore Supports 256 to 32K MACs per cycle to allow SoC architects to meet power, performance, and area (PPA) tradeoffs Works with DSPs, general-purpose microcontrollers, and application processors Support for Int4, Int8, Int16, and FP16 data types for CNN, RNN and transformer-based networks. Up to 20x higher performance than the first-generation Cadence AI IP, with […]

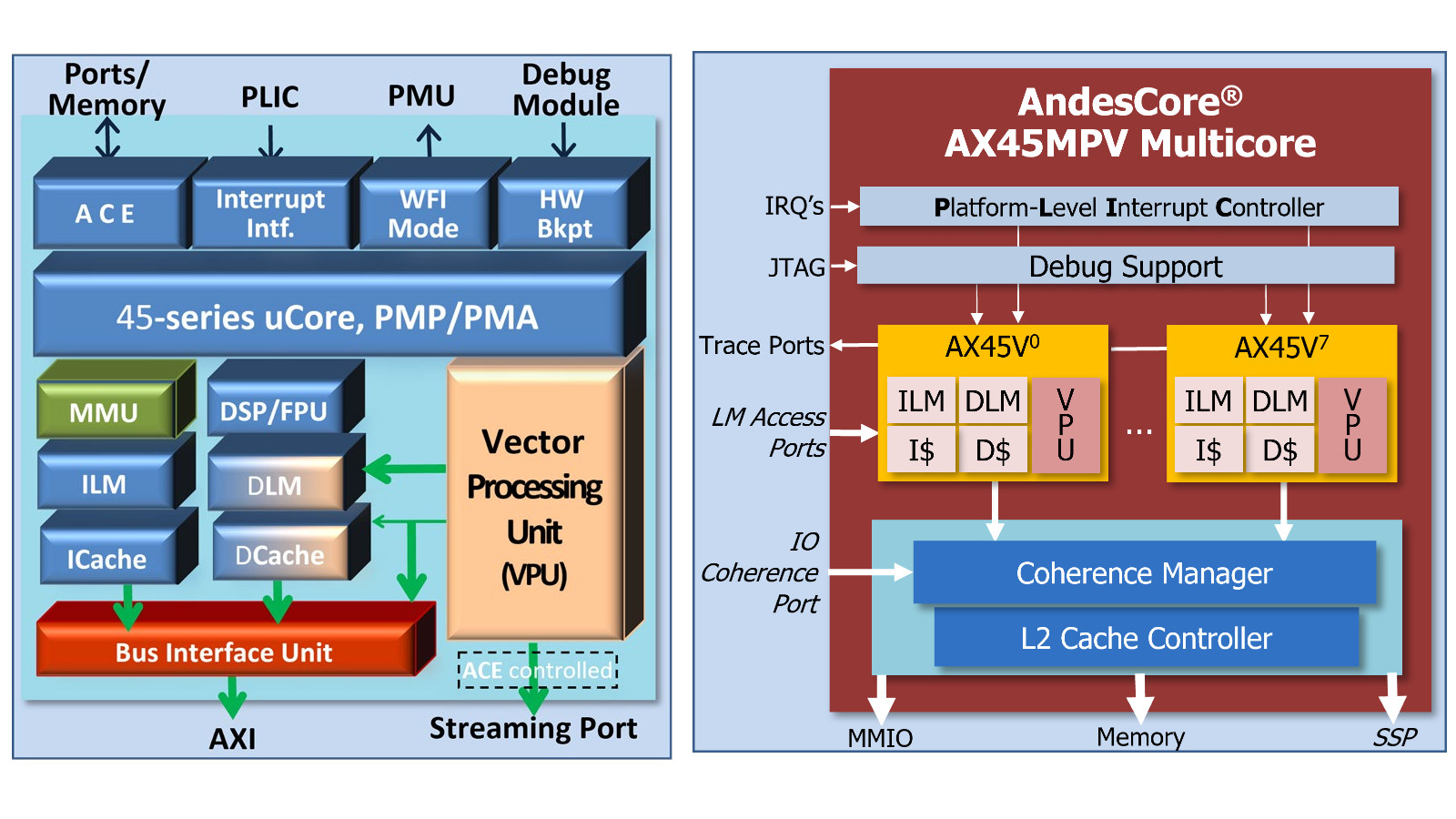

Andes launches AX45MPV RISC-V CPU core with Vector Extension 1.0

Andes Technology has recently announced the general availability of the AndesCore AX45MPV RISC-V CPU which builds upon the AX45MP multicore processor and adds RISC-V Vector Extension 1.0. Equipped with RISC-V vector processing and parallel execution capability, the new RISC-V CPU core targets SoCs processing large amounts of data for applications such as ADAS, AI inference and training, AR/VR, multimedia, robotics, and signal processing. AX45MPV key features and specifications: 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU) – compliant with RISC-V V-extension (RVV) 1.0 + custom extensions Supports clusters of up to 8 cores L2 cache and coherence support High bandwidth vector local memory (HVM) AndeStar V5 Instruction Set Architecture (ISA) Compliant with RISC-V GCBPV extensions Andes performance extension Andes CoDense extension for further compaction of code size Separately licensable Andes Custom Extension (ACE) for customized scalar and vector instruction 64-bit architecture for memory space […]

LiFi 802.11bb standard uses light for in-room data transmission up to 224GB/s

The 802.11bb WiFi-like standard, also called LiFi, was ratified in June 2023. It enables data transmission up to 224GB/s at a few meters range within a room using light instead of RF signals used in most other wireless standards. The technology has been worked on for many years, and we first covered (a version of) LiFi in 2014 that was still part of the IEEE 802.15 standard with speeds up to 1 Gbps. But the Light Communications 802.11bb Task Group was only formed in 2018 chaired by pureLiFi and supported by Fraunhofer HHI, and led to be ratification of the IEEE 802.11bb standard last month. In a typical LiFi setup, you’d have a LiFi-capable router connected to your local network and the Internet, a LiFi-enabled light bulb on a ceiling, and one or more LiFi receivers. From the end-user perspective, it would work like accessing a WiFi access point. We’re […]

Andes unveils AndesCore AX65 Out-of-Order RISC-V core for compute intensive applications

Andes Technology has unveiled the high-end AndesCore AX60 series out-of-order 64-bit RISC-V processors at the Linley Fall Processor Conference 2022 with the new cores designed for compute-intensive applications such as advanced driver-assistance systems (ADAS), artificial intelligence, augmented/virtual reality, datacenter accelerators, 5G infrastructure, high-speed networking, and enterprise storage. AndesCore AX65 is the first member of the family and supports RISC-V scalar cryptography extension and bit manipulation extension. It is a 4-way superscalar core with Out-of-Order (OoO) execution in a 13-stage pipeline and can fetch 4 to 8 instructions per cycle. The company further explains the AX65 core then decodes, renames, and dispatches up to 4 instructions into 8 execution units, including 4 integer units, 2 full load/store units, and 2 floating-point units. The AX65’s memory subsystem also includes split 2-level TLBs (translation lookaside buffers) with up to 64 outstanding load/store instructions. Up to eight AX65 cores (or should that then be […]

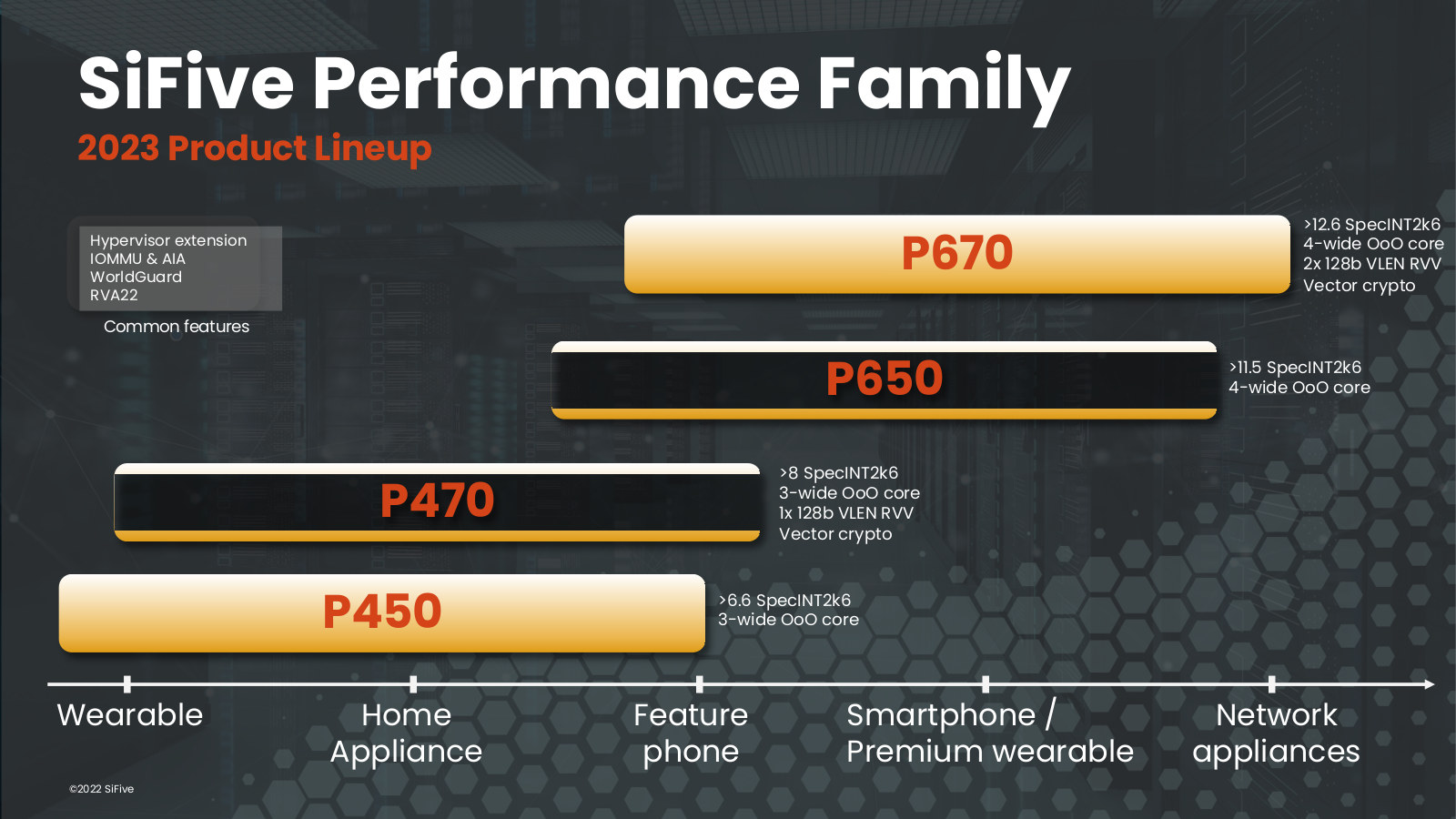

SiFive P670 and P470 RISC-V processors feature RISC-V Vector Extensions

SiFive has announced two new RISC-V Performance cores with the P670 and P470 processors with RISC-V Vector Extension for AI/ML, media and sensor processing, and designed for high volume applications such as wearables, smart home, industrial automation, AR/VR, and other consumer devices. The P670 is comparable to the Cortex-A78, and the P470 is comparable to the Cortex-A55. Both support the standardized RISC-V RVA22 profile for better OS compatibility and implement RISC-V Vector v1.0 and Vector Cryptography extensions. The SiFive Performance P470 and P670 share the following features: Full RISC-V RVA22 profile compliance Full, Out-of-Order, RISC-V Vector implementation, based on the ratified RISC-V Vector v1.0 Specification RISC-V Vector Cryptography extensions SiFive WorldGuard system security Support for virtualization, including a separate IOMMU for accelerating virtualized device IO Advanced Interrupt Architecture (AIA) compliant interrupt controller with better support for Message Signal Interrupts (MSI) and virtualization Enhanced scalability with fully coherent multi-core, multi-cluster, with […]