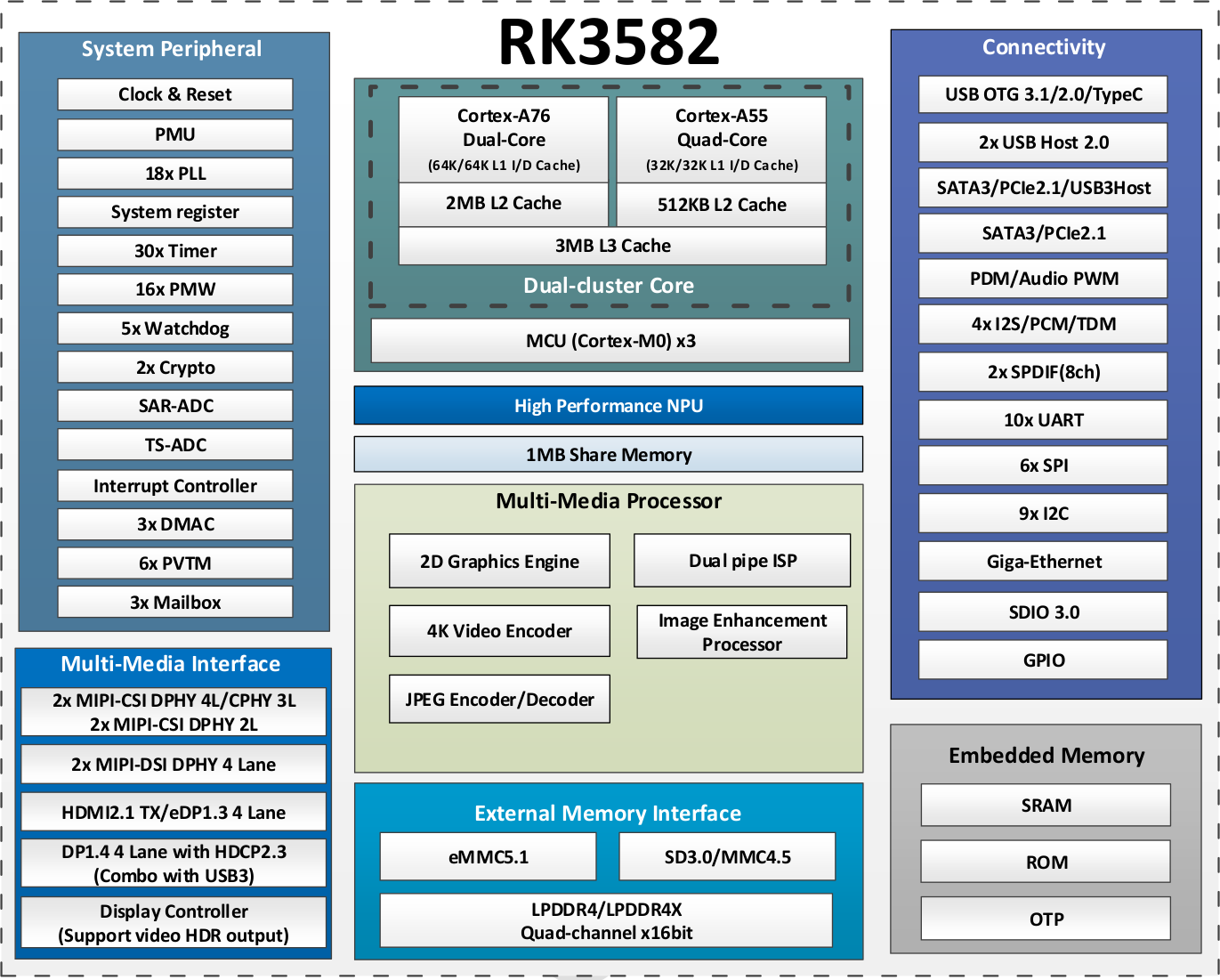

Rockchip RK3582 hexa-core SoC is pin-to-pin compatible with the popular Rockchip RK3588S octa-core Cortex-A76/A55 SoC, but only features two Cortex-A76 cores, a 5 TOPS NPU (instead of 6 TOPS) and does not come with a 3D GPU. I was first made aware of the Rockchip RK3582 in October 2023 when I was sent a photo of a board allegedly for a TV box, but while the RK3582 still features a 4K video decoder, the lack of a 3D GPU could make it problematic with 3D accelerated user interface. We now have more details with Radxa having released the datasheet and a few more interesting details. Rockchip RK3582 specifications: Hexa-core CPU – 2x Cortex-A76 and 4x Cortex-A55 cores in dynamIQ configuration (frequencies are still shown as TBD in the datasheet) GPU No 3D GPU 2D graphics engine up to 8192×8192 source, 4096×4096 destination AI Accelerator – 5 TOPS NPU 3.0 (Neural […]

Efinix Titanium Ti375 FPGA offers quad-core hardened RISC-V block, PCIe Gen 4, 10GbE

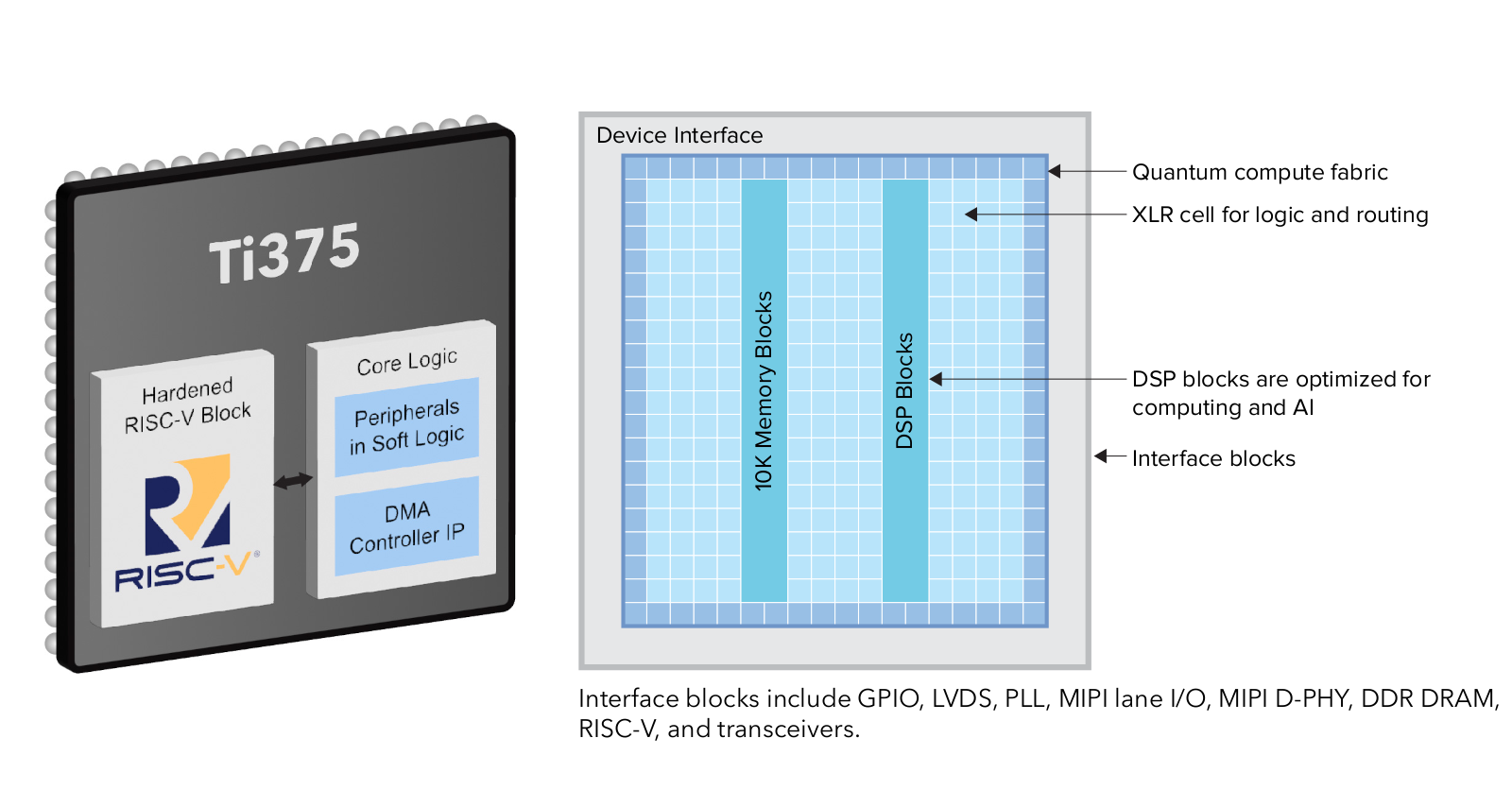

Efinix Titanium Ti375 SoC combines high-density, low-power Quantum compute fabric with a quad-core hardened 32-bit RISC-V block and features a LPDDR4 DRAM controller, a MIPI D-PHY for displays or cameras, and 16 Gbps transceivers enabling PCIe Gen 4 and 10GbE interfaces. The Titanium Ti375 also comes with 370K logic elements, 1.344 DSP blocks, 2,688 10-Kbit SRAM blocks, and 27,53 Mbits embedded memory, as well as DSP blocks optimized for computing and AI workloads, and XLR (eXchangeable Logic and Routing) cells for logic and routing. Efinix Titanium Ti375 specifications: FPGA compute fabric 370,137 logic elements (LEs) 362,880 eXchangeable Logic and Routing (XLR) cells 27,53 Mbits embedded memory 2,688 10-Kbit SRAM blocks 1,344 embedded DSP blocks for multiplication, addition, subtraction, accumulation, and up to 15-bit variable-right-shifting Memory – 10-kbit high-speed, embedded SRAM, configurable as single-port RAM, simple dual-port RAM, true dual-port RAM, or ROM FPGA interface blocks 32-bit quad-core hardened RISC-V block […]

SiFive unveils P870 high-performance core, discusses future of RISC-V

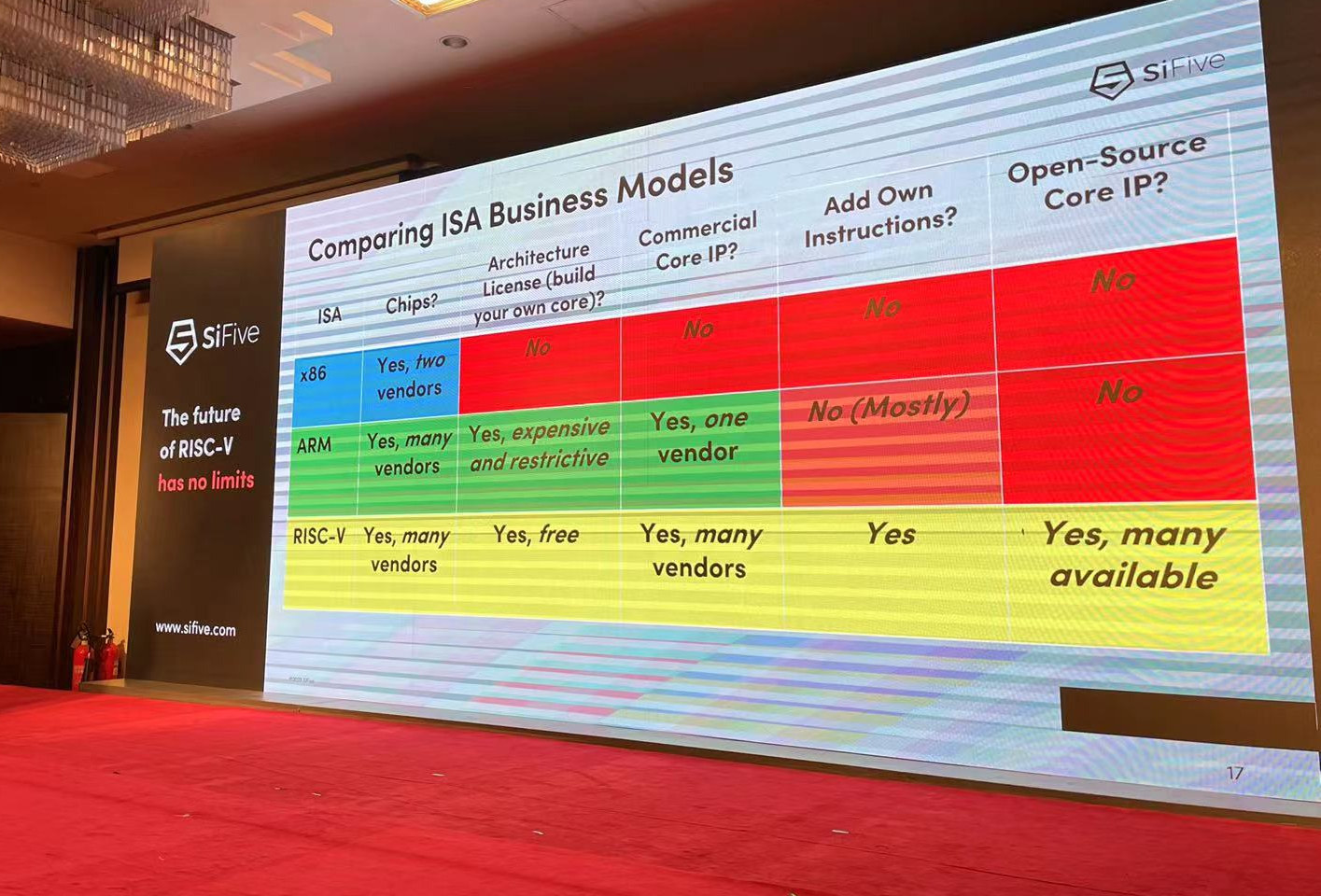

SiFive has just given a presentation at Hot Chips 2023 introducing the new high-performance P870 RISC-V core and its automotive equivalent the P870-A core, plus discussing RISC-V in general, its previous generation RISC-V cores, and what to expect going forward. SiFive has not officially announced the P870 and P870-A cores just yet, so most of the information we have from the English-speaking Internet is from ServeTheHome who managed to get some presentation slides, but this is also corroborated by various Chinese sources on Baidu and Guokr. SiFive P870 and P870-A The P870 and P870-A RISC-V cores are new cores from the SiFive Performance family compatible with the RISC-V RVA23 profile and succeeding the SiFive P670 core. The SpecINT2k6 benchmark reports 17 points per GHz on the P870 compared to 13.2 points per GHz for the P670 (comparable to the Arm Cortex-A78) or about a 29% higher performance at the same […]

DBM10 AI SoC is optimized for battery-powered voice and sensor processing

DSP Group announced DBM10 a low-power AI/ML-enabled dual-core SoC. The SoC is equipped with a DSP (Digital Signal Processor) and a dedicated nNetLite NN (Neural Network) processor that improves voice and sensor processing and ensures low-power consumption when working with sufficient-sized neural networks. Key Specifications of NN Processor Form factor: ~4 mm2 Ultra-low-power inference consumption – ~500 µW (typical) for voice NN algorithms Runs Hello Edge 30-word detection model @ 1 MHz (125 MHz available) Allows porting of large models (10s of megabytes) without significant accuracy loss using model optimization and compression. DBM10 AI SoC uses the combined functioning of machine learning, voice, and sensor parameters. This includes voice trigger (VT), voice authentication (VA), voice command (VC), noise reduction (NR), acoustic echo cancellation (AEC), sound event detection (SED), proximity and gesture detection, sensor data processing, and equalization. The DBM10 is suitable for battery-operated devices like smartphones, tablets, and wearables. It […]

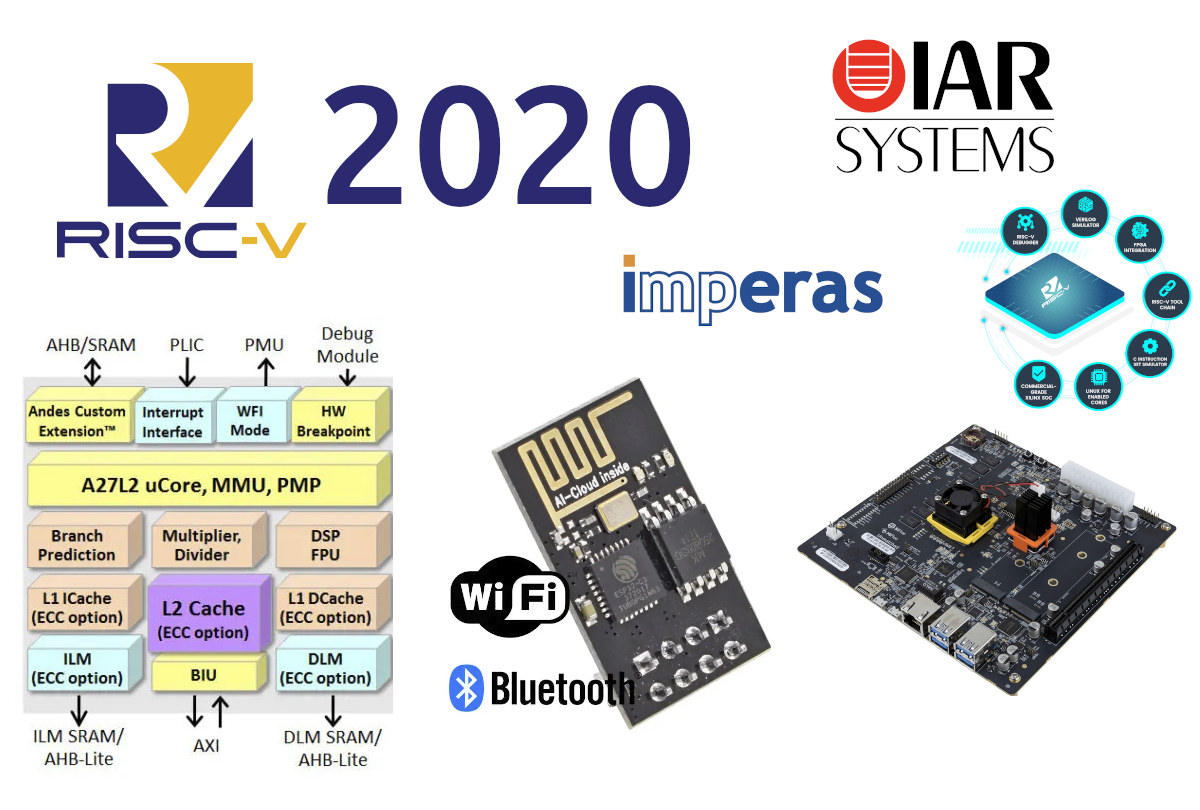

RISC-V hardware & software ecosystem highlights in 2020

The RISC-V Summit 2020 is currently taking place virtually, and RISC-V International, a non-profit corporation aiming to drive the adoption and implementation of the RISC-V instruction set architecture (ISA), took the occasion to remind us of the growth of the ISA both in terms of commercial adaption, education, and other projects. Calista Redmond, CEO of RISC-V International, detailed the growth in memberships: This year, our technical community has grown 66 percent to more than 2,300 individuals in our more than 50 technical and special interest groups. We’re seeing increased market momentum of RISC-V cores, SoCs, developer boards, software and tools across computing from embedded to enterprise … We’re proud of our growing global membership, which has more than doubled in the last year to 1,000 total members, including 222 organizations.” RISC-V also launched the RISC-V Exchange now listing over 124 RISC-V cores, SoCs, and developer boards, as well as 129 […]

zGlue Launches the Open Chiplet Initiative in Collaboration with Google and Antmicro

We first covered zGlue’s ZiP (zGlue Integration Platform) in 2018 as the company introduced its multi-chip module similar to SiP (system-in-package) via a crowdfunding campaign. Just like SiP, the technology packages several components into a single package, but costs have been brought down to enable low-volume production of custom chips for a reasonable price. Since then the company announced new ZiP multi-chip modules such as nRF52832 based Omnichip and the FPGA, Arm or/and RISC-V based GEM ASIC by Antmicro. The company recently announced the Open Chiplet Initiative, a collection of open-source designs, tools and file formats, launched in collaboration with Google and Antmicro. There are four main types of tools within the Open Chiplet Initiative: Open Chiplet Interfaces – Currently only ZEF (zGlue Chiplet Info Exchange Format) is provided. It defined the part numbers, pins, and mechanical dimensions of various parts. The ZEF specification can be found on Github. Design […]

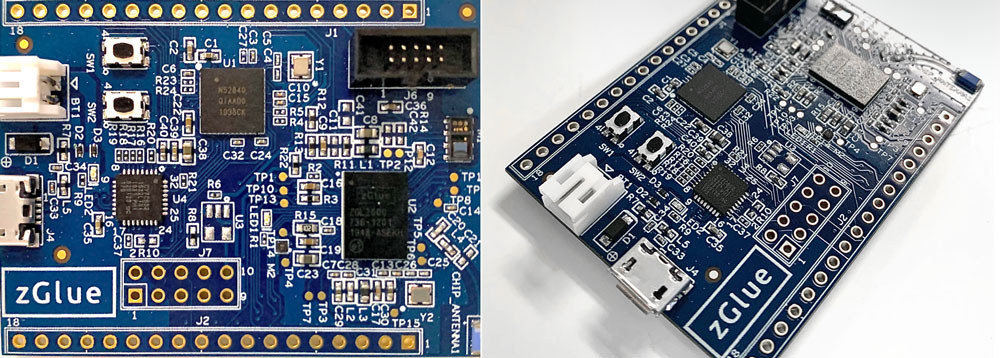

Omnichip Devkit 2 Features Nordic nRF52832 based zGlue ZiP Multichip Module

We first covered zGlue Integration Platform (ZiP) in 2018 when the company introduced its chip-stacking technology with a fitness tracker based on ZGZL1BA ZiP equipped with chips from Dialog Semiconductor, Analog Devices, Macronix, MCube and others. The concept is similar to SiP (System-in-Package), but zGlue claims the costs and lead times are much lower with the technology. Earlier this year, ZiP was back in the news thanks to Antmicro GEM custom RISC-V/Arm ASIC, and today, I was informed about zGlue Omnichip devkit 2 that is equipped with a ZiP of the same name, and that can be used to evaluate the technology. zGlue OmniChip ZiP zGlue OmniChip ZiP is a multichip module with the following ICs (aka Chiplets) and specifications: Nordic Semiconductor nRF52832 Cortex-M4F microcontroller with Bluetooth LE and NFC connectivity Texas Instruments BQ25120AYFPR battery charger, buck regulator Maxim Integrated MAX86140ENP+ optical pulse oximeter Texas Instruments TMP108AIYFFR temperature sensor Bosch […]

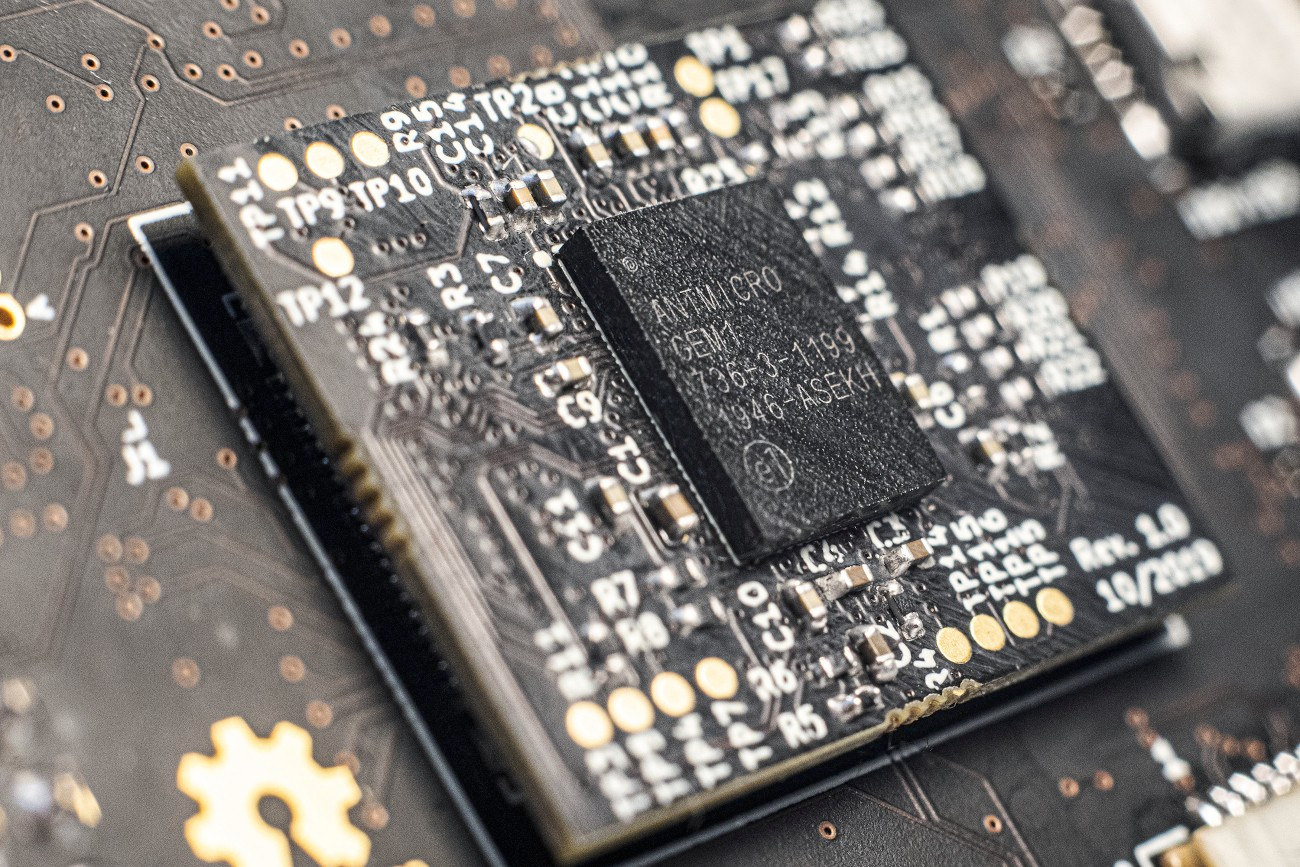

Antmicro GEM ASIC Leverages zGlue Technology to Quickly Bring Custom Arm/RISC-V SoC’s to Market

Introduced in 2018, ZiP (zGlue Integration Platform) chip-stacking technology aims to produce chips similar to Systems-in-Package (SiP) but at much lower costs and lead times. We first found it in a Bluetooth tracker featuring ZGLZ1BA custom chip manufactured with zGlue technology and integrating an Arm Cortex-M0 MCU, flash memory and sensors into a single package. But now the technology is back in the news with Antmicro announcing GEM chiplet-based ASIC last December. At the time of the announced the company’s GEM1 chip featured two Lattice iCE40 FPGAs with a MIPI CSI-2 switch, and they had started working on GEM2 chip combining a hard RISC-V processor and Lattice iCE40 FPGA. Those are so-called demonstrators chip as Antmicro customers will be able to easily and quickly design their own 6×9 mm chip(s) with RISC-V and/or ARM CPUs, FPGAs, sensors, radios and other functional elements to meet the requirements of their specific applications. […]