Microchip has recently released the SAMA7D65 MPU, a high-performance Arm Cortex-A7 embedded processor designed for HMI and connectivity applications across industrial, home, medical, and appliance markets. The MPU is available in both System-in-Package (SiP) and System-on-Chip (SoC) variants and features various display interfaces, including MIPI DSI, LVDS, and 8-bit Serial RGB interfaces, along with a 2D GPU for graphical acceleration. Memory and storage options include support for 16-bit DDR2/DDR3/DDR3L and LPDDR2/3 memory, optional 1 Gbit or 2 Gbit DDR3 RAM, NAND Flash, eMMC Flash, and SD card. It features dual Gigabit Ethernet with TSN support, an I3C controller, five CAN-FD interfaces, and three high-speed USB ports. Additionally, it comes with various security features, including physically unclonable function (PUF), secure boot, key storage, and cryptographic accelerators for AES, SHA, RSA, and ECC. Microchip SAMA7D65 SoC/SiP specifications: CPU – Arm Cortex-A7 core up to 1 GHz Arm TrustZone, NEON, FPU 32KB L1 I-cache […]

Wiznet W55RP20-EVB-Pico board features W55RP20 SiP with W5500 Ethernet controller and RP2040 MCU

Wiznet has recently released the W55RP20-EVB-Pico dev board, a compact board based around the W55RP20 SiP that fuses the Raspberry Pi RP2040 MCU and the W5500 Ethernet controller into a single IC, plus a 2MB flash chip for firmware storage. Just last month we wrote about W5100S-EVB-Pico2 and W5500-EVB-Pico2 dev boards, both the boards have a newer Raspberry Pi RP2350 MCU and external Ethernet controller (W5500 or W5100S). The RP2350 offers additional security features such as One Time Programmable (OTP) memory, secure boot, and Arm TrustZone technology, making it more suitable for secure applications. The W55RP20 on the other hand integrates a W5500 Ethernet controller and the RP2040 in a single SiP which is also pin-compatible with the Raspberry Pi Pico, making it easy to use existing Pico accessories and code examples. W55RP20-EVB-Pico dev board specifications: SiP– W55RP20 microcontroller MCU – Raspberry Pi RP2040 Core– Dual Cortex M0+ cores up […]

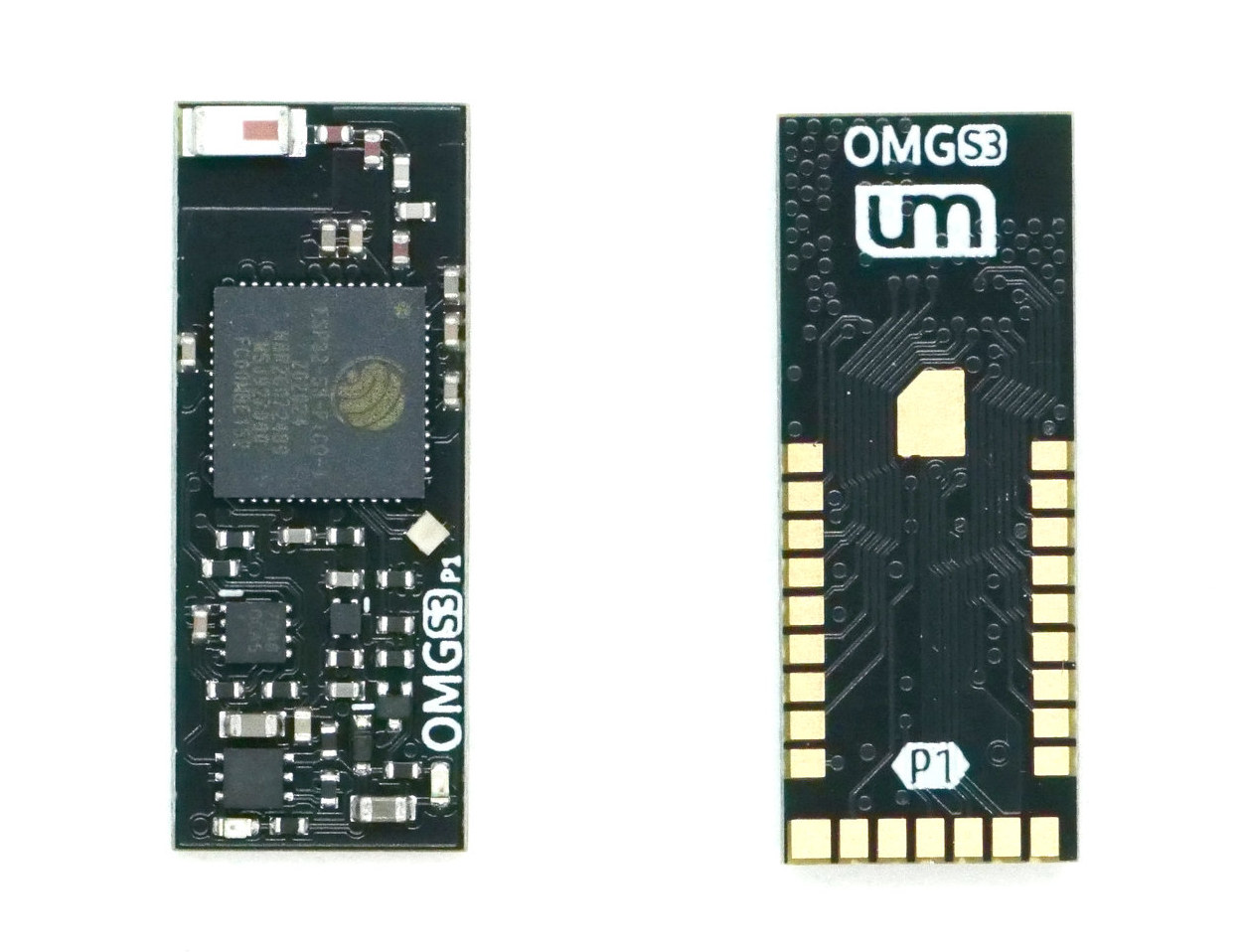

ESP32-S3-PICO-based OMGS3 is the world’s smallest fully-featured ESP32-S3 module/board

Based on the ESP32-S3-PICO system-in-package (SiP), Unexpected Maker OMGS3 is a small, yet full-featured ESP32-S3 module/board whose designer claims is the world’s smallest in its category at just 25x10mm in size. It replaces the earlier Unexpected Maker NanoS3 based on the ESP32-S3FN8 SoC measuring 28 x 11 mm. The OMGS3’s ESP32-S3-PICO SiP integrates a dual-core ESP32-S3 WiFi and BLE wireless SoC, 8MB QSPI flash, and 2MB QSPI PSRAM. The board itself also includes a 3D antenna, an RGB LED, two LEDs for power and charging, and I/Os are exposed through 26 solder pads. Unexpected Maker OMGS3 specifications: SiP – Espressif ESP32-S3-PICO SoC ESP32-S3 dual-core Tensilica LX7 up to 240 MHz with 512KB SRAM, 16 KB RTC SRAM Wireless – WiFi 4 and Bluetooth 5 LE + Mesh Memory – 2MB QSPI PSRAM Storage – 8MB QSPI flash Antenna – High-gain 3D antenna I/Os via 26x solder pads Up to 17x GPIO […]

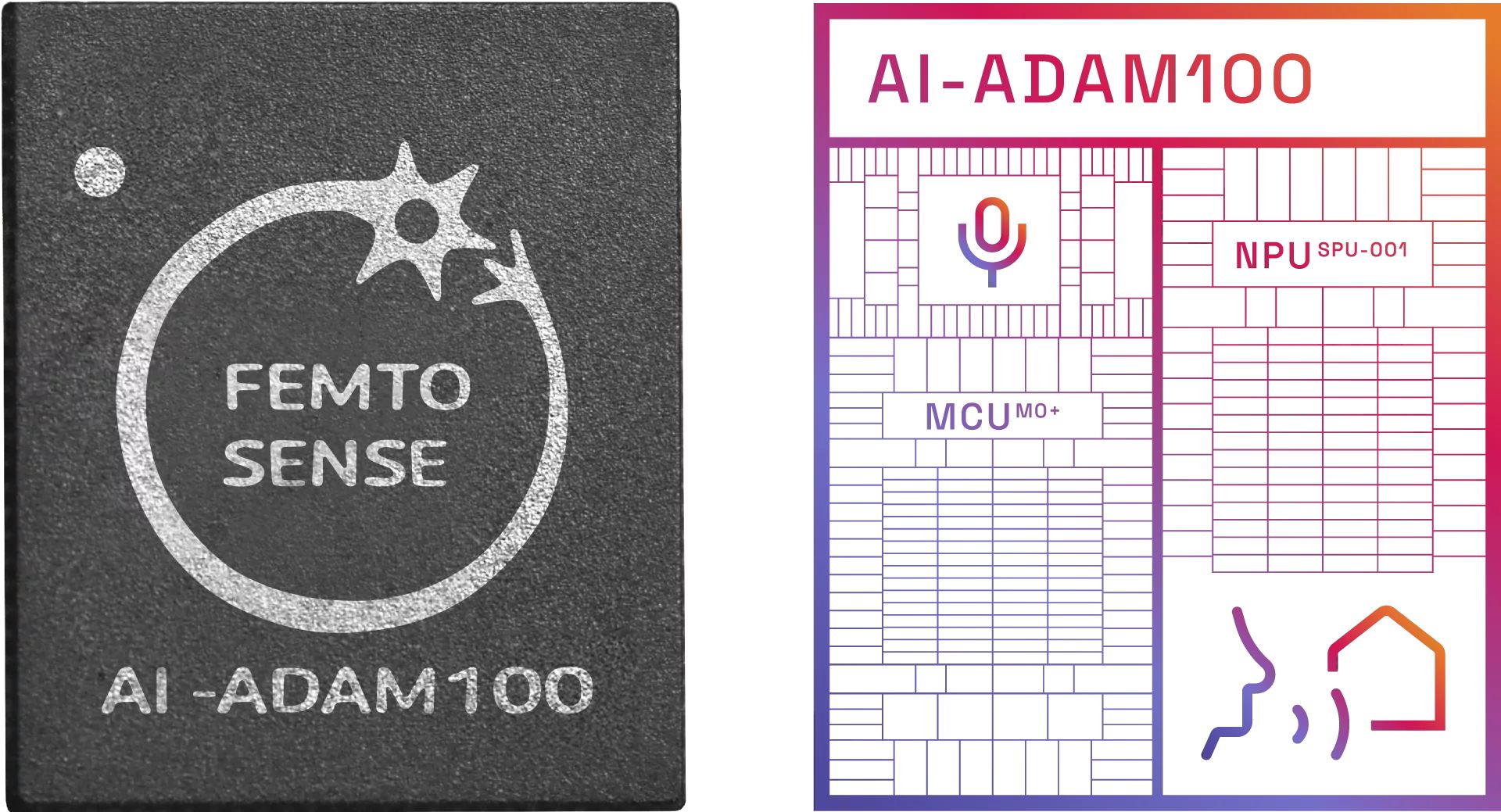

Femtosense introduces the AI-ADAM-100 system-in-package for affordable, efficient AI-based voice processing on the edge

Femtosense’s newest release, the AI-ADAM-100, combines a low-power Arm Cortex M0+ microcontroller from ABOV Semiconductor with the Femtosense Sparse Processing Unit (SPU), an in-house neural processing unit. This combination powers AI voice processing and cleanup capabilities on edge devices. It leverages sparsity techniques to ensure that models can run on edge devices without intensive processing. Sparsity in AI refers to the presence of zeroes or non-zero values in the matrices and tensors used in machine learning models. No computation is required for these zero weights, heavily reducing processing requirements. The Femtosense AI-ADAM-100 aims to bring voice control to various devices such as home appliances, hearing aids, industrial headsets, and consumer earbuds. These appliances can implement voice user interfaces that allow users to talk naturally in their own words. On-device voice cleanup functionality would reduce infrastructure costs and improve the accuracy of the data sent to the cloud. The Femtosense SiP […]

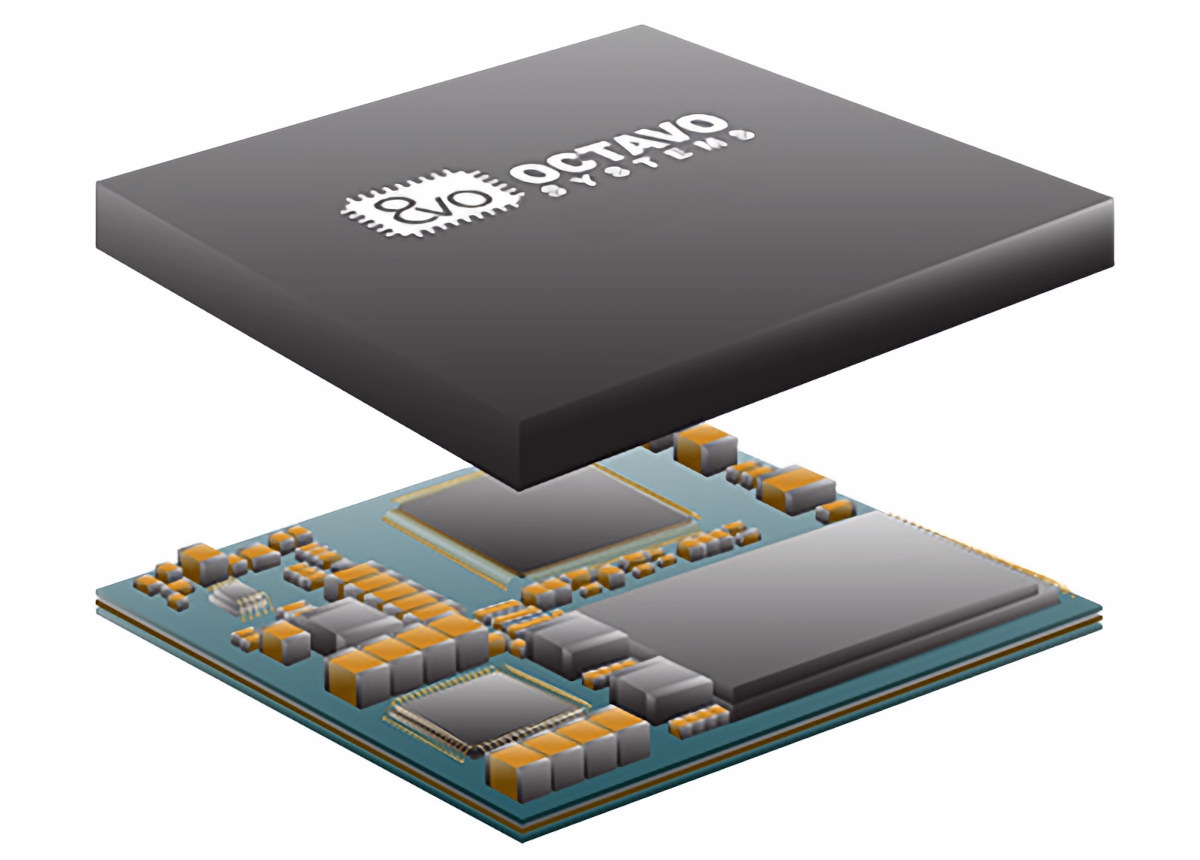

Octavo OSD32MP2 System-in-Package (SiP) packs an STM32MP25 SoC, DDR4, EEPROM, and passive components into a single chip

Octavo Systems OSD32MP2 is a family of two System-in-Package (SiP) modules, comprised of the OSD32MP2 and OSD32MP2-PM, based on the STMicro STM32MP25 Arm Cortex-A35/M33 AI processor, DDR4 memory, and various components to reduce the complexity, size, and total cost of ownership of solutions based on the STM32MP2 chips. The OSD32MP2 is a larger, yet still compact, 21x21mm package with the STM32MP25, DDR4, EEPROM, oscillators, PMIC, passive components, and an optional RTC, while the OSD32MP2-PM is even smaller at 14x9mm and combines the STM32MP25, DDR4, and passive components in a single chip. OSD32MP2 specifications: SoC – STMicro STM32MP25 CPU – Up to 2x 64-bit Arm Cortex-A35 @ 1.5 GHz MCU 1x Cortex-M33 @ 400 MHz with FPU/MPU; 1x Cortex M0+ @ 200 MHz in SmartRun domain GPU – VeriSilicon 3D GPU @ 900 MHz with OpenGL ES 3.2 and Vulkan 1.2 APIs support VPU – 1080p60 H.264, VP8 video decoder/encoder Neural […]

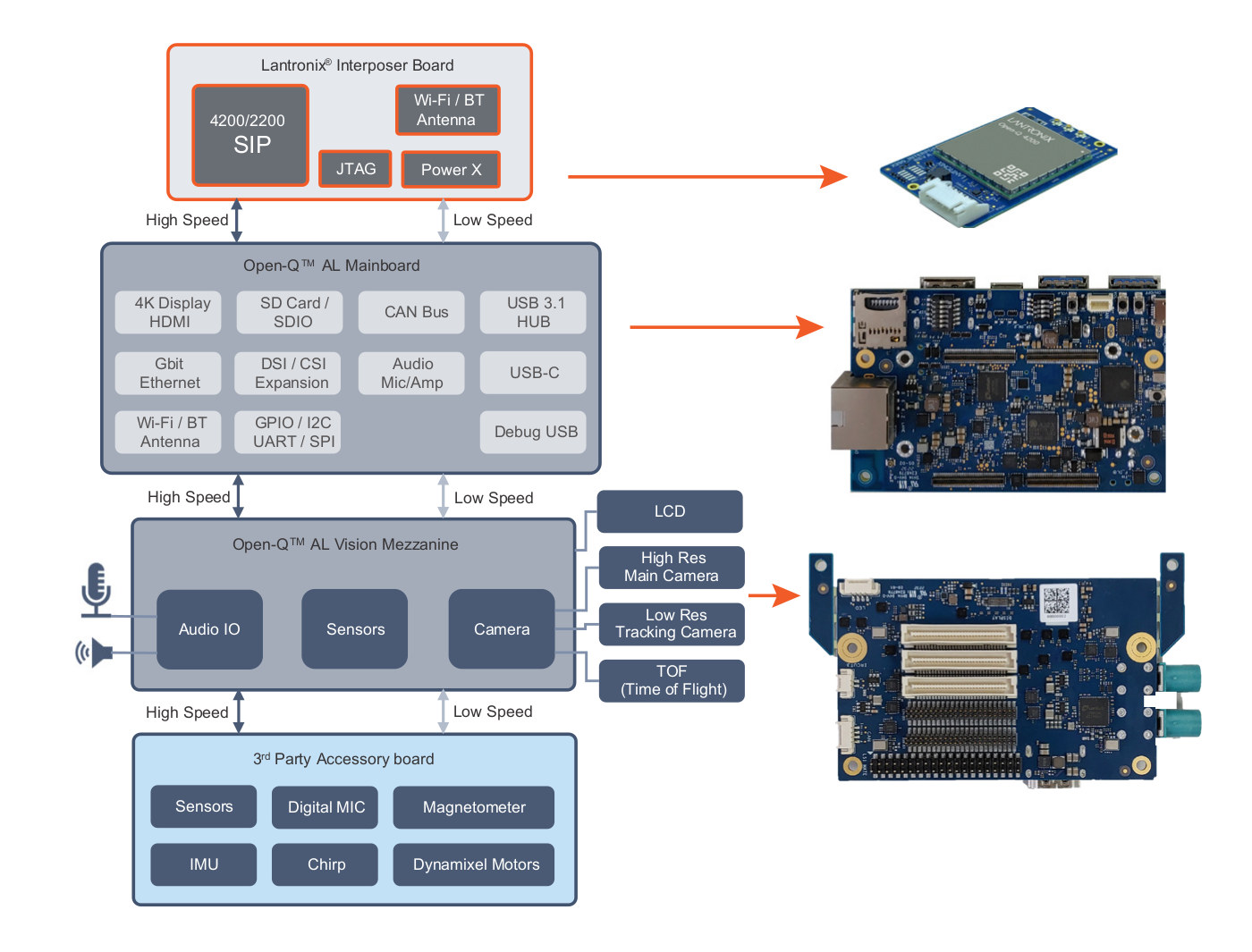

Lantronix Open-Q 2210RB and 4210RB SiPs for robotics power RB1/RB2 development kit

What comes after Qualcomm Robotics RB3, RB5, and RB6 platforms? Apparently, it’s Qualcomm Robotics RB1 and RB2 platforms powered by Qualcomm QRB2210 and Qualcomm QRB4210 processors respectively and optimized for cheaper, smaller robots with lower power consumption. But Qualcomm is one of the lamest companies known to man, so they did not include any photos when announcing the Robotics RB1 and RB2 platforms, so I’ll focus this post on Lantronix Open-Q 2210RB and 4210RB system-in-packages (SiP) based on the same processors, as well as the Open-Q RB1/RB2 development kit. Open-Q 2210RB and 4210RB SiP The new system-in-packages are very similar to the earlier Open-Q 2290CS and 4290CS SIPs for industrial IoT and machine vision applications, with the only difference being the Qualcomm processor used, so I invite you to read the earlier post for the full details, and I’ll just provide summaries here. Open-Q 2210RB key features: SoC – Qualcomm […]

Qualcomm-based Open-Q 2290CS and 4290CS SIPs target industrial IoT and machine vision applications

Lantronix has just unveiled two new System-in-Packages (SiP) with the entry-level Open-Q 2290CS SIP based on Qualcomm QCS2290 quad-core Cortex-A53 processor designed for industrial IoT applications and safety vehicle equipment control, and the pin-compatible, mid-range Open-Q 4290CS SIP based on Qualcomm QCS4290 octa-core Kryo 260 CPU for applications requiring artificial intelligence and machine learning capabilities. The Open-Q 2290CS module comes with 2GB LPDDR4, 16GB eMMC flash, WiFi 5 and Bluetooth 5.0 connectivity, while the Open-Q 4290CS module is equipped with up to 6GB LPDDR4, up to 256GB eMMC flash., and Wi-Fi 5 with some Wi-Fi 6 features (TWT & 8SS), and Bluetooth 5.1. Lantronix also offers the Open-Q AL2 development kit supporting either both SIP modules for evaluation and rapid prototyping. Open-Q 2290CS – Qualcomm QCS2290 SiP Specifications: SoC – Qualcomm QCS2290 quad-core Cortex-A53 processor at up to 2.0 GHz with Adreno 702 GPU at 845 MHz with support for […]

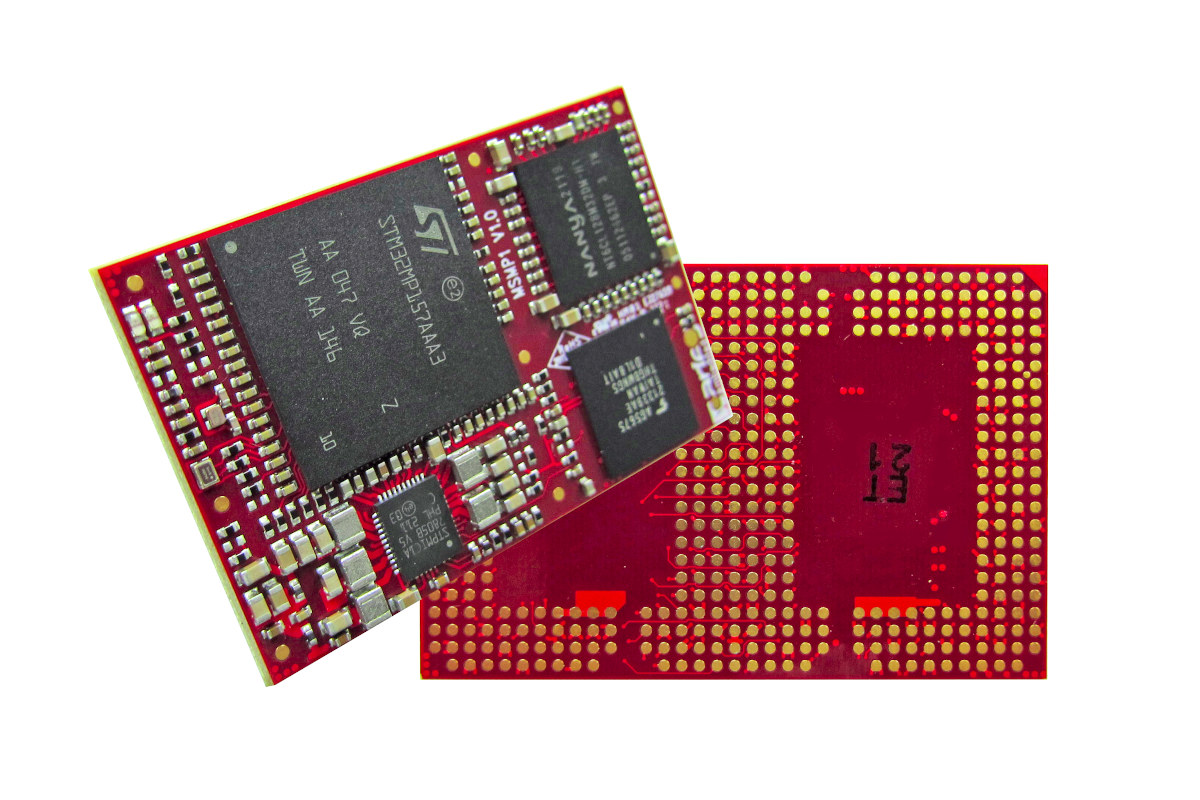

OSM Size M SiP Integrates STM32MP1 MPU for industrial & IoT applications

ARIES Embedded MSMP1 OSM-compatible system-in-package (SiP) based on STM32MP1 CortexA7/M4 microcontroller for Industrial and IoT applications follows the company’s MSRZG2UL and MSRZFive OSM-compatible SiPs with Renesas Arm or RISC-V microprocessor introduced a few months ago. But instead of coming in the ultra-compact 30×30 mm OSM Size S form factor, the new MSMP1 complies with the larger 45x30mm OSM Size M form factor with a total of 476 contacts to allow for more I/Os. The SiP also integrates 512 MB to 4 GB DDR3L RAM, and 4 to 64 GB eMMC flash. MSMP1 SIP specifications: SoC – STMicro STM32MP1 single or dual-core Arm Cortex-A7 processor up to 800MHz, with Arm Cortex-M4 real-time core up to 209MHz, Vivante GPU compatible with OpenGL ES 2.0 System Memory – 512MB – 4GB DDR3L RAM Storage – 4GB – 64GB eMMC NAND Flash 476-contact LGA with Networking – Gigabit Ethernet USB – USB 2.0 Host/OTG […]