SiFive has recently announced their Core IP 7 Series of RISC-V cores offering better performance, and designed to enable “embedded intelligence” in applications such as 5G, networking, storage, augmented reality, artificial intelligence, SLAM, and sensor fusion. Three families of the new 7 Series been launched with namely SiFive E7, S7 and U7 Core IP Series, so let’s have a look at each of them. E7 Core IP Series – E76 and E76-MC Cores The E7 Core IP Series comprises the 32-bit E76 and E76-MC (Multi-core), provides hard real-time capabilities, and compares to Arm’s Cortex M7, Cortex-R7/R8 cores. E76-MC Key Features Fully compliant with the RISC-V ISA specification 4x RV32IMAFC E76 Cores Machine and User Mode Support In-order, 8-stage pipeline Advanced Memory Subsystem 32KB Instruction Cache 32KB Instruction Tightly Integrated Memory (ITIM) 32KB Data Cache 32KB FIO RAM 256KB L2 Cache High-performance TileLink Interface Benchmark Scores- 2.3 DMIPS/MHz, 4.9 CoreMark/MHz E76 […]

SiFive Announces E20 and E21 RISC-V Cores for IoT and Wearables

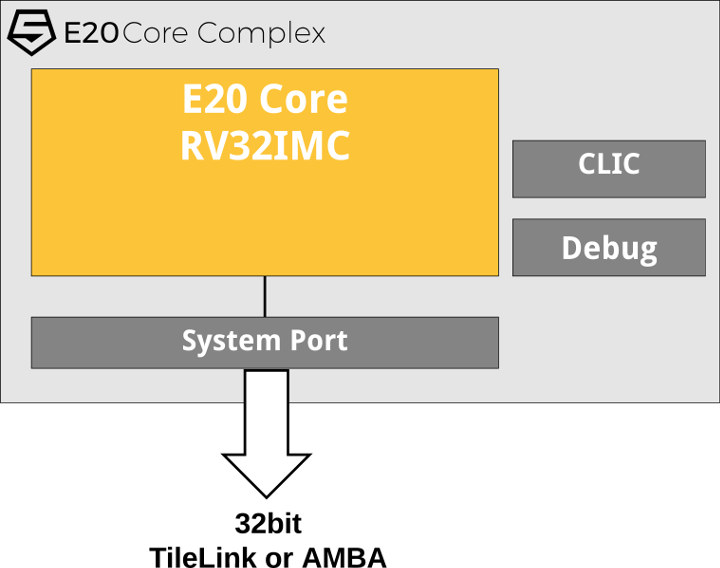

SiFive has just announced the availability of their new E2 Core IP Series low-area, low-power microcontroller cores designed for use in embedded devices. Two standards cores are currently part of the new family: E21 providing mainstream performance for MCUs, sensor fusion, minion cores and smart IoT markets E20, the most power-efficient SiFive standard core designed for microcontrollers, IoT, analog mixed signal and finite state machine applications SiFive E20 MCU Core SiFive E20 Standard Core IP Key Features: RISC-V ISA – RV32IMC Machine Mode only 2-stage pipeline System Port for external memory accesses Core Local Interrupt Controller (CLIC) with 32 interrupts Advanced debug with 4 hardware breakpoints/watchpoints Performance – 1.1 DMIPS/MHz; 2.4 CoreMark/MHz Power / Clock / Area 28nm HPC – 0.58 mW; 725 MHz and up; 0.023 mm2 55nm LP – 1.3 mW; 250 MHz and up; 0.064 mm2 The company compares E20 core to Arm Cortex-M0+ core in the […]

HiFive Unleashed RISC-V Linux Development Board Gets a $2000 FPGA Expansion Board

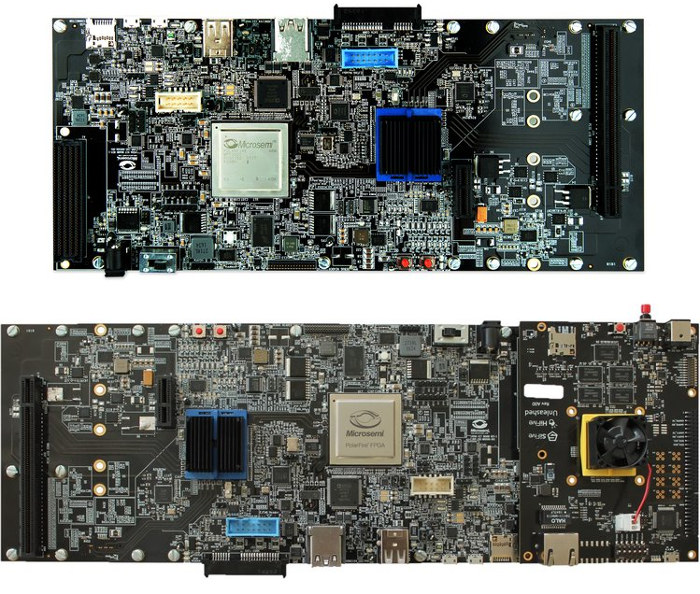

If you’re a RISC-V architecture’s enthusiast or represent a company working on products with the new ISA, you may have spent $999 or more on Hifive Unleashed RISC-V Linux development board a few months ago. You now have the opportunity to spend an extra $1,999 for HiFive Unleashed Expansion Board powered by a MicroSemi PolarFire FPGA programmed with a PCIe root port bridge, and allowing you to test all sorts of peripherals such as HDD’s & SSD’s, HDMI output, and audio cards, network adapters, graphics cards, and so on. Expansion board specifications: FPGA – Microsemi Low Power PolarFire FPGA with 300K Logic Element 4 Gbit DDR4 x16 SPI Flash for remote FPGA updates, QSPI Flash connected to GPIO 24 lane PCIe Switch x1 PCI Express card connector x16 PCI Express card connector with 4 lanes of PCIe gen2 connected SSD M.2 connector SATA connector HDMI connector eMMC Nand Flash uSD […]

SiFive Partners with Western Digital to Produce 1 Billion RISC-V Cores

Architecture like Arm and x86 are well established, and initiatives like RISC-V opens source ISA have potential, but market acceptance and commercial success are not guaranteed. But RISC-V just got a big boost, as SiFive announced it raised $50.6 million in a Series C round from existing and new investors, as well as strategic partners such as Huami, SK Telecom and Western Digital. Even more importantly, Sifive and Western Digital signed a multi-year license for the Freedom Platform, with Western Digital pledging to produce 1 billion RISC-V cores. The announcement does not explicitly mention which Freedom platform, but Western Digital statement makes it quite clear they’ll use one of the more powerful (and Linux capable) core: RISC-V delivers a platform for innovation unshackled from the proprietary interface of the past. This freedom allows us to bring compute closer to data to optimize special purpose compute capabilities targeted at Big Data and […]

RISC-V Keynote at Embedded Linux Conference 2018 (Video)

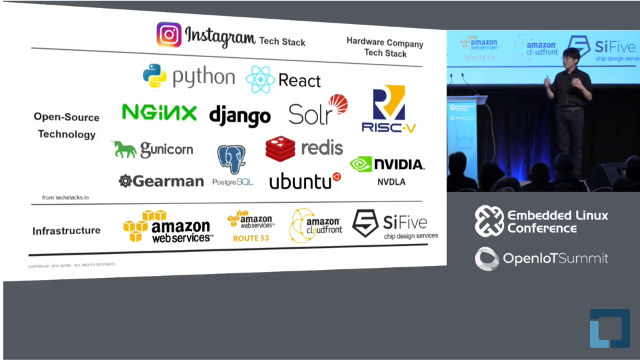

The Embedded Linux Conference and OpenIoT Summit 2018 have just started, and the Linux Foundation has already uploaded a few keynote videos to YouTube, including the one by Yunsup Lee, Co-Founder and CTO, SiFive, entitled “Designing the Next Billion Chips: How RISC-V is Revolutionizing Hardware”. Yunsup explains the current problem with chip development, and go through the open source RISC-V solutions offered by Sifive. Currently design a chip has a high upfront (NRE = non-recurring engineering) costs, is time-consuming (1.5 to 2 years at least) and silicon vendors normally target high volume production, but now many applications like IoT or machine learning require custom chips that may not be (yet) manufactured in such high volume. The solution is to adapt some idea from open source software to open source hardware in order to lower the costs, enable fast prototyping, and involve the community of designers and software developers. He took […]

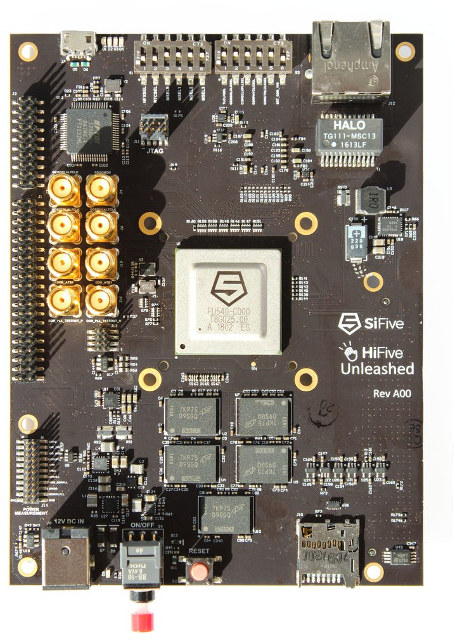

SiFive Introduces HiFive Unleashed RISC-V Linux Development Board (Crowdfunding)

RISC-V free and open architecture has gained traction in the last couple of years. SiFive has been one of the most active companies with RISC-V architecture, introducing Freedom U500 and E500 open source RISC-V SoCs in the summer of 2016, before launching their own HiFive1 Arduino compatible board, and later the official Arduino Cinque board. That’s fine if you are happy with MCU class boards, but RISC-V is getting into more powerful processors, and recently got initial support o Linux 4.15, so it should come as no surprise the company has now launched HiFive Unleashed, the first RISC-V-based, Linux-capable development board. HiFive Unleashed key features and specifications: SoC – SiFive Freedom U540 with 4x U54 RV64GC application cores @ up to 1.5GHz with Sv39 virtual memory support, 1x E51 RV64IMAC Management Core, 2 MB L2 cache; 28 nm TSMC process System Memory – 8GB DDR4 with ECC Storage – 32MB […]

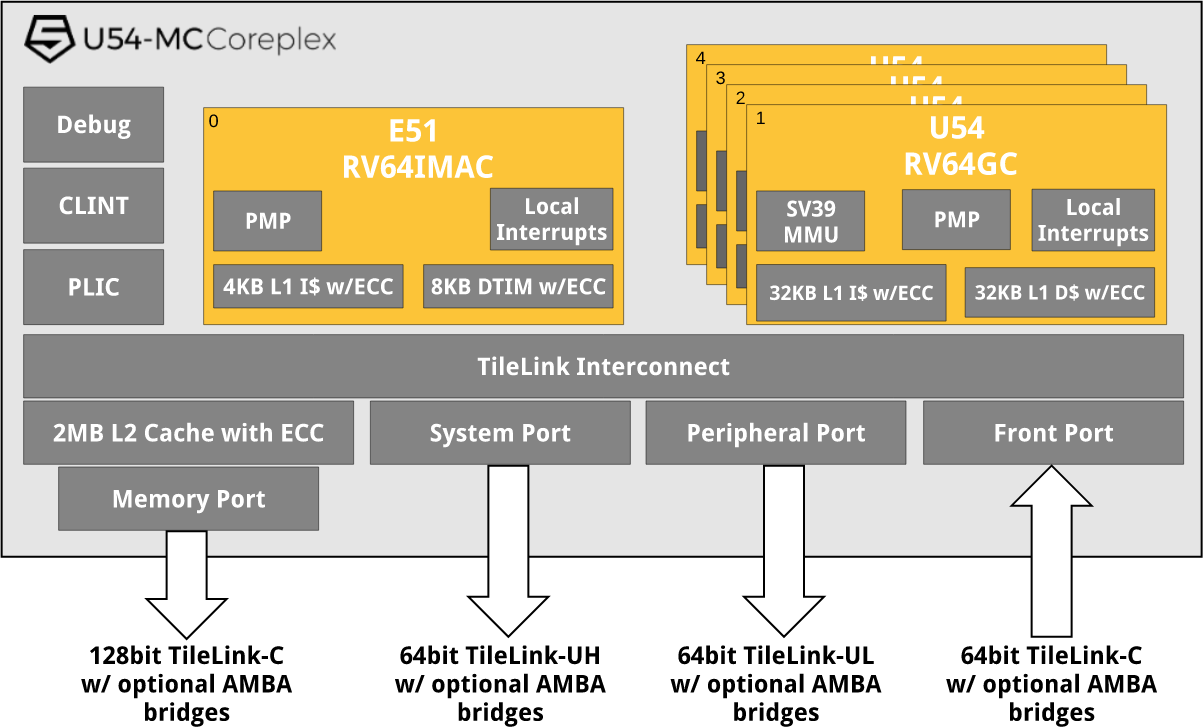

SiFive U54-MC Coreplex is the First Linux Ready RISC-V based 64-bit Quad-Core Application Processor

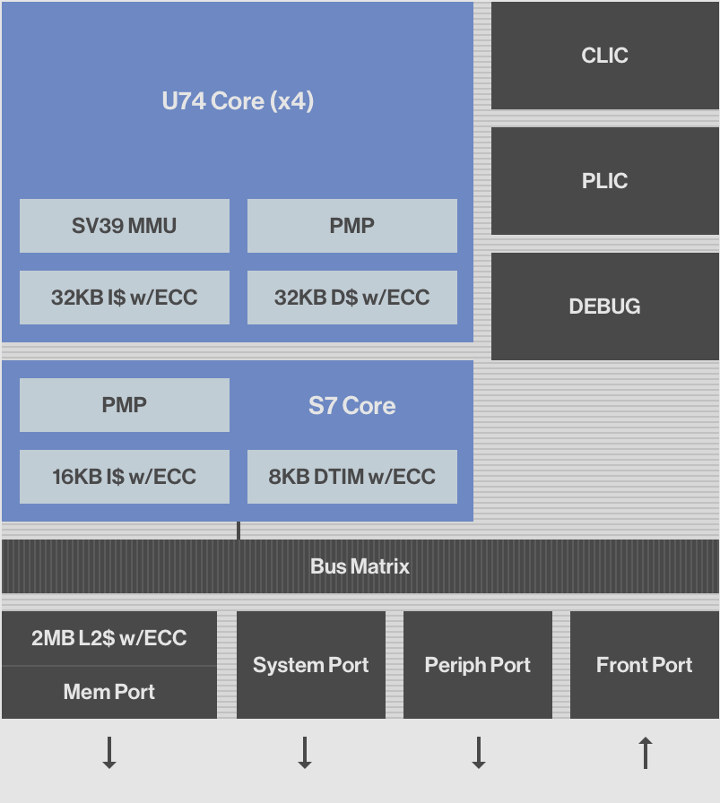

We first covered SiFive when they unveiled their open source Freedom RISC-V SoCs. Since then, they moved away from open source for their customizable IP, since their customers did not require fully open source designs, but kept releasing more RISC-V cores such as 32-bit E31 Coreplex & 64-bit E51 Coreplex, as well as offering their one-time fee pricing without recurring royalties, contrary to what some competitors – such as Arm – are doing. The company has now just announced U54-MC Coreplex quad core real-time capable application processor with support for full featured operating systems such as Linux. U54-MC Coreplex main specifications / features: Fully compliant with the RISC-V ISA specification 4x RV64GC U54 Application Cores 32KB L1 I-cache with ECC, 32KB L1 D-cache with ECC 8x Region Physical Memory Protection 48x Local Interrupts per core Sv39 Virtual Memory support with 38 Physical Address bits 1x RV64IMAC E51 Monitor Core 4KB […]

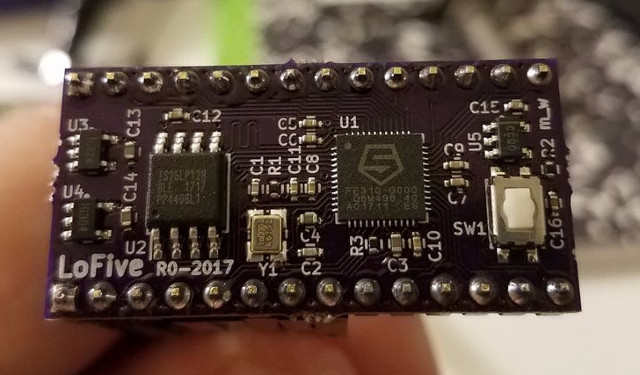

LoFive is a Tiny Open Source Hardware Board based on SiFive FE310 RISC-V Open SoC

Do you remember HiFive1? It’s an Arduino compatible board based on the SiFive FE310 open source RISC-V SoC. Michael Welling has now started working on LoFive board using the same processor, but in a much smaller & breadboard friendly form factor. LoFive board specifications: MCU – SiFive Freedom E310 (FE310) 32-bit RV32IMAC processor @ up to 320+ MHz (1.61 DMIPS/MHz) Storage – 128-Mbit SPI flash (ISSI IS25LP128) Expansion – 2x 14-pin headers with JTAG, GPIO, PWM, SPI, UART, 5V, 3.3V and GND Misc – 1x reset button, 16 MHz crystal Power Supply – 5V via pin 1 on header; Operating Voltage: 3.3 V and 1.8 V Dimensions – 38 x 18 mm (estimated) The board will be programmable with Arduino IDE + Cinco just like HiFive1 board. The board is also open source hardware, so beside the aforelinked info on Hackster,io, you’ll also find the KiCAD schematics, PCB layout, and […]