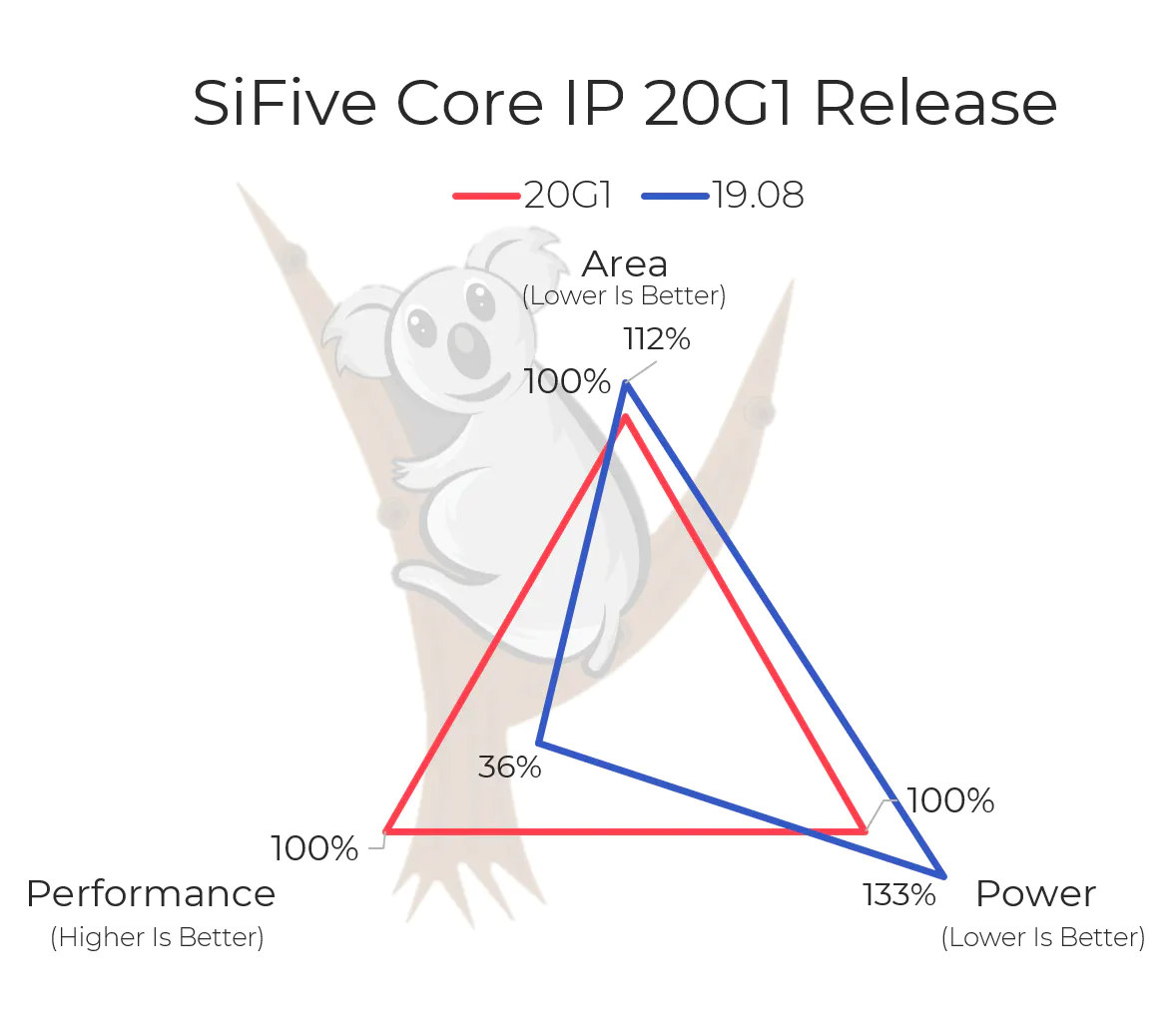

SiFive RISC-V cores portfolio ranges from low power 32-bit IoT processors to more powerful, Linux-capable 64-bi RISC-V cores like the latest SiFive U84/U87 cores rivaling with Arm Cortex-A7x cores. SiFive Core IP 20G1 release further enhances the company’s existing RISC-V cores with performance improvements, higher efficiency, and a smaller footprint. Specifically, SiFive claims the SiFive U7-Series has increased load bandwidth up to 2.8x for memory-intensive workloads such as AI inference processing, and all of the company’s RISC-V cores can now run at lower power, with the SiFive U74 standard core running at up to 25% lower power while running Dhrystone benchmark. The SiFive E-Series processors which feature real-time capability are now available with the RISC-V Embedded extension (RV32E) which reduces the footprint compared to RV32I ISA with for instance up to 11% smaller area for the SiFive E3-Series. RV32E and RV32I have the same instructions set, but RV32E comes with […]

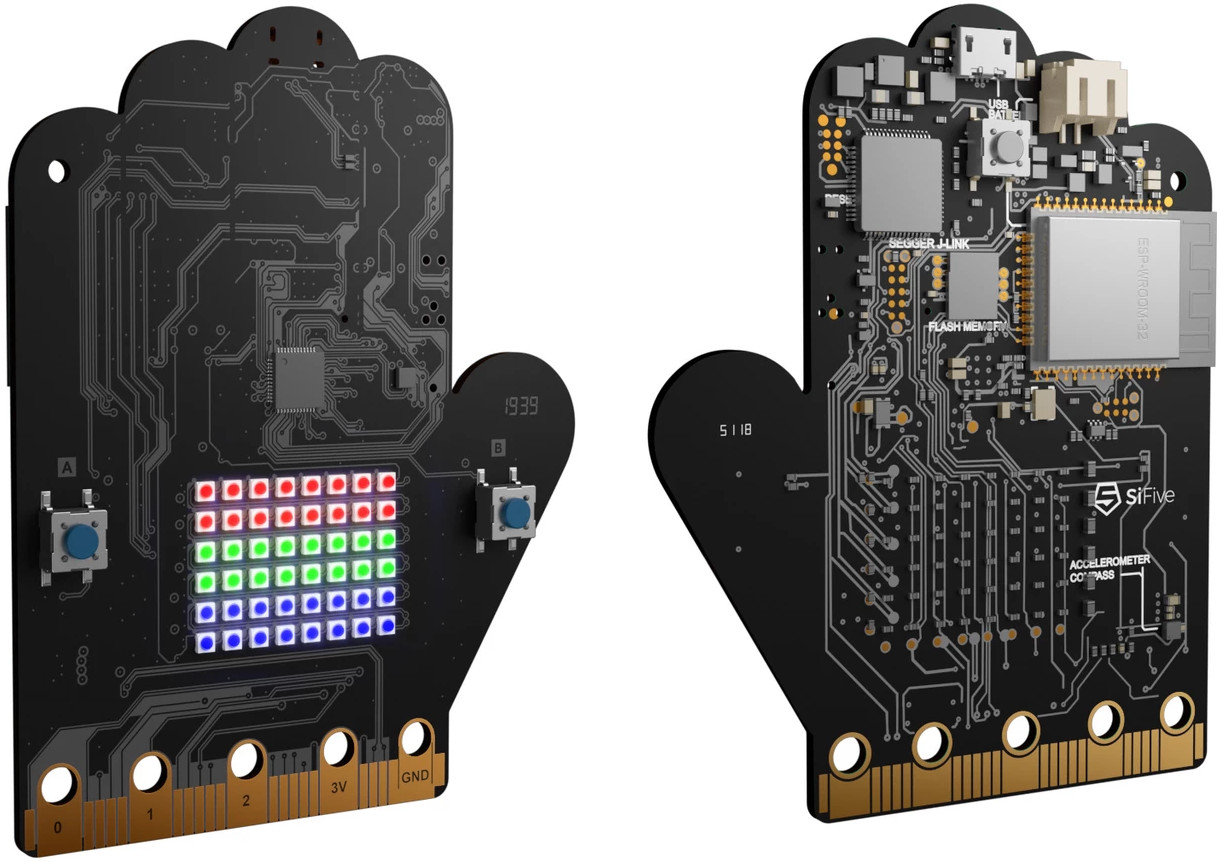

SiFive Learn Inventor is a Wireless RISC-V Development Kit Inspired by BBC Micro:bit

SiFive Learn Inventor is a RISC-V educational board partially inspired by BBC Micro:bit board with the same crocodile clip-friendly edge connector, and an LED matrix. The board is also fully qualified to work with the Amazon FreeRTOS real-time operating system. Shaped in the form of a hand, the board features SiFive FE310 RISC-V processor found in the SiFive HiFive1 board, as well as ESP-WROOM-32 WiFi + Bluetooth module. SiFive Learn Inventor specifications: SoC – SiFive FE310-G003 32-bit RISC-V (RV32IMAFC) processor @ 150 MHz with 64KB of internal SRAM Storage – 512 KB flash “Display” – 6×8 “widescreen” array of RGB LEDs with 262,000 colors each; LEDs can expand off-board onto external arrays via the edge connector Wireless Connectivity – 802.11b/g/n WiFi 4 (2.4GHz) and Bluetooth 4.2 LE via an ESP32 module (ESP-WROOM-32) USB – 1x Micro USB port for power and programming/debugging Expansion A/D Converters (four) accessed via on-board coprocessor […]

SiFive U8-Series Out-of-Order RISC-V Core IP Takes on Arm Cortex-A72 Core

Earlier this week, we wrote about SiFive Shield open security platform as the equivalent of Arm TrustZone security technology, but the company had had another important announcement this week with the introduction of SiFive U8-Series Out-of-Order (OoO) RISC-V Core IP with much higher performance than the company’s earlier U7-series core and competing with Arm Cortex A72 core. At first, the company will offer two standard cores with SiFive U84 RISC-V core optimized for power efficiency and area efficiency, and the SiFive U87 RISC-V core with vector processing. SiFive U84 Performance & Efficiency We do not have much information about U87, but SiFive already published some interesting details about U84 cores. SiFive U84 core offers about 3.1 times higher performance compared to their earlier U74 standard core thanks to a 2.3x increase in IPC combined with a 1.4x increase in maximum frequency. Compared to SiFive U54, U84 delivers 5.3x higher performance […]

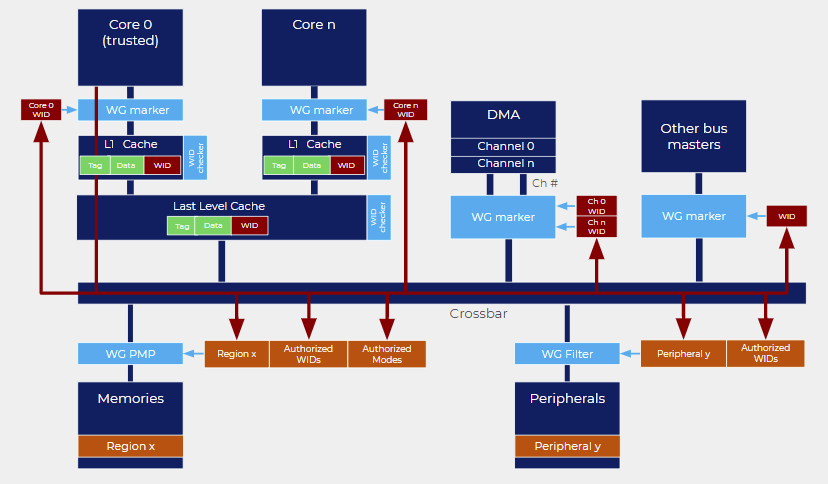

SiFive Shield is an Open Security Platform for RISC-V Processors

Most Arm processors and Armv8-M microcontrollers support Arm TrustZone security with hardware-enforced isolation built into the CPU. But so far, I had not read anything about equivalent solutions for RISC-V processors. It turns out Hex-Five’s MultiZone security is one of the RISC-V hardware-security providing an answer to Arm TrustZone, and besides checking out the presentation slides, you can also watch the video filmed at RISC-V Workshop Taiwan last March. But what brought me to write about RISC-V security is SiFive announcement for their Shield open security platform for RISC-V processors SiFive Shield Overview SiFive Shield is an open, scalable security platform designed for RISC-V processors. It supports root-of-trust, customizations, and offers per-memory protected memory regions and multi-core privilege modes. Combined with SiFive WorldGuard, SiFive Shield enables greater isolation. SiFive WorldGuard Isolation SiFive WorldGuard is a fine-grain security model for isolated code execution and data protection. It offers core-driven and process-id […]

SiFive RISC-V Processors to Support Imagination PowerVR GPU and NNA IP Cores

RISC-V is getting more popular and mature as development progress, but if you want a system with RISC-V and a GPU so far you had to use a PCIe graphics card which is not cost-effective nor practical for most applications based on RISC-V processor. What is needed is some GPU IP that will glue with RISC-V core. Developing a new GPU is not an easy task (understatement of the month) so it would make sense to go with solutions available on the market. However, Arm Mali is tied to Arm Cortex cores and Arm is unlikely to want to help RISC-V take away their market share, and Adreno and VideoCore are owned by respectively Qualcomm and Broadcom which are unwilling to provide their GPU IP to third parties. This basically leaves us with Vivante and Imagination. Vivante may have made the most sense since open-source graphics drivers do exist (Etnaviv), […]

SiFive S2 RISC-V Core may be the World’s Smallest 64-bit Embedded Core

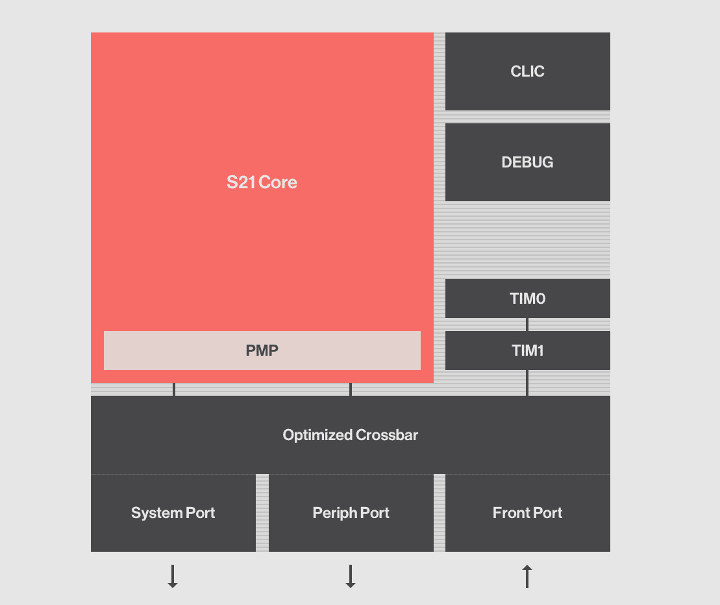

Last year, SiFive introduced their first RISC-V cores competing with Arm Cortex-R family of processors thanks to their S7 Series 64-bit RISC-V Core IP providing an answer to Arm Cortex-R7/R8 32-bit real-time processors. The company has now announced the SiFive S2 RISC-V core that it claims to be the world’s smallest 64-bit embedded core, and also the first SiFive IP core without any direct competitive equivalent in the market. For now, there’s only one core in the family with SiFive S21 offering the following key features: RISC-V ISA – RV64IMAC 64-bit AXI Ports Machine and User Mode with 4 Region Physical Memory Protection 3-stage pipeline with Simultaneous Instruction and Data Access 2 Banks of Tightly Integrated Memory (TIM) CLIC (Core Local Interrupt Controller) with 127 interrupts Advanced debug with 4 hardware breakpoints/watchpoints Performance – 1.6 DMIPS/MHz; 3.2 Coremarks/MHz The company compares its to the SiFive S5 cores, which I had […]

HiFive1 Rev B Board Gets FE310-G002 RISC-V Processor, WiFi & Bluetooth Module

SiFive launched what may have been the very first RISC-V development board in 2016 thanks to their HiFive1 Arduino compatible board powered by Freedom E310 (FE310) open source RISC-V processor. The company has now launched an upgrade version of the processor and board. Meet FE310-G002 processor and HiFive1 Rev B development board. HiFive1 Rev B development board specifications with new features highlighted in bold or stricken-through: MCU – SiFive Freedom E310-G0002 32-bit RV32IMAC processor @ up to 320+ MHz (1.61 DMIPS/MHz) Storage – 32 Mbit SPI flash (was 128 Mbit in the first version) Connectivity – ESP32-SOLO-1 WiFi & Bluetooth module I/Os 19x Digital I/O Pins 19x external interrupt pins 1x external wakeup pin 9x PWM pins 1/3 SPI Controllers/HW CS Pins I/O Voltages – 3.3V or 5V supported; note: bidirectional level shifters removed so FE310-G002 can drive the I/O pins directly at 3.3V only. USB – 1x micro USB […]

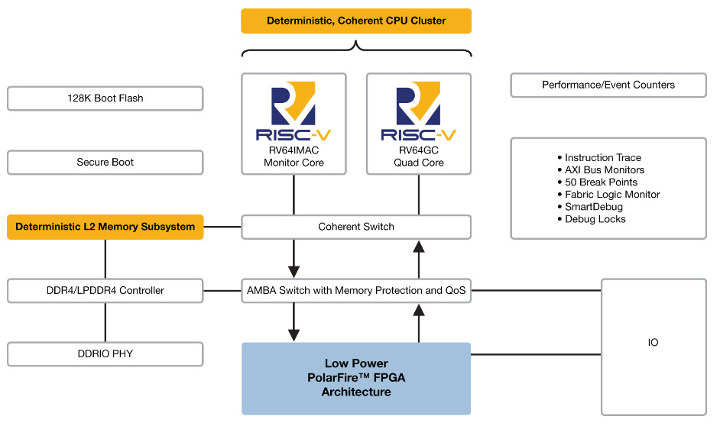

MicroSemi Introduces PolarFire FPGA & RISC-V SoC

In the past we’ve covered SoCs comprised of Arm cores and FPGA fabric via Xilinx Zynq-7000 series SoCs and Zynq UltraScale+ series MPSoCs, respectively featuring up to two Arm Cortex A9 cores, and up to four Cortex A53 cores. MicroSemi has now announced an alternative, not based on Arm cores, but instead based on SiFive U54-MC RISC-V cores combined with PolarFire FPGA fabric. PolarFire FPGA RISC-V SoC key features & specifications: FPGA – Microsemi PolarFire FPGA Processor Cores – Up to 4x SiFive U54-MC RISC-V cores clocked at up to 1.5GHz (performance similar to Cortex-A35 cores); 28nm process Deterministic Coherent Multi-core CPU Cluster Deterministic L2 Memory Subsystem System Memory I/F – Integrated DDR4/LPDDR4 Controller and PHY Storage – Secure Boot, 128K Boot Flash Debug capability Rich I/Os Low Power – Low static power; power optimized transceivers, up to 50% lower power compared to SRAM based FPGAs So we don’t have […]