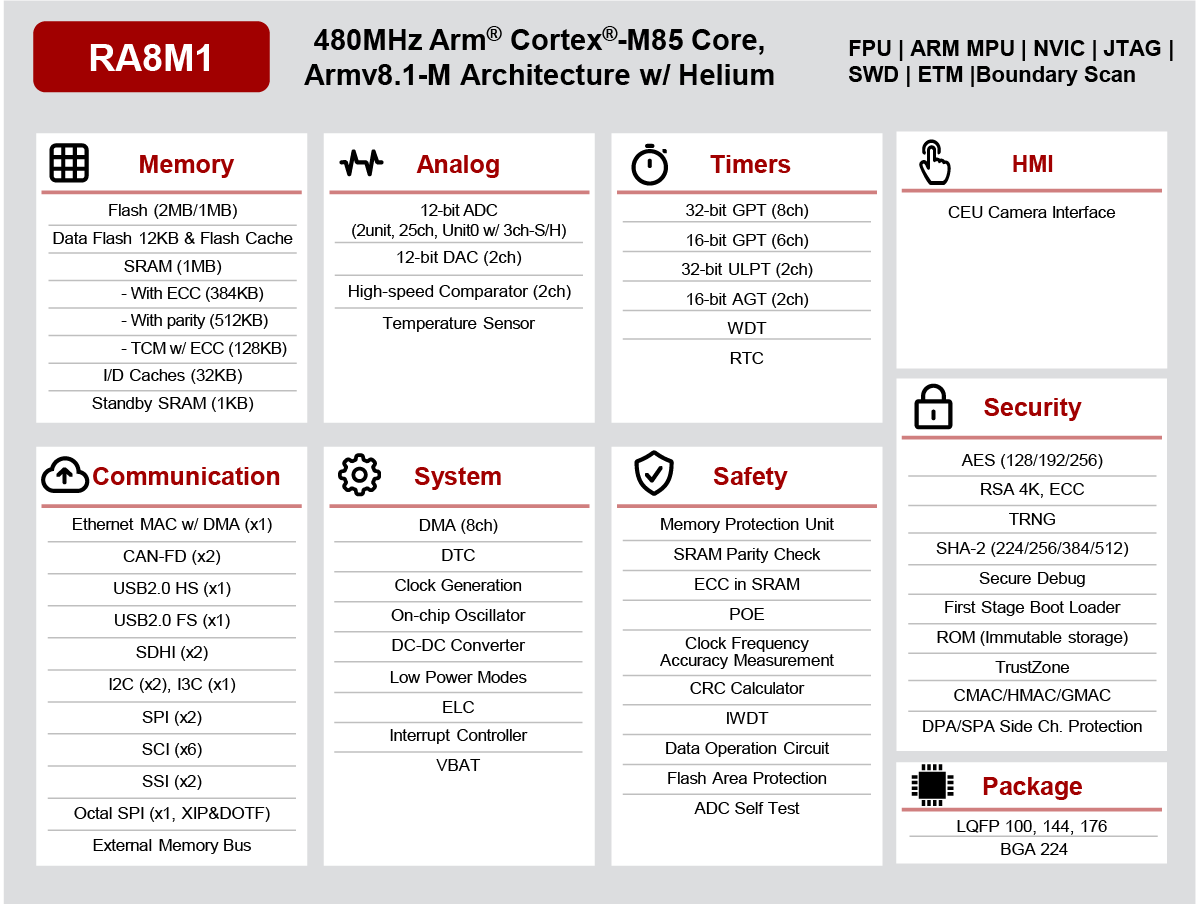

Renesas RA8M1 is an up to 480 MHz Arm Cortex-M85 microcontroller with Arm Helium technology to improve DSP and machine learning performance on Cortex-M microcontrollers, and delivering up to 6.39 CoreMark/MHz performance using EEMBC’s CoreMark, or over 3,000 CoreMark at 480 MHz. The Arm Cortex-M85 core was first unveiled in April 2022 as a faster Cortex-M7 alternative and new Arm Helium technology that delivers machine learning performance similar to Cortex-M55 application processor. We had some teases about the upcoming Renesas Cortex-M85 in the last year, but the world’s first Cortex-M85 microcontroller is finally here. Renesas RA8M1 key features and specifications: MCU core – Arm Cortex-M85 clocked at 240 to 480 MHz with Helium MVE (M-Profile Vector Extension) with 32KB I/D Caches and 12KB Data Flash Memory & Storage 1MB SRAM with TCM 1MB to 2MB Flash memory External memory interfaces (CS/SDRAM) Camera – 16-bit Capture Engine Unit (CEU) interface Communication […]

OpenWrt 23.05 released with MbedTLS by default, Rust packages, over 1,790 supported devices

OpenWrt 23.05 open-source Linux operating system for routers and resource-constrained headless embedded systems has just been released with over 4300 commits since the release of OpenWrt 22.03 a little over a year ago. The new release now supports over 1790 devices or about over 200 new devices compared to the OpenWrt 22.03 release with notable new targets including the ipq807x target for the Qualcomm IPQ807x WiFi 6 SoCs, the mediatek/filogic subtarget for the Mediatek Filogic 830 and 630 SoCs, and the sifiveu target for the HiFive Unleashed and Unmatched RISC-V development boards. OpenWrt 23.05 switches from wolfSSL to MbedTLS as default because the latter has a much smaller footprint and offers a more stable ABI (application binary interface) and LTS releases, but it does lack support for TLS 1.3, so users who need the latter may still switch to wolfSSL if needed. Another highlight of the new OpenWrt release is […]

Microchip PIC32CZ CA 300 MHz Arm Cortex-M7 MCU features a Hardware Security Module (HSM)

Microchip PIC32CZ CA is a new family of Arm Cortex-M7 microcontrollers with the PIC32CZ CA90 integrating a Hardware Security Module (HSM), and the PIC32CZ CA80 doing without one. The HSM in the PIC32CZ CA90 provides advanced security for industrial and consumer applications and operates as a secure subsystem with a separate MCU on board that runs the firmware and security features including hardware secure boot, key storage, cryptographic acceleration, true random number generator, and more. Microchip PIC32CZ CA key features and specifications: MCU core – Arm Cortex-M7 clocked at up to 300 MHz with 16KB ECC-protected instruction and data L1 cache, up to 256Kb of Tightly Coupled Memory (TCM): 128 KB each of ECC-protected Instruction and Data TCM Memory 512KB or 1MB SRAM with ECC, 8KB SRAM for backup mode 2MB, 4MB, or 8MB flash 2x 80KB boot flash memory 16-bit external bus interface (EBI) – Static memory controller for […]

Android 14 released, source code hits AOSP

Google has just released Android 14 for supported devices such as Google Pixel phones and pushed the source code to AOSP (the Android Open-Source Project). Most of the changes to the fourteenth version of the Android operating system were introduced with the first Android 14 developer preview – released in February 2023 – which included performance improvements, better privacy and security, and additional user-side customization options. Some of the new features unveiled since the first Android 14 developer preview include: AI-generated wallpapers using text-to-image diffusion models to help users easily create unique wallpapers HDR images with Ultra HDR (Android 13 already supported HDR videos) Built-in Health Connect support to let people track their fitness, health, and wellness levels across apps in a secure way respecting privacy. Android 14 encourages users to set a six-digit PIN (or longer) to improve security. Improved accessibility with vision-and hearing-inclusive features such as an enhanced […]

$999 Librem 11 Linux tablet features Celeron N5100 processor, 1TB NVMe SSD, 2.5K AMOLED display

Purism Librem 11 is an 11.5-inch Linux tablet running the secure PureBoot bootloader and PureOS Linux distribution with a focus on privacy and respect for personal freedom. The tablet comes with what looks to be a decent 11.5-inch AMOLED touchscreen display with a 2560×1600 resolution, 8GB RAM, and a 1TB NVMe SSD, but the Intel Celeron N5100 quad-core Jasper Lake processor would be considered entry-level in 2023. The tablet also comes with a keyboard and stylus making a 2-in1 hybrid device. Purism Librem 11 specifications: SoC – Intel Celeron N5100 quad-core Jasper Lake processor @ 1.1GHz/2.89GHz (Turbo) with Intel UHD Graphics System Memory – 8 GB LPDDR4 (soldered) Storage 1 TB NVMe SSD (Kingston KC3000) microSD card reader implemented with Genesys Logic GL823K Display – 11.5-inch AMOLED display with 2560×1600 resolution, 60Hz refresh rate, Goodix GXTP7380 multitouch digitizer, stylus support Stylus – 2x buttons, 4096 pressure levels, tilt support (XY), […]

Intel Downfall (Gather Data Sampling) vulnerability impacts AVX2/AVX-512 workloads

After vulnerabilities like Spectre and Meltdown were discovered in 2018, Intel processors have more vulnerabilities with the Downfall attacks that target the Gather instruction part of AVX2/AVX-512 and impact 6th generation Skylake up to 11th generation Tiger Lake processors introduced as far back as 2014. It does not affect more recent processors, and as somebody who has just purchased a laptop based on a 13th Raptor Lake processor, I guess I can breathe a sigh of relief until the next vulnerability is discovered, but people using hardware with older Intel processors will have to update the OS and suffer from a performance impact, at least for tasks leveraging AVX2 or AVX-512. The website about the Downfall vulnerability explains: Downfall attacks targets a critical weakness found in billions of modern processors used in personal and cloud computers. This vulnerability, identified as CVE-2022-40982, enables a user to access and steal data from […]

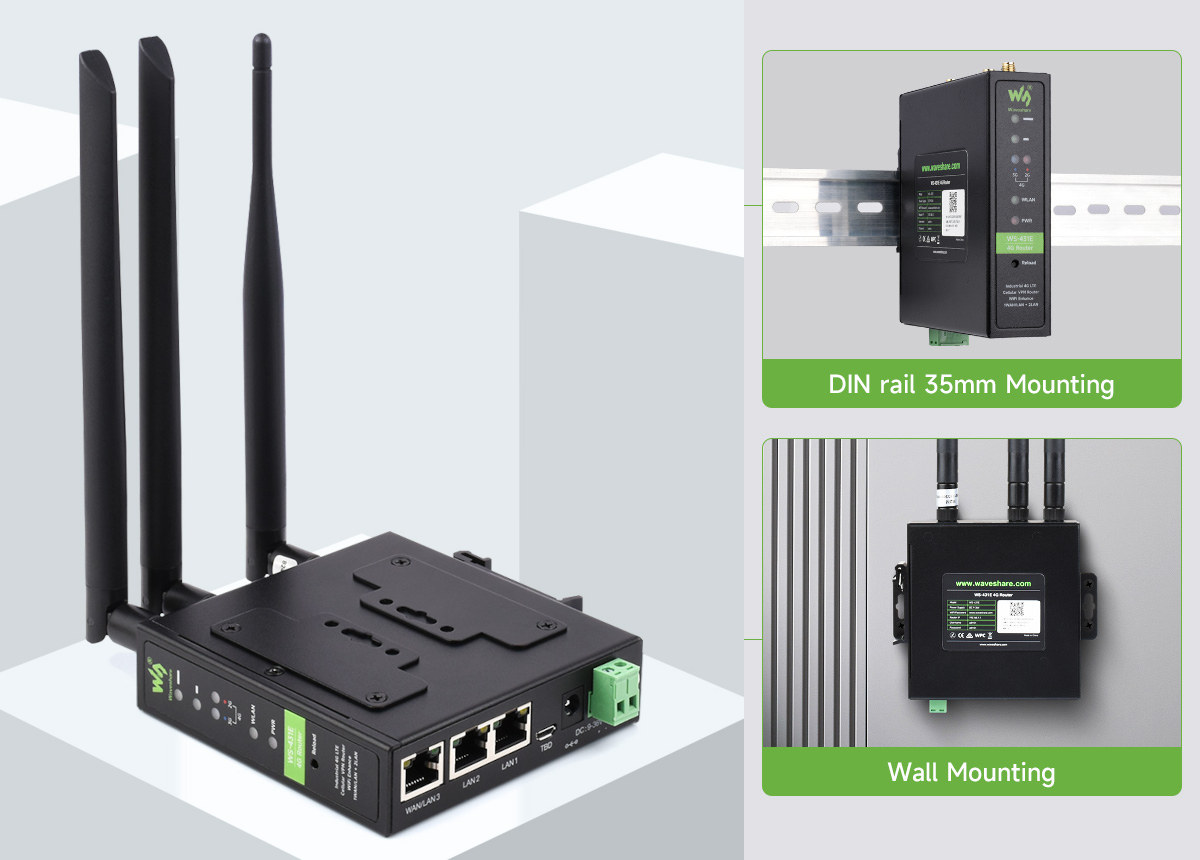

DIN-Rail mountable industrial 4G LTE router takes 9V to 36V DC power input

Waveshare WS-431E is an industrial-grade 4G LTE router with three Ethernet ports, WiFi 4, wall and DIN-Rail mounting options, and support for a wide power input range between 9V and 36V DC. The router is said to be based on two Qualcomm chips without further details provided, support various VPN protocols, and be suitable for networked medical equipment, Smart Agriculture, Smart Cities, robots, and security monitoring applications. Waveshare WS-431E specifications: SoC – “Dual Qualcomm chips” for WiFi and 4G LTE Networking Ethernet 1x 10/100Mbps Ethernet RJ45 WAN port (can be configured as LAN) with auto MDI/MDIX, 1.5KV electromagnetic isolation protection 2x 10/100Mbps Ethernet RJ45 LAN ports with auto MDI/MDIX, 1.5KV electromagnetic isolation protection 2.4 GHz 802.11b/g/n WiFi 4 2×2 MIMO up to 300 Mbps, and 500-meter LoS range 4G LTE cellular 4G TDD-LTE – B38/40/41 4G FDD-LTE – B1/3/7/8/20/28A 3G WCDMA – B1/8 2G GSM/EDGE – B3/8 Nano SIM card […]

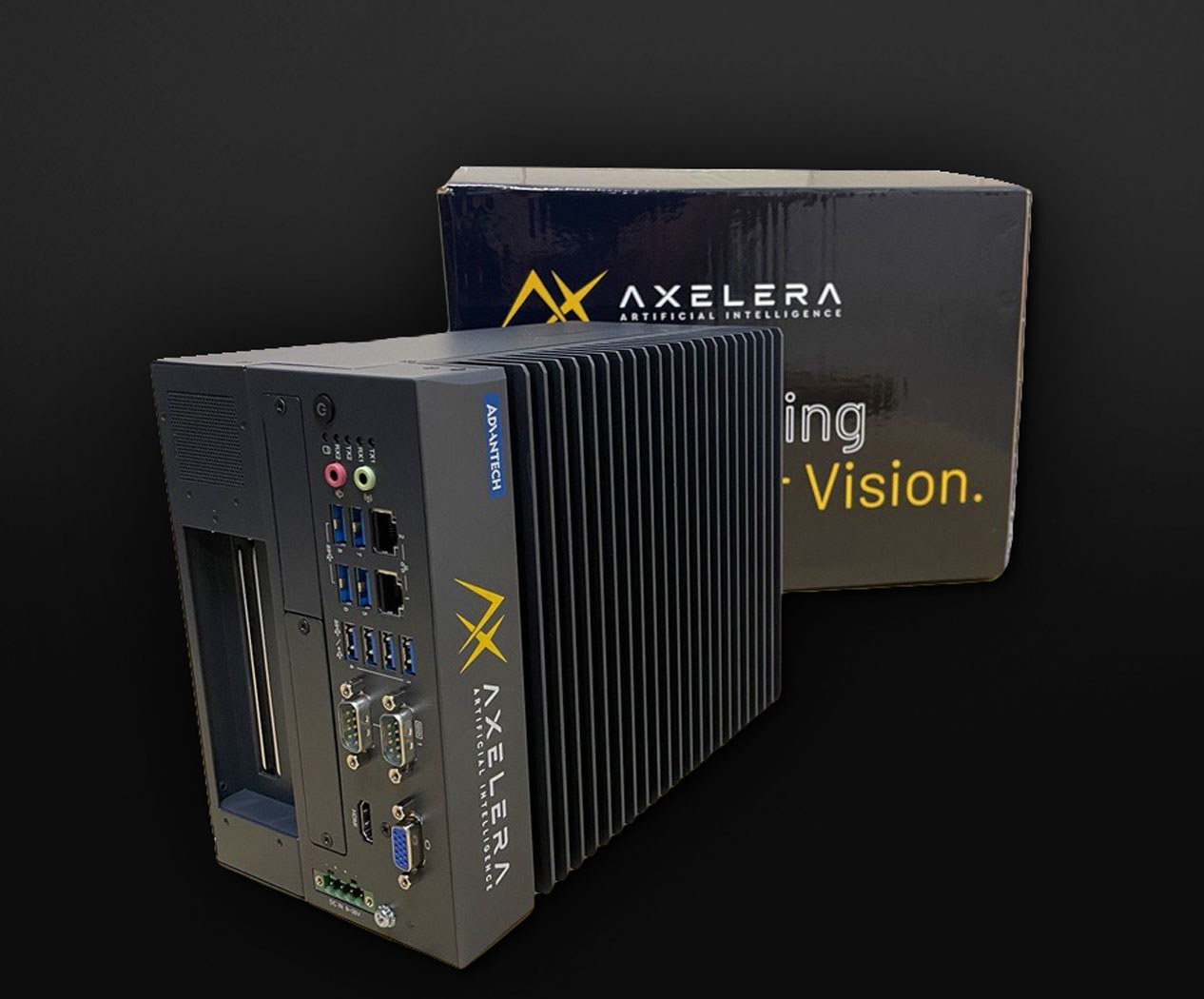

Get Early Access to the World’s Most Powerful Edge AI Accelerator! (Sponsored)

Final Call for Axelera AI’s Early Access Program A few months ago Axelera AI launched their Metis AI hardware and software platform, available as M.2 cards, PCIe boards, and vision-ready systems, combined with the Voyager SDK. Now, Axelera AI’s Early Access Program (EAP) is entering its final phase – the first evaluation kits are almost ready to be shipped. This program offers a unique opportunity for customers who have signed up to experience firsthand the accuracy, performance, and usability of the Metis AI Platform. Axelera AI delivers the most powerful AI Accelerator in the world. With a PCIe AI Edge accelerator card delivering a peak performance of 214 TOPS. Using a smaller form factor, the M.2 AI Edge accelerator module delivers up to 106 TOPS peaks. This handles the most demanding vision applications. In this article, we will delve into the advantages of the EAP by sharing three customer stories […]