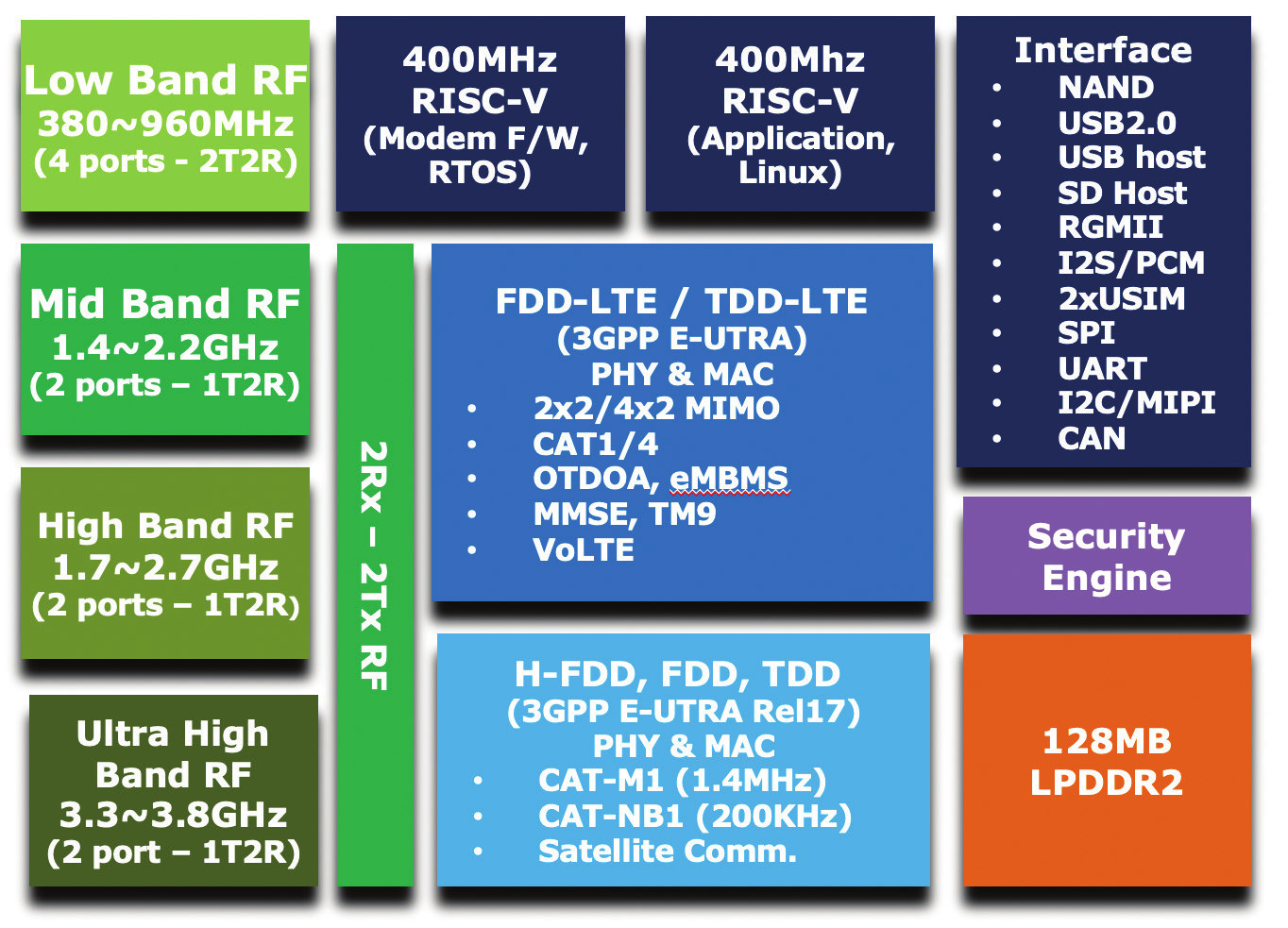

CT Semiconductor Holding GDM7243SL is a multi-mode 5G/4G LTE IoT modem with two 400 MHz RISC-V cores capable of operating in Cat 4, Cat 1bis, Cat M1, Cat NB1/NB2 (NB-IoT) and non-terrestrial networks (NTN) in order to work anywhere on earth. If I remember correctly, one of the first commercial RISC-V SoCs I saw was a storage controller from Western Digital introduced in 2019. But since then, we’ve seen more and more RISC-V chips come to market from entry-level microcontrollers up to Linux-capable application processors, and even chips for datacenters that are out of the scope of topics covered on CNX Software. But with GDM7243SL, I think it’s the first time I’ve encountered a RISC-V modem, so let’s have a closer look. There are two models, the GDM7243SL1 and GDM7243SL2, with different memory and storage options, and the L1 lacks support for LTE Cat 4. GDM7243SL key features: CPU 400 […]

WCH CH32V002 32-bit RISC-V MCU comes with 4KB SRAM, supports 2V to 5V DC supply voltage

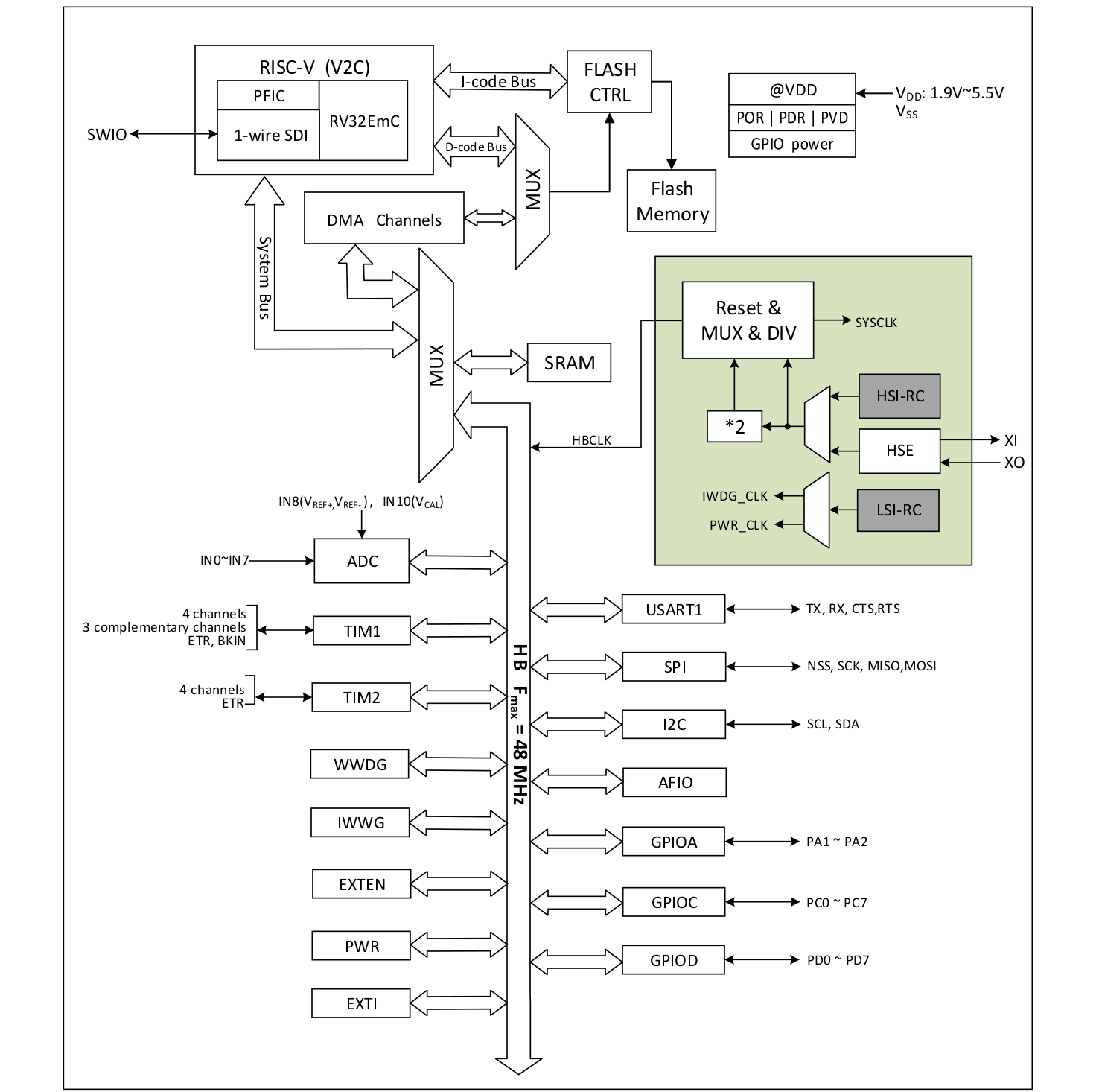

WCH CH32V002 is an industrial-grade general-purpose 32-bit RISC-V microcontroller that is pin-to-pin compatible with the popular CH32V003 MCU with 4KB SRAM instead of 2KB, a wider input voltage range from 2V to 5V, and other improvements. Earlier this month we wrote about the WCH CH32V006 RISC-V microcontroller that offers an upgrade to the CH32V003 with more I/Os, memory, and storage, requiring a new PCB layout. But now, the Chinese company has unveiled a pin-compatible alternative with the CH32V002 that adds more SRAM, uses the new V2C core with RV32EmC instruction set (also used in the CH32V006), offers a larger bootloader and configuration memories, upgrades the ADC to 12-bit, and adds support for 8-channel touch-key channel detection. WCH CH32V002 specifications (highlights in bold show differences against the CH32V003): CPU – 32-bit “RISC-V2C” core up to 48 MHz using RV32EmC instruction set Memory – 4KB SRAM Storage – 16KB flash, 3328 Bytes […]

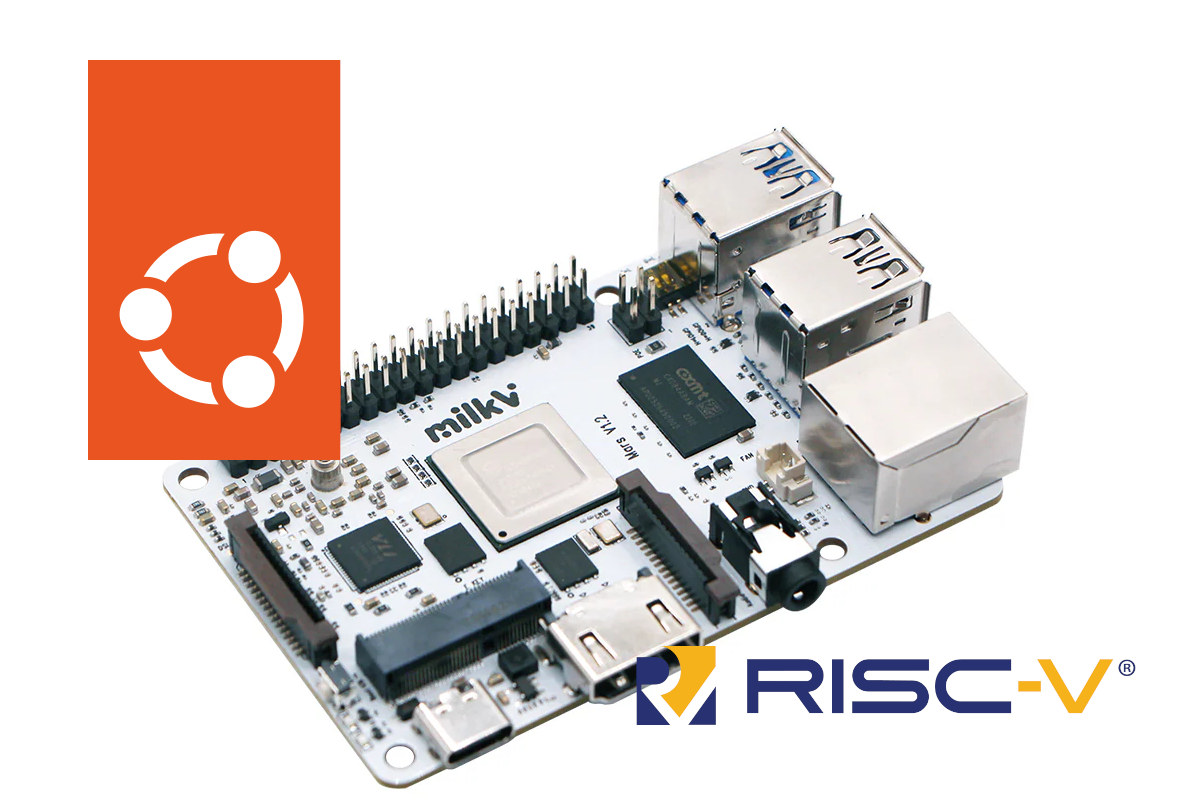

Canonical releases Ubuntu 24.04 Server image for Milk-V Mars RISC-V SBC

Canonical has been releasing Ubuntu RISC-V images for SBCs and QEMU at least since 2021. The latest addition is an Ubuntu 24.04 Server image for the Mars credit-card-size SBC powered by StarFive JH7110 quad-core RISC-V SoC and designed by Shenzhen Milk-V Technology. That means we now have Ubuntu Server images for the QEMU emulator, AllWinner Nezha SBC, Microchip Polarfire SoC FPGA Icicle Kit, SiFive Unmatched mini-ITX motherboard, Sipeed LicheeRV Dock, StarFive VisionFive 2 SBC, and the Mars SBC. You’ll note there aren’t any Ubuntu Desktop images for now, because the GPU (if any) in RISC-V SoCs is not yet fully supported. Mars SBC specifications: SoC – StarFive JH7110 CPU – Quad-core RISC-V processor (RV64GC) at up to 1.5GHz GPU – Imagination BXE-4-32 GPU with support for OpenCL 1.2, OpenGL ES 3.2, Vulkan 1.2 VPU H.264 & H.265 4Kp60 decoding H.265 1080p30 encoding JPEG encoder / decoder System Memory – 1GB, […]

Linux 6.9 release – Main changes, Arm, RISC-V, and MIPS architectures

Linus Torvalds has just announced the release of Linux 6.9 on LKML: So Thorsten is still reporting a few regression fixes that haven’t made it to me yet, but none of them look big or worrisome enough to delay the release for another week. We’ll have to backport them when they get resolved and hit upstream. So 6.9 is now out, and last week has looked quite stable (and the whole release has felt pretty normal). Below is the shortlog for the last week, with the changes mostly being dominated by some driver updates (gpu and networking being the big ones, but “big” is still pretty small, and there’s various other driver noise in there too). Outside of drivers, it’s some filesystem fixes (bcachefs still stands out, but ksmbd shows up too), some late selftest fixes, and some core networking fixes. And I now have a more powerful arm64 machine […]

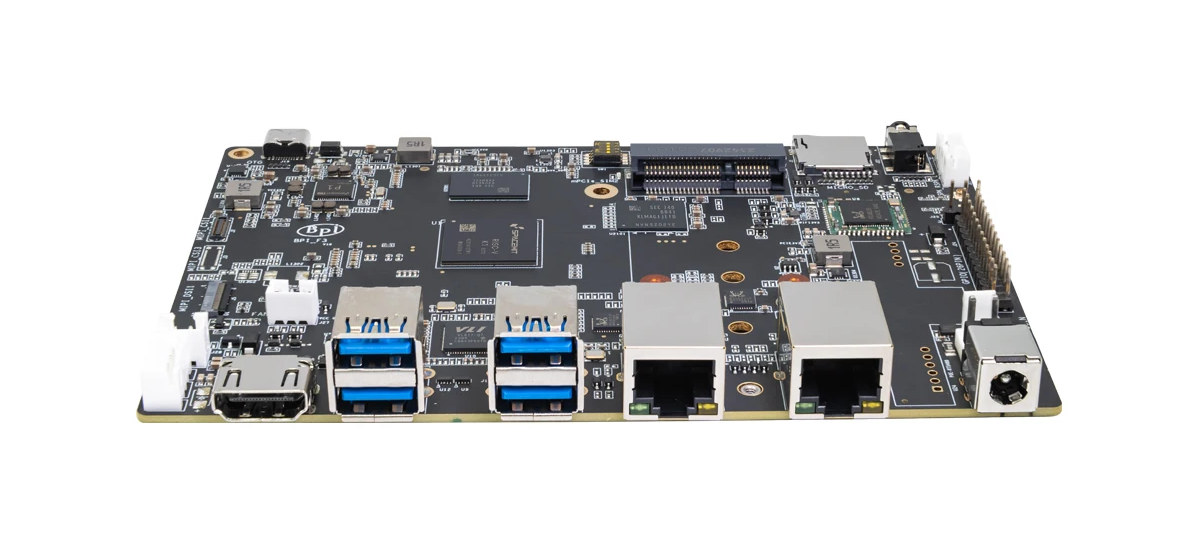

Banana Pi BPI-F3 SBC features SpacemIT K1 octa-core RISC-V AI SoC

Banana Pi BPI-F3 single board computer (SBC) is powered by the same SpacemiIT K1 octa-core 64-bit RISC-V SoC with 2TOP AI accelerator found in the upcoming Muse Book RISC-V laptop. The board comes with up to 4GB RAM and 16GB eMMC flash, supports NVMe or SATA storage via its M.2 socket, is equipped with HDMI and MIPI DSI display interfaces, two MPI CSI camera interfaces, two gigabit Ethernet ports, a WiFi 5 and Bluetooth 4.2 module, and can also take a PCIe module for 4G LTE cellular connectivity. Other features include four USB 3.0 Type-C ports, a microSD card slot, a 26-pin GPIO header, and optional support for PoE. Banana Pi BPI-F3 specifications: SoC – SpacemiT K1 CPU – 8-core X60 RISC-V processor with single-core performance equivalent to about 1.3x the performance of an Arm Cortex-A55 GPU – Imagination IMG BXE-2-32 with support for OpenCL 3.0, OpenGL ES3.2, Vulkan 1.2 […]

Sipeed MaixCAM is a RISC-V AI camera devkit with up to 5MP camera, 2.3-inch color touchscreen display, GPIOs

Sipeed MaixCAM is an AI camera based on SOPHGO SG2002 RISC-V (and Arm, and 8051) SoC with a 1 TOPS NPU that takes up to 5MP camera modules and comes with a 2.3-inch color touchscreen display. The development kit also comes with WiFi 6 and BLE 5.4 connectivity, optional Ethernet, audio input and output ports, a USB Type-C port, and two 14-pin GPIO headers for expansion that makes it suitable for a range of computer vision, Smart audio, and AIoT applications. Sipeed MaixCAM specifications: SoC – SOPHGO SG2002 CPU 1 GHz RISC-V C906 processor or Arm Cortex-A53 core (selectable at boot) running Linux 700 MHz RISC-V C906 core running an RTOS 25 to 300 MHz low-power 8051 processor NPU – 1 TOPS @ INT8 with support for models such as Mobilenetv2, YOLOv5, YOLOv8, etc… Video Codec – H.264, H.265, MJPEG hardware encoding and decoding up to 2K @ 30fps Memory […]

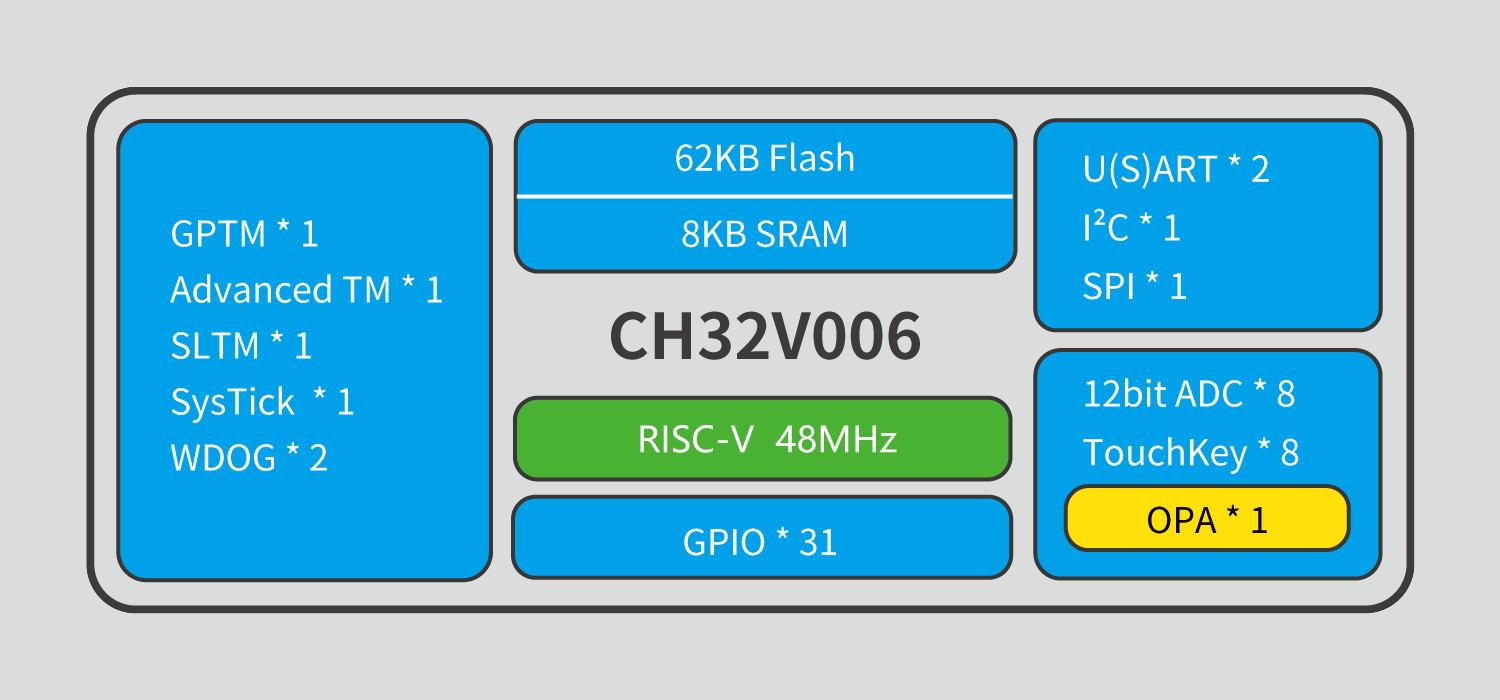

WCH CH32V006 RISC-V microcontroller adds more I/Os, memory, and storage compared to CH32V003

WCH CH32V006 RISC-V microcontroller is an upgrade to the 10-cent CH32V003 microcontroller with more I/Os, up to four times the memory, storage, a wider supply voltage range, the addition of a TouchKey interface, as well as a new 32-bit V2C RISC-V core instead of the V2A core found in the CH32V003. More specifically that means we went from the CH32V003 with 2KB SRAM and 8KB flash, up to 8KB SRAM and 62KB for the CH32V006, and 6KB SRAM and 32KB flash for the CH32V005, a smaller sibling of the new RISC-V microcontroller. WCH CH32V005 & CH32V006 specifications (with highlights in bold to show differences against CH32V003): CPU – 32-bit “RISC-V2C” core up to 48 MHz Memory – 6KB SRAM (CH32V005) or 8KB SRAM (CH32V006) Storage – 32KB flash (CH32V005) or 62KB flash (CH32V006) Peripherals Up to 31x GPIO with interrupt support (CH32V003 had up to 18x GPIO) 2x USART interfaces […]

QEMU 9.0 released with Raspberry Pi 4 support and LoongArch KVM acceleration

QEMU 9.0 open-source emulator just came out the other day, and it brings on board major updates and improvements to Arm, RISC-V, HPPA, LoongArch, and s390x emulation. But the most notable updates are in Arm and LoongArch emulation. The QEMU 9.0 emulator now supports the Raspberry Pi 4 Model B, meaning you can run the 64-bit Raspberry Pi OS for testing applications without owning the hardware. However, QEMU 9.0 has some limitations since Ethernet and PCIe are not supported for the Raspberry Pi board. According to the developers, these features will come on board in a future release. For now, the emulator supports SPI and I2C (BSC) controllers. Still on ARM, QEMU 9.0 provides board support for the mp3-an536 (MPS3 dev board + AN536 firmware) and B-L475E-IOT01A IoT node, plus architectural feature support for Nested Virtualization, Enhanced Counter Virtualization, and Enhanced Nested Virtualization. If you develop applications for the LoongArch […]