Espressif Systems “ESP32-P4-Function-EV-Board” – the official ESP32-P4 development board – is now available in limited quantities on Espressif’s AliExpress store for $55.44, and some other AliExpress stores at a premium as part of a kit with a 7-inch touchscreen display and a 2MP camera module. First unveiled in January 2023, the ESP32-P4 is the first general-purpose RISC-V microcontroller from Espressif Systems without any wireless connectivity. It’s a high-end microcontroller with two RISC-V cores clocked at 400 MHz, vector instructions for AI acceleration, a 2D graphics accelerator for smooth graphical user interfaces, and H.264 video encoding support. There’s been some buzz about it in recent months, and finally, it’s now possible to purchase an ESP32-P4 board for evaluation and software development. ESP32-P4-Function-EV-Board development board specifications: Microcontroller – Espressif Systems ESP32-P4 CPU Dual-core RISC-V HP (High-performance) CPU @ up to 400 MHz with AI instructions extension and single-precision FPU, 768KB of on-chip […]

Building a workstation with Radxa ROCK 5 ITX (Arm) or Milk-V Jupiter (RISC-V) mini-ITX motherboard – Part 1: The hardware

Radxa ROCK 5 ITX is a mini-ITX motherboard powered by a Rockchip RK3588 octa-core Cortex-A76/A55 processor, and the Shenzhen Milk-V Jupiter is another mini-ITX motherboard, but based on SpacemIT K1 octa-core 64-bit RISC-V processor instead. When Radxa contacted me about reviewing those, I thought it would be interesting to review a complete kit with a mini-ITX case since I had never built this type of system myself. Yesterday, I was surprised to receive two large packages and thought maybe a company sent me a 3D printer or laser engraver kit, but instead, I got one package with the two Arm and RISC-V mini-ITX motherboards and another with a mini-ITX NAS enclosure with 6x SATA bays. Radxa ROCK 5 ITX unboxing Let’s look at the ROCK 5 ITX motherboard and accessories first. The motherboard ships with a rear panel and two screws for the M.2 module. The motherboard features the Rorkchip […]

Linux 6.10 Release – Notable changes, Arm, RISC-V, and MIPS architectures

Linux Torvalds has announced the release of Linux 6.10 on LKML: So the final week was perhaps not quote as quiet as the preceding ones, which I don’t love – but it also wasn’t noisy enough to warrant an extra rc. And much of the noise this last week was bcachefs again (with netfs a close second), so it was all pretty compartmentalized. In fact, about a third of the patch for the last week was filesystem-related (there were also some btrfs latency fixes and other noise), which is unusual, but none of it looks particularly scary. Another third was drivers, and the rest is “random”. Anyway, this obviously means that the merge window for 6.11 opens up tomorrow. Let’s see how that goes, with much of Europe probably making ready for summer vacation. And the shortlog below is – as always – just the last week, not some kind […]

Microchip PIC64GX is a quad-core 64-bit RISC-V microprocessor for real-time processing

Microchip has introduced its first 64-bit RISC-V microprocessor family with the PIC64GX pin-to-pin compatible with the company’s PolarFire SoC FPGA devices and designed for edge designs for the industrial, automotive, communications, IoT, aerospace, and defense segments. The PIC6GX MPU supports asymmetric multiprocessing (AMP) to run Linux, real-time operating systems, and bare metal in a single processor cluster with secure boot capabilities. The company further claims the PIC64GX MPU is “the first RISC-V multi-core solution that is AMP capable for mixed-criticality systems”. The first member of the PIC64GX RISC-V family is the PIC64GX1000 microprocessor. Microchip PIC64GX1000 specifications: CPU Quad-core SiFive U54 64-bit five-stage, single-issue, in-order pipeline RISC-V (RV64GC) processor at up to 625 MHz with AMP and deterministic latencies, PMP and MMU units Single-core SiFive E51 64-bit RISC-V (RV64IMAC) monitor processor core at up to 625 MHZ with PMP unit Cache L1 memory subsystem with Single-Error Correct, Double-Error Detect (SECDED) Flexible […]

$20+ NanoKVM is a tiny low-power RISC-V KVM over IP solution

Sipeed NanoKVM is a tiny KVM over IP solution based on the Lichee RVNano RISC-V microcontroller board that offers most of the features provided by the popular Raspberry Pi 4-based PiKVM solution allowing users to fully remote control a host such as a computer, server, or SBC down to the BIOS level and power on/off. Two variants are available, namely the NanoKVM Lite and NanoKVM Full. Both support up to 1080p60 displays, virtual USB keyboard and mouse, USB storage emulation, Ethernet with Wake-on-LAN, and IPMI (Intelligent Platform Management Interface) through serial interfaces, but the Full version also adds a resin enclosure, 0.96-inch information display, ATX power control through USB-C port, a microSD card with the firmware, and optional WiFi or PoE support Sipeed NanoKVM specifications: SBC – Sipeed RVNano SoC – SOPHGO SG2002 Main core – 1GHz 64-bit RISC-V C906 or Arm Cortex-A53 core (the latter is likely not used […]

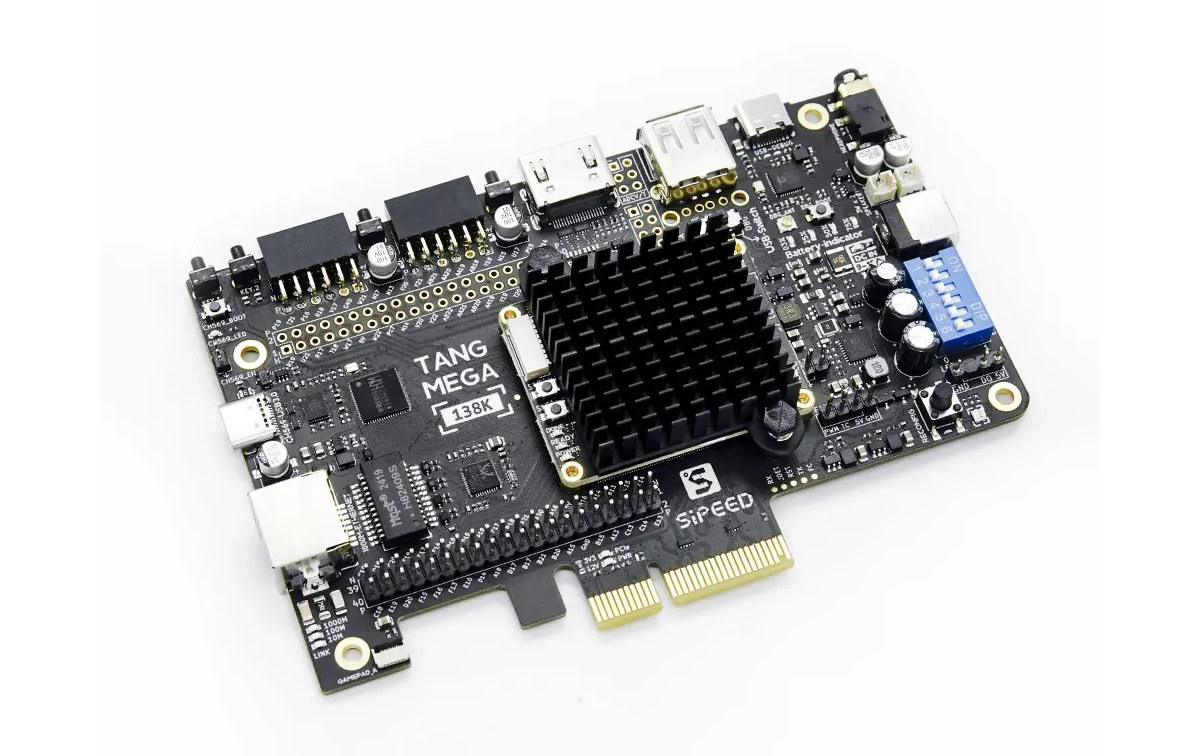

Sipeed Tang Mega 138K Dock is a lower-cost GOWIN GW5AST FPGA + RISC-V development board

The Sipeed Tang Mega 138K Dock is a low-cost version of the Tang Mega 138K Pro development board launched last year with the GOWIN GW5AST FPGA + RISC-V SoC, two SPF+ cages, a PCIe 3.0 x4 interface, and DVI Rx and Tx ports. The new Tang Mega 138K Dock keeps a GW5AST FPGA SoC but with a 484-ball package that fits on a smaller system-on-module, and does without the SPF+ cages, replaces the PCIe 3.0 x4 interface with a PCIe 2.0 x4 interface, and only uses a single HDMI port for DVI Rx or Tx. Sipeed Tang Mega 138K system-on-module Let’s first have a look at the specifications of the SoM itself: SoC FPGA – GOWIN GW5AST-LV138FPG484A with 138,240 LUT4 1,080 Kb Shadow SRAM (SSRAM) 6,120 Kb Block SRAM (BSRAM) Number of BSRAM – 340 298x DSP slices 12x PLLs 16x global clocks 24x HCLK 8x transceivers at 270Mbps to […]

Quectel FLM263D 2.4 GHz WiFi 6 and BLE 5.2 RISC-V module supports Amazon Alexa Connect Kit (ACK) SDK for Matter

Quectel Wireless FLM263D is a standalone WiFi 6 and Bluetooth 5.2 LE module with a 320 MHz RISC-V microcontroller that supports Alexa Connect Kit (ACK) SDK for Matter for connectivity with Amazon Alexa, Google Home, Samsung SmartThings, Apple HomeKit, and other Matter-compliant Smart Home devices. The module also implements security standards such as secure boot and Mbed TLS encryption. The FLM263D offers certifications such as Works with Alexa (WWA) and supports features such as Matter Simple Setup (MSS) that allows zero-touch setup of Matter-compliant smart home devices through Alexa. Quectel FLM263D specifications: MCU – RISC-V wireless microcontroller up to 320 MHz, with 512KB SRAM and 4MB flash (likely Beken BK7235) Wi-Fi 6 & BLE 5.2 WLAN Protocol – IEEE 802.11b/g/n/ax Wi-Fi Frequency Band – 2.4 GHz Wi-Fi Modulation Mode – CCK, BPSK, QPSK, 16QAM, 64QAM Wi-Fi Operating Mode – AP, STA, STA + AP WiFi Rx sensitivity – Up to […]

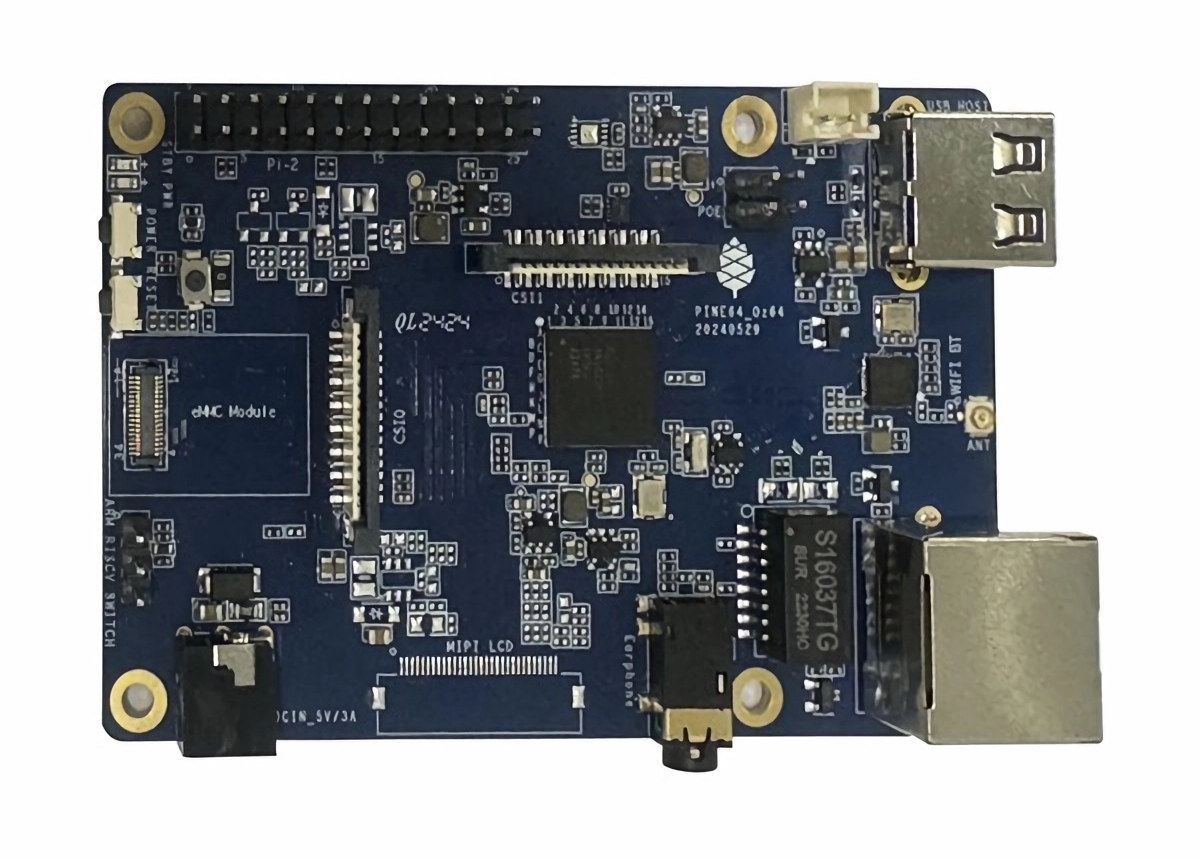

Pine64 Oz64 RISC-V+Arm SBC to support NuttX RTOS and Debian Linux

Pine64 Oz64 is an upcoming credit card-sized SBC based on the SOPHGO SG2000 RISC-V+Arm(+8051) processor that currently runs NuTTX RTOS, and a Debian Linux image is also in the works. With a name likely inspired by the earlier Pine64 Ox RISC-V SBC, the Oz64 is a more powerful embedded board with 512 MB of DRAM integrated into the SG2000, a microSD card, an eMMC flash module connector, Ethernet port, WiFi 6 and Bluetooth 5.2, a USB 2.0 Type-A host port, and a 26-pin GPIO header. Pine64 Oz64 specifications: SoC – SOPHGO SG2000 Main core – 1 GHz 64-bit RISC-V C906 or Arm Cortex-A53 core (selectable) Minor core – 700 MHz 64-bit RISC-V C906 core Low-power core – 25 to 300 MHz 8051 MCU core with 8KB SRAM NPU – 0.5 TOPS INT8, supports BF16 Integrated 512MB DDR3 (SiP) Storage MicroSD card slot eMMC flash module connector Display – Optional 2-lane […]