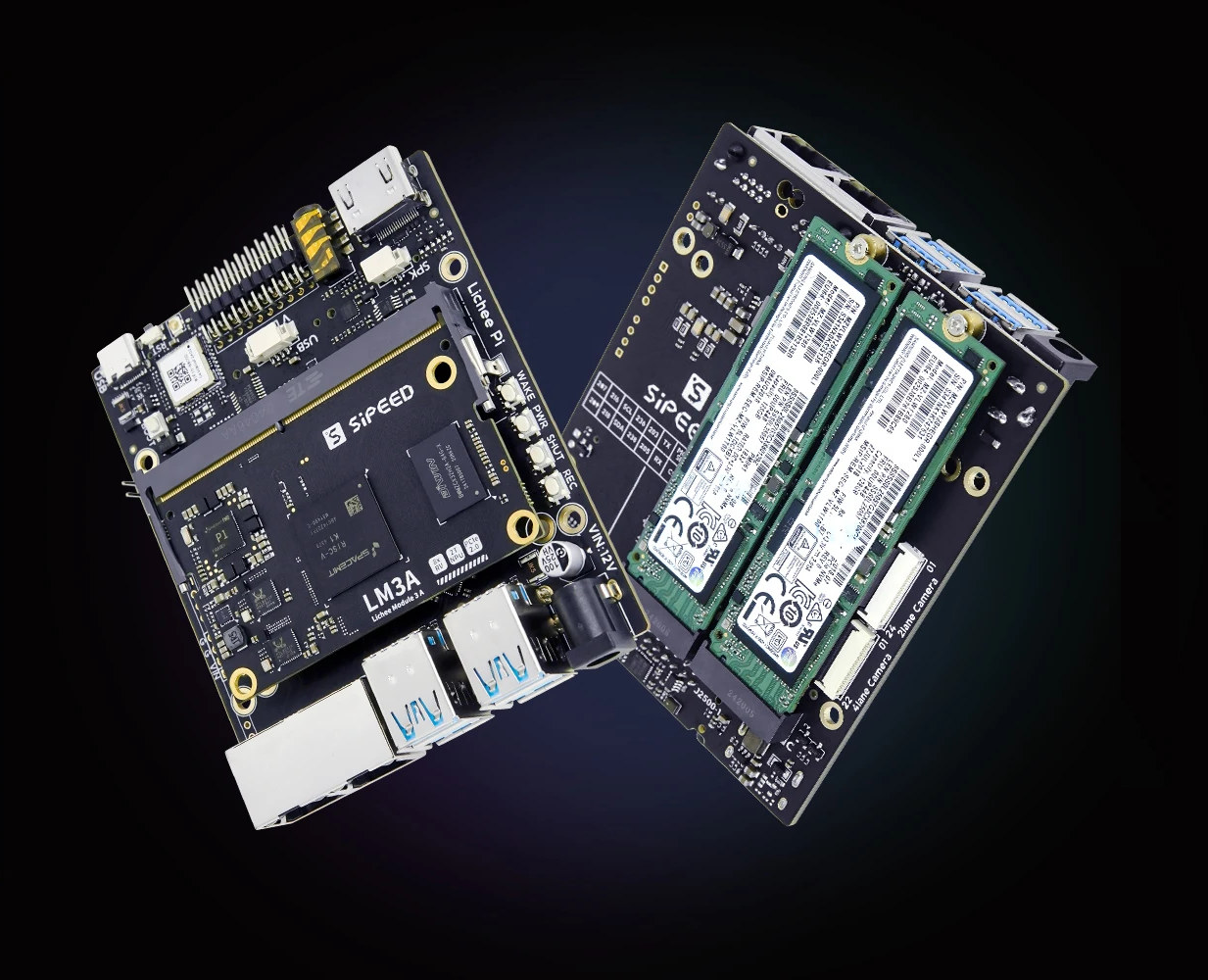

Sipeed LicheePi 3A is a development board comprised of the LM3A system-on-module based on SpacemIT K1 octa-core RISC-V SoC and the same baseboard as found in the earlier LicheePi 4A equipped with a T-Head TH1520 quad-core RISC-V “LM4A” system-on-module instead. The LicheePi 3A is currently offered with a 32GB eMMC flash and 8GB or 16GB LPDDR4x memory. The carrier board provides a microSD card, two M.2 PCIe sockets for storage or other expansion, two gigabit Ethernet ports, a WiFi 6 and Bluetooth 5.2 module, HDMI and MIPI DSI display interfaces, two MIPI CSI camera interfaces, four USB 3.0 ports, and a 20-pin GPIO header for expansion. Sipeed LicheePi 3A specifications: Sipeed LM3A SoM SoC – SpacemiT K1 CPU – 8-core X60 RISC-V processor @ 1.6 GHz GPU – Imagination IMG BXE-2-32 with support for OpenGL ES3.2, Vulkan 1.2, OpenCL 3.0; 20 GFLOPS VPU – H.265 and H.264 1080p60 decoding/encoding NPU […]

DietPi 9.7 and Armbian 24.8 released with improved support for Rockchip, Amlogic, and Allwinner SBCs

Armbian and DietPi are two separate projects that provide Linux-based OS images optimized for Arm-based single board computers. The last time we had a look at both projects was in June with the release of Armbian 24.5.1 and DietPi 9.4, but there have been several updates since then including the releases of the latest DietPi 9.7 and Armbian 24.8 Yelt just a few days ago. So let’s check out the latest changes. DietPi 9.7 DietPi is a lightweight Debian-based Linux distribution for SBCs and server systems that ships as a minimal image but users can install any packages they want, including the ones required for desktop environment, to match the requirements of the applications. It’s notably used by the Linamp project – a Raspberry Pi 4-based project that brings WinAMP to real life – that we covered a few weeks ago. DietPi 9.7 was released on August 25, 2024 with […]

Using RISC-V cores on the Raspberry Pi Pico 2 board and RP2350 MCU – From blinking an LED to building Linux

Raspberry Pi Pico 2 was released last month with a Raspberry Pi RP2350 microcontroller equipped with two Arm Cortex-M33 cores and two 32-bit RISC-V “Hazard3” cores with up to two cores usable at any time. So in this guide, we’ll show how to use the RISC-V cores on the RP2350 MCU, compare their performance against the Arm Cortex-M33 cores, and even build Linux for RISC-V for RP2350 boards that have PSRAM. Apart from the extra memory and more powerful cores, plus new features related to security and the HSTX interface, the Raspberry Pi Pico 2 and Pico will be very similar to the end user and the instructions in our article “Getting Started with Raspberry Pi Pico using MicroPython and C” remain valid. I don’t think there’s a MicroPython RISC-V image yet, so we’ll focus on running C programs on the RISC-V cores. A quick check with the Arm cores […]

DC-ROMA RISC-V Pad II octa-core RISC-V tablet can be pre-ordered for $149 and up

DeepComputing DC-ROMA RISC-V Pad II is a 10.1-inch tablet based on the same SpacemIT K1 octa-core 64-bit RISC-V processor found in the DC-ROMA RISC-V Laptop II introduced a few months ago, as well as in the MILK-V Jupiter mini-ITX motherboard. The RISC-V tablet features up to 16GB LPDDR4, 128GB eMMC flash, a 10.1-inch capacitive touchscreen display with 1920×1200 resolution, a 5MP rear camera, a 2MP webcam, a USB-C port for peripherals and/or an external display, and a 6,000 mAh battery. DC-ROMA RISC-V Pad II specifications: SoC – SpacemiT K1 CPU – 8-core X60 RISC-V processor @ up to 2.0 GHz GPU – Imagination IMG BXE-2-32 with support for OpenCL 3.0, OpenGL ES3.2, Vulkan 1.2 VPU – H.265, H.264, VP9, VP8 4K encoding/encoding NPU – 2.0 TOPS AI accelerator RVA 22 Profile RVV 1.0 compliant System Memory – 4GB, 8GB or 16GB LPDDR4 Storage 64GB or 128GB eMMC 5.1 flash MicroSD […]

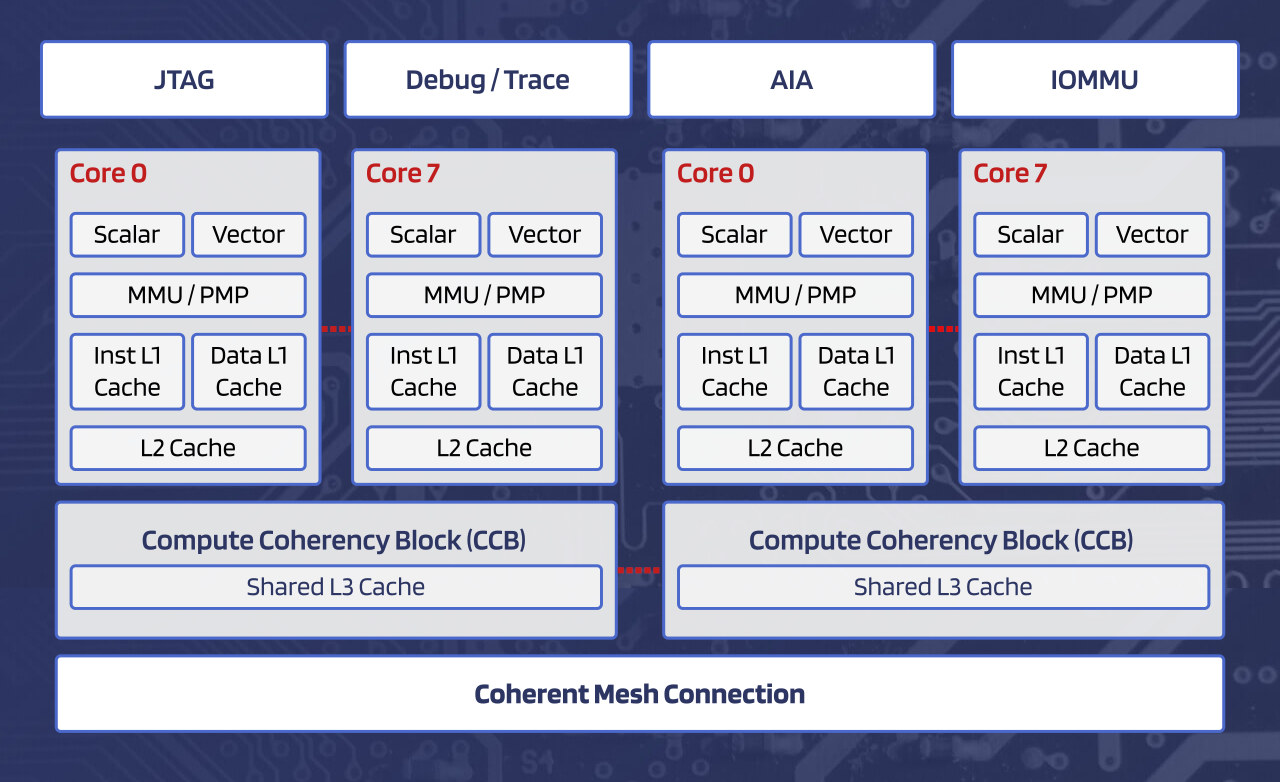

Akeana unveils 10 RISC-V cores suitable for microcontrollers up to data center chips

Founded about three years ago, Akeana has just officially launched and announced three 32-bit and 64-bit RISC-V processor lines and SoC IP with the Akeana 100 series for 32-bit microcontrollers, the Akeana 1000 series for 64-bit processors with MMU, and the Akeana 5000 series with much higher single-thread performance and designed for laptops, data centers, and cloud infrastructure. The company also introduced Scalable Coherent Interconnect, Interrupt Controller, and IOMMU IP for building out compute subsystems based on the aforementioned RISC-V cores, as well as AI-targeted Vector RISC-V Cores and Matrix Computation IP. The design team is said to have previously worked on Marvell’s ThunderX2 server chips. Akeana 100 Series The Akeana 100 Series is a line of highly configurable processors with 32-bit RISC-V cores that support applications from embedded microcontrollers to edge gateways, to personal computing devices. Four Akeana 100 RISC-V cores are available Akeana 110 for area- and power-constrained […]

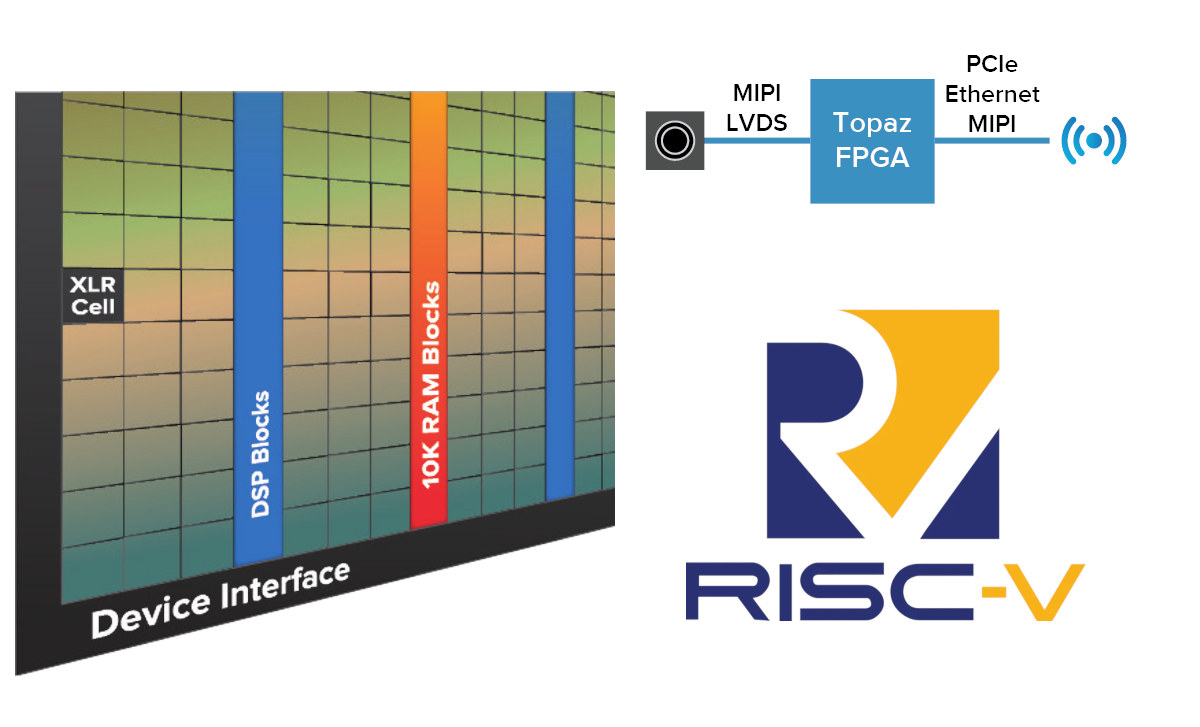

Efinix introduces the low-power Topaz RISC-V SoC FPGA family for “high-volume, mass-market applications”

Efinix Topaz is a new low-power RISC-V SoC FPGA family manufactured with the same 16nm TSMC process as the Efinix Titanium SoC FPGA, but optimized for high-performance in a low-power footprint, and targetting high-volume, mass-market applications. The Topaz SoC FPGAs provide fewer features than the Titanium family but still offer up to four RISC-V hard cores, PCIe Gen3, MIPI interfaces, LPDDR4, LVDS, and 12.5 Gbps transmitter with most features being optional and depending on the exact SKUs selected. Efinix Topaz key features and specifications: FPGA compute fabric Up to 326,080 logic elements (LEs) Up to 19.22 Mbits embedded memory Up to 1,877 10-Kbit SRAM blocks Up to 1,008 embedded DSP blocks Memory – 10-kbit high-speed, embedded SRAM, configurable as single-port RAM, simple dual-port RAM, true dual-port RAM, or ROM FPGA interface blocks Optional 32-bit quad-core hardened RISC-V block (RISCV32I with M, A, C, F, and D extensions and six pipeline […]

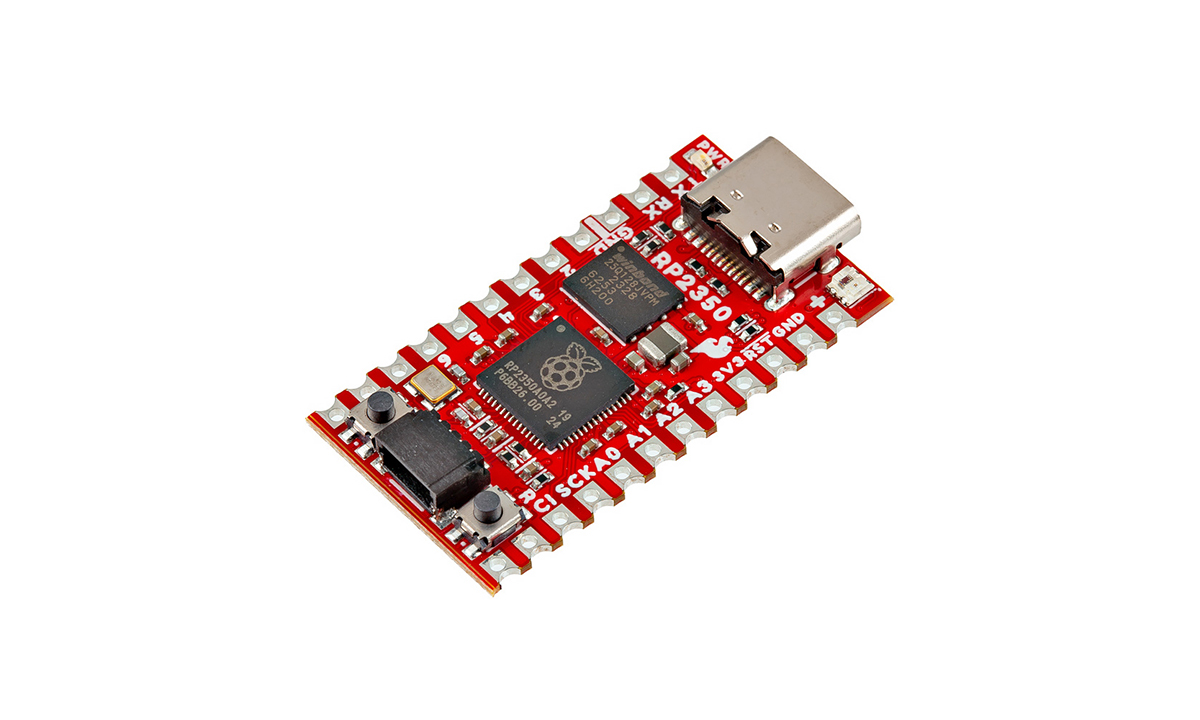

SparkFun Pro Micro – RP2350 development board comes with 16MB flash, 8MB PSRAM

The SparkFun Pro Micro – RP2350 is a compact and powerful development board built around the RP2350 chip from Raspberry Pi and equipped with 16MB flash and 8MB PSRAM. It follows the updated Pro Micro design and includes a USB-C connector, Qwiic connector, WS2812B RGB LED, Boot and Reset buttons, resettable PTC fuse, and both PTH and castellated solder pads. Last week, besides the Raspberry Pi Pico 2, we wrote about more boards with the Raspberry Pi RP2350, like the XIAO RP2350, Solder Party’s RP2350 Stamp, and Cytron MOTION 2350 Pro. Feel free to check them out if you are interested in these boards. SparkFun Pro Micro – RP2350 specification Microcontroller – Raspberry Pi RP2350A MCU CPU Dual-core Arm Cortex-M33 @150MHz with Arm Trustzone for secure boot Dual-core 32-bit Hazard3 RISC-V @ 150MHz Up to two cores can be used at the same time Memory – 520 KB on-chip SRAM […]

MILK-V Jupiter review – A RISC-V mini-ITX motherboard and PC tested with Ubuntu-based Bianbu OS

In this review or preview of the the Shenzhen Milk-V Jupiter RISC-V mini-ITX motherboard, I’ll assemble the motherboard into a mini-ITX chassis, before installing the Ubuntu 23.10 Mantic-based Bianbu OS optimized for RISC-V platforms, and testing the device to see how much progress has been done on RISC-V since I tested the StarFive VisionFive 2 SBC with Debian 12 about 18 months ago. In the first part of the review, we checked out the Radxa ROCK 5 ITX (Rockchip RK3588 Arm) and Jupiter (SpacemIT K1 RISC-V) mini-ITX motherboards with specifications and unboxing, and the Auriga 6-Bay NAS mini-ITX chassis used in this review. I planned to start with the Radxa ROCK 5 ITX, but due to logistics and technical issues, I went ahead testing the RISC-V motherboard first. Installing Bianbu OS to the Jupiter RISC-V motherboard The board does not come with storage, so no operating system is installed. So […]