A few years ago, we came across GigaDevice GD32 microcontroller compatible with STMicro STM32F103, but with a higher 108 MHz clock, and zero wait state internal flash. The MCU was also a drop-in replacement for the STMicro alternative since beside being software compatible, it was also pin-to-pin compatible. The company is now back with a new microcontroller, but it’s not Arm-based. Instead, GigaDevice GD32V is based on RISC-V open source architecture. GD32V General Purpose RISC-V MCU GigaDevice GD32V is a 32-bit RISC-V general-purpose MCU that targets industrial and consumer applications such as IoT, edge computing, artificial intelligence and “vertical industries”. The new GD32VF103 series RISC-V MCU family features 14 models with the following key specifications: Core – GD32VF103 32-bit rv32imac RISC-V “Bumblebee Core” @ 108 MHz Memory – 8KB to 32KB SRAM Storage – 16KB to 128KB flash Peripherals – USB OTG and CAN 2.0B I/O – 3.3V, 5V tolerant […]

Getting Started with Sipeed M1 based Maixduino Board & Grove AI HAT for Raspberry Pi

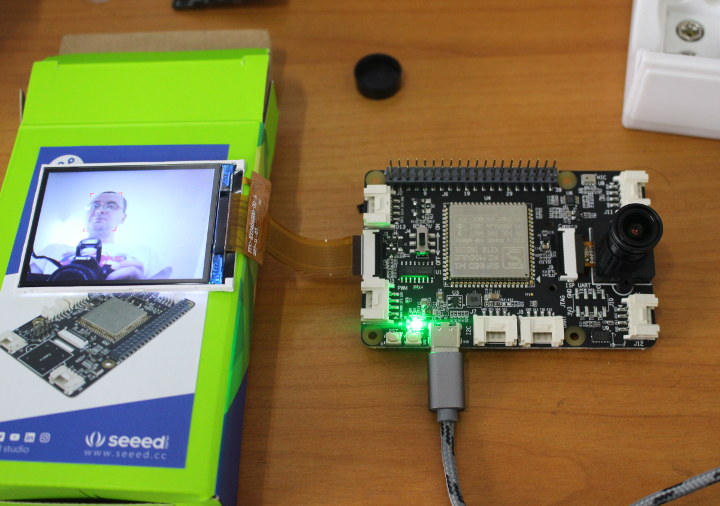

Last year we discovered Kendryte K210 processor with a RISC-V core and featuring AI accelerators for machine vision and machine hearing. Soon after, Sipeed M1 module was launched with the processor for aroud $10. Then this year we started to get more convenient development board featuring Sipeed M1 module such as Maixduino or Grove AI Hat. Seeed Studio sent me the last two boards for review. So I’ll start by showing the items I received, before showing how to get started with MicroPython and Arduino code. Note that I’ll be using Ubuntu 18.04, but development in Windows is also possible. Unboxing I received two packages with a Maixduino kit, and the other “Grove AI HAT for Edge Computing”. Grove AI HAT for Edge Computing Let’s start with the second. The board is a Raspberry Pi HAT with Sipeed M1 module, a 40-pin Raspberry Pi header, 6 grove connectors, as well […]

M5Stack M5StickV is a Tiny AI Camera for Maker Projects

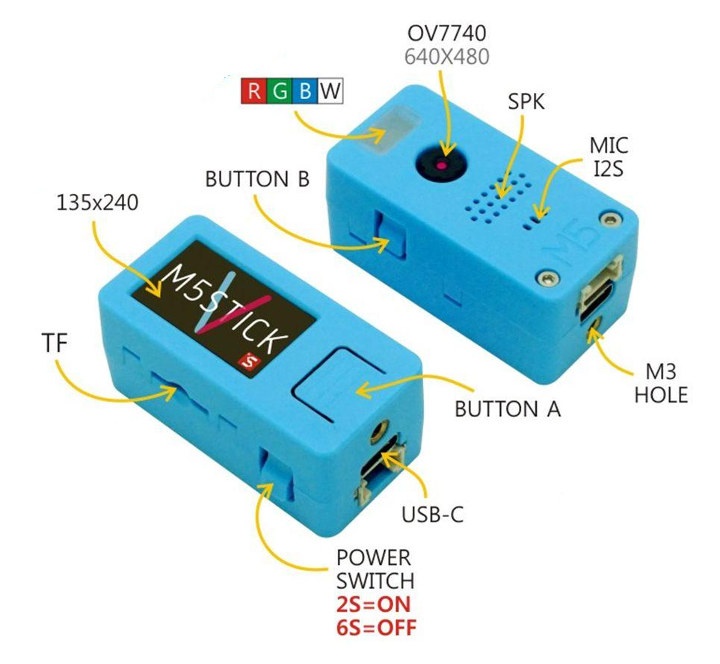

I’ve just started to play with Maixduino board based on ESP32 WiSoC and Sipeed M1 module that enables AI tasks such as object detection thanks to built-in AI accelerators found in Kendryte K210 RISC-V processor and noticed references to M5Stack M5StickV in firmware file names. Somehow I never wrote about M5Stack, but the company provides modular ESP32 IoT development boards that can be stacked with various modules to easily and quickly build prototypes. M5StickV is one of those modules and is similar to Maixduino kit with camera and display, minus WiFi + Bluetooth connectivity, except that everything nicely packed into a cute module. M5StickV hardware specifications: SoC – Kendryte K210 dual-core 64-bit RISC-V processor @ 400MHz with dual independent double-precision FPU, 8MB on-chip SRAM, Neural Network Processor (KPU) @ 0.8Tops, Field-Programmable IO Array (FPIOA), and more Storage – 16MB flash, microSD card slot Display -1.14″ SPI display with 240×135 resolution […]

Embedded Linux Conference (ELC) Europe 2019 Schedule – October 28-30

I may have just written about Linaro Connect San Diego 2019 schedule, but there’s another interesting event that will also take place this fall: the Embedded Linux Conference Europe on October 28 -30, 2019 in Lyon, France. The full schedule was also published by the Linux Foundation a few days ago, so I’ll create a virtual schedule to see what interesting topics will be addressed during the 3-day event. Monday, October 28 11:30 – 12:05 – Debian and Yocto Project-Based Long-Term Maintenance Approaches for Embedded Products by Kazuhiro Hayashi, Toshiba & Jan Kiszka, Siemens AG In industrial products, 10+ years maintenance is required, including security fixes, reproducible builds, and continuous system updates. Selecting appropriate base systems and tools is necessary for efficient product development. Debian has been applied to industrial products because of its stability, long-term supports, and powerful tools for packages development. The CIP Project, which provides scalable and […]

HuskyLens AI Camera & Display Board is Powered by Kendryte RISC-V Processor (Crowdfunding)

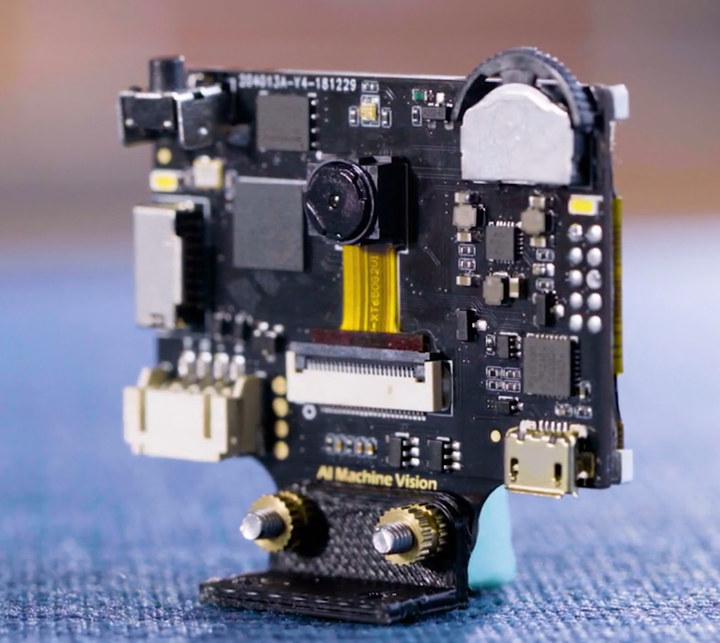

A couple of years ago, I reviewed JeVois-A33 computer vision camera powered by Allwinner A33 quad-core Cortex-A7 processor running Linux. The tiny camera would implement easy-to-use software for machine vision with features such as object detection, eye tracking, QR code and ArUco marker detection, and so on. The camera could handle the tasks at hand, but since it relied on purely software computer vision, there were lag for some of the demo applications including 500ms for single object detection, and up to 3 seconds for YOLO test with multiple object types using deep learning algorithms. That’s a bit slow for robotics project, and software solutions usually consume more than hardware accelerated ones. Since then, we’ve started to see low-cost SoC and hardware with dedicated hardware AI accelerators, and one of those is Kendryte K210 dual-core RISC-V processor with a built-in KPU Convolutional Neural Network (CNN) hardware accelerator and APU audio […]

Alibaba Unveils XuanTie 910 16-core RISC-V Processor

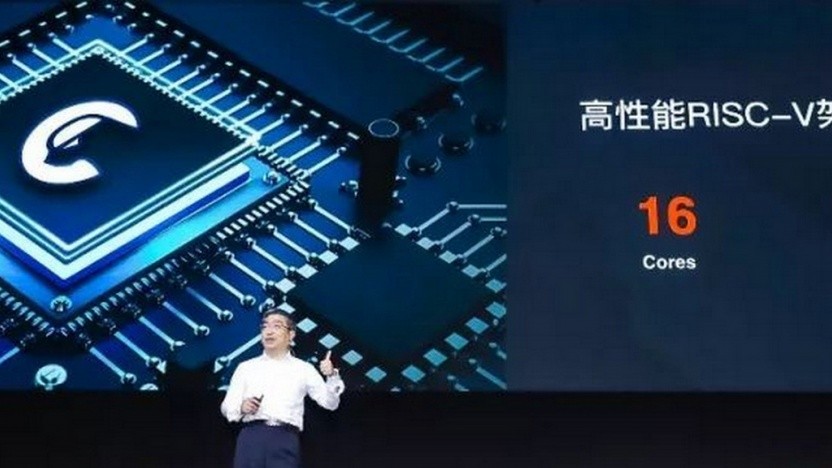

When Pingtou Ge (Brother Pingtou) Semiconductor Co. was founded by Alibaba in September 2018, the vision was to create groundbreaking chips for production. The company had once been Zhongtianwei, a chip company, which was acquired by Alibaba in April 2018 along with team Aha. On July 25, 2019, it was announced that Brother Pingtou had released the XuanTie 910 (Black Iron 910) 16-Core RISC-V Processor. The company has reported that the processor will be integrated into high-performance end to end 5G chips, AI, and autonomous driving applications. There are conflicting reports that the processor is also known as T-Head, although its name means Black Iron. There has been no firm release date or price as of yet. Open-source technologies are being adopted on a regular basis in China, and the XuanTie 910 is being offered to developers with encouragement to use Berkeley-based open-source ISA with very few intellectual property restrictions. […]

Linux 5.2 Release – Main Changes, Arm, MIPS & RISC-V Architectures

Linus Torvalds announced the release of Linux 5.2 last Sunday: So I was somewhat pre-disposed towards making an rc8, simply because of my travels and being entirely off the internet for a few days last week, and with spotty internet for a few days before that [*]. But there really doesn’t seem to be any reason for another rc, since it’s been very quiet. Yes, I had a few pull requests since rc7, but they were all small, and I had many more that are for the upcoming merge window. Part of it may be due to the July 4th week, of course, but whatever – I’ll take the quiet week as a good sign. So despite a fairly late core revert, I don’t see any real reason for another week of rc, and so we have a v5.2 with the normal release timing. There’s no particular area that stands […]

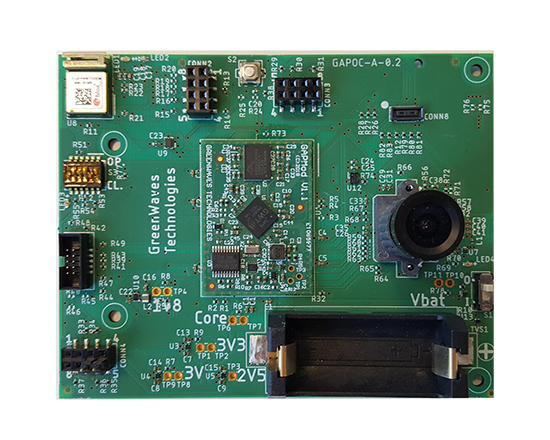

GAPPoc AI development boards based on the GAP8 RISC-V Chip

GreenWaves has developed a development board based on the GAP8 chip which can be evaluated from a GAPuino board, a generic board that can run off a low power external power source or USB and is compatible with the Arduino ecosystem. Recently the company moved beyond the generic board to the GAPPoc, platform which stands for GAP8 Proof of Concept. The GAPPoc is focused on a class of applications which can be embedded on a single board and able to carry hardware such as crystal or external memory, sensors, a radio fit, and a battery. The board will be geared towards a set of low power functions for a particular class of applications. This is a family of boards designed to increase the range of abilities in edge Artificial Intelligence. At this time there is only a single board with a platform to enhance AI, targeting Computer Vision in the […]