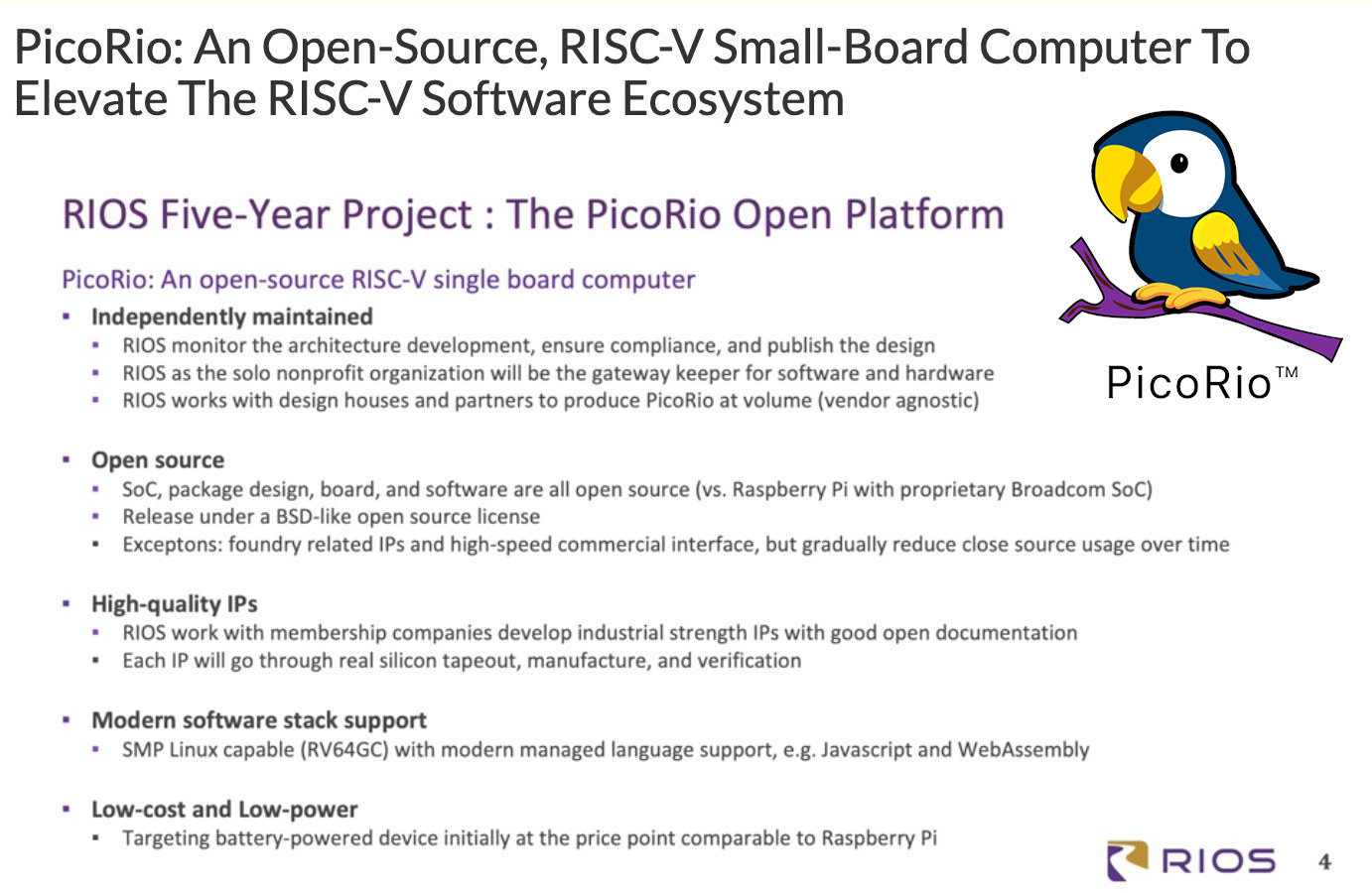

There’s a lot of interest/hype around RISC-V, and low-cost boards such as Longan Nano or Maixduino are already available, but those are based on microcontroller-class chips, even though it’s possible to run Linux on Kendryte K210 RISC-V board, it comes without MMU, so it’s not for everyone. Linux capable RISC-V boards do exist but cost several hundred dollars or more with the likes of HiFive Unleashed and PolarFire SoC Icicle development kit. If only there was a RISC-V board similar to the Raspberry Pi board and with a similar price point… The good news is that the RISC-V International Open Source (RIOS) Laboratory is collaborating with Imagination technologies to bring PicoRio RISC-V SBC to market at a price point similar to Raspberry Pi. The PicoRio board was presented at the RISC-V Global Forum on September 3rd. I could not find the full presentation slides yet, but there are some screenshots […]

RISC-V & ESP32 based TTGO Handheld T-WATCH K210 AIoT DevKit Works with a 9V Battery

LilyGO TTGO T-Watch K210 AIOT is a rather thick watch development kit based on Kendryte K210 RISC-V AI Processor and ESP32 WiSoC capable of performing AI workloads such as face detection using a USB power source. We first covered the development kit in June, and the company releases some small variants from time to time with the latest being TTGO Handheld T-Watch K210 with basically the same hardware, plus the addition of a handle that adds a power button, and a compartment for a 9V battery to power the watch/devkit. TTGO Handheld T-Watch K210 specifications: SoC – Kendryte K210 dual-core 64-bit RISC-V processor with 8MB RAM, AI accelerators Storage – 16MB flash, MicroSD card slot Display – 1.54-inch capacitive touch IPS screen connected over an 8080 interface Camera – Adjustable 2MP OV2640 sensor with 65-degree lens (optional 120-degree angle lens), AS312 “human” infrared sensor Connectivity – 2.4 GHz 802.11b/g/n WiFi […]

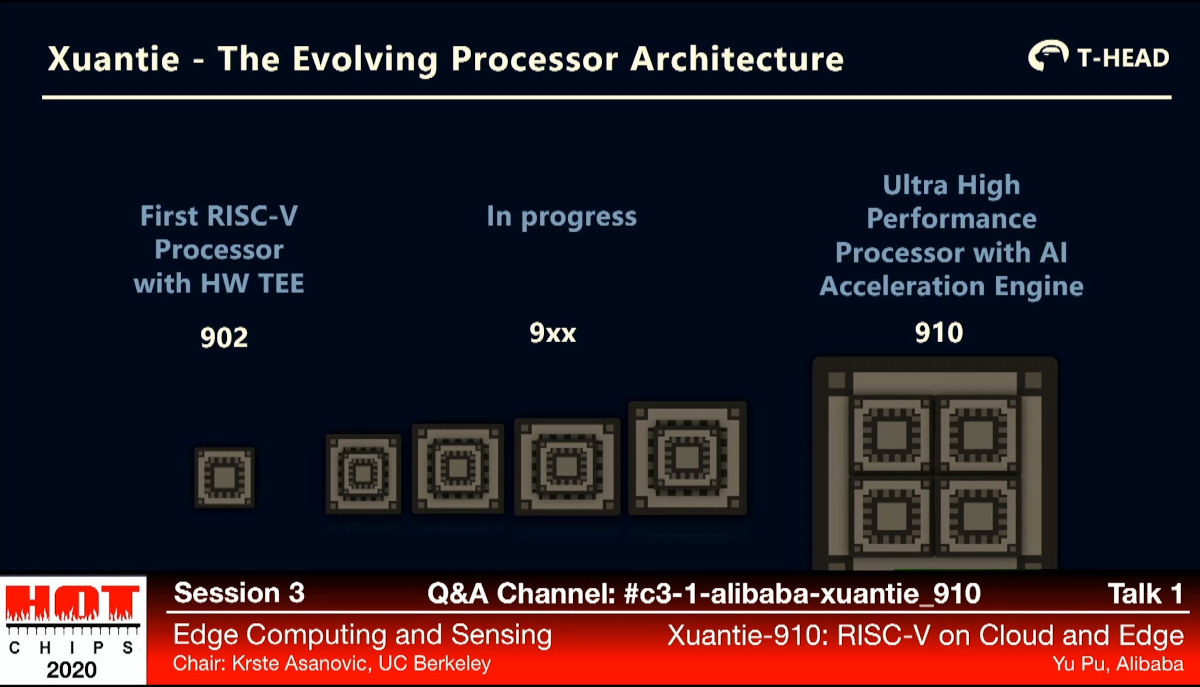

More Details about Alibaba XT910 64-bit RISC-V Core

Alibaba unveiled XuanTie 910 16-core RISC-V Processor last year with few details except it targetted high-performance 5G, AI, and autonomous driving applications. The company has now provided more details about Alibaba XuanTie 910 (aka XT910) processor during the virtual Hot Chips 2020 conference, and he notably compared the RV64GCV core found in the processor to Arm Cortex-A73 core. Alibaba XT910 main features and specifications: CPU – Up to 16x 64-bit RISC-V (RV64GCV) cores with RISC-V Vector extension and custom Turbo extension in four clusters of four cores; 12-stage out of order; Coremark: 7.1 per MHz Cache – 32KB or 64KB I/D cache per core, up to 8MB L2 cache per cluster FP16-FP64 floating-point unit Vector Computing Unit (aka Vector Engine) for AI acceleration Memory Management – Sv39 MMU + 8/16 PMP Interrupt Controller – Clint + PLIC Process – Final: 12nm FinFET; engineering samples: TSMC 28nm HPC Alibaba RISC-V Turbo […]

Sipeed Maix Amigo is a Portable 64-bit RISC-V AI Development Kit with Display and Cameras

Earlier this year, Seeed Studio introduced Wio Terminal a portable Arduino devkit with an LCD display, and expansion connectors and headers. The company is now selling a similar looking devkit but for different applications with Sipeed Maix Amigo portable 64-bit RISC-V development kit powered by Kendryte K210 RISC-V AI processor and equipped with an LCD display, two cameras, a few buttons, and several I/O headers and Grove connectors. Sipeed Maix Amigo specifications: SoC – Kendryte K210 Dual-core 64-bit RISC-V (RV64GC) processor with FPU @ 400 MHz (overclockable to 500MHz), 8MB SRAM, built-in AI accelerators for video and audio Storage – 16MB Flash, MicroSD card slot up Display – 3.5-inch TFT capacitive touch screen display with 480×320 resolution Camera VGA front-facing camera up to 30 fps (GC0328 sensor) VGA rear camera up to 60 fps (OV7740 sensor) Audio – Build-in microphone, optional 6-mic array USB – 1x USB Type-C port for […]

Linux 5.8 Release – Main Changes, Arm, MIPS, and RISC-V Architectures

Linus Torvalds has just released Linux 5.8: So I considered making an rc8 all the way to the last minute, but decided it’s not just worth waiting another week when there aren’t any big looming worries around. Because despite the merge window having been very large, there really hasn’t been anything scary going on in the release candidates. Yeah, we had some annoying noise with header file dependencies this week, but that’s not a new annoyance, and it’s also not the kind of subtle bug that keeps me up at night worrying about it. It did reinforce how nice it would be if we had some kind of tooling support to break nasty header file dependencies automatically, but if wishes were horses.. Maybe some day we’ll have some kind of SAT-solver for symbol dependencies that can handle all our different architectures and configurations, but right now it’s just a manual […]

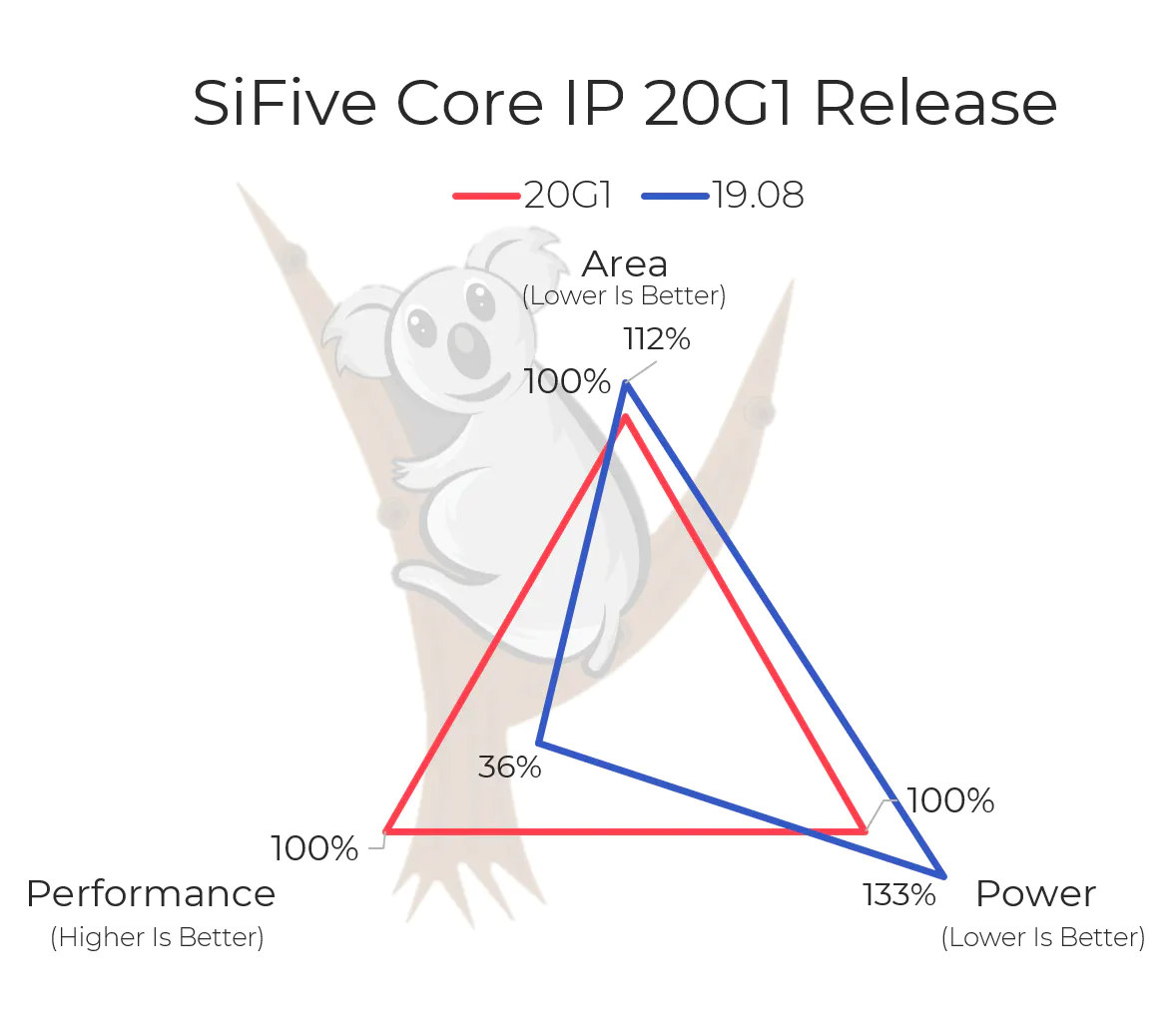

SiFive RISC-V Processors Get Performance & Efficiency Improvements, Smaller Footprint with 20G1 Release

SiFive RISC-V cores portfolio ranges from low power 32-bit IoT processors to more powerful, Linux-capable 64-bi RISC-V cores like the latest SiFive U84/U87 cores rivaling with Arm Cortex-A7x cores. SiFive Core IP 20G1 release further enhances the company’s existing RISC-V cores with performance improvements, higher efficiency, and a smaller footprint. Specifically, SiFive claims the SiFive U7-Series has increased load bandwidth up to 2.8x for memory-intensive workloads such as AI inference processing, and all of the company’s RISC-V cores can now run at lower power, with the SiFive U74 standard core running at up to 25% lower power while running Dhrystone benchmark. The SiFive E-Series processors which feature real-time capability are now available with the RISC-V Embedded extension (RV32E) which reduces the footprint compared to RV32I ISA with for instance up to 11% smaller area for the SiFive E3-Series. RV32E and RV32I have the same instructions set, but RV32E comes with […]

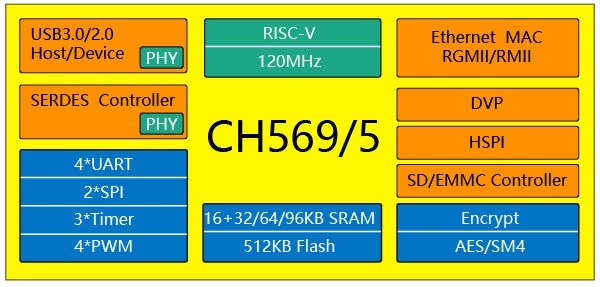

WCH CH569 RISC-V SoC Offers USB 3.0, Gigabit Ethernet, High-Speed SERDES & HSPI Interfaces

RISC-V open architecture has made its way into low-cost low power general purpose MCUs such as Gigadevices GD32V or WCH CH32V103, Western Digital hard drives, some AI processors notably Kendryte K210, and even Linux capable boards including Microsemi’s PolarFire SoC Icicle kit. But more applications featuring RISC-V architecture are coming with, for instance, WCH CH569 RISC-V processor featuring USB 3.0, Gigabit Ethernet, DVP camera, and 1.25 SERDES block all managed by a RISC-V core clocked at 120 MHz. CH569 (and CH565) processor key features and specifications: CPU – RISC-V (RISC-V3A) core @ 120MHz with hardware multiplication and division, programmable interrupt controller, low-power two-stage pipeline Memory – 16KB 32-bit SRAM, 32/64/96KB configurable 128-bit SRAM Storage Internal – 448KB code flash, 32KB data flash External – SD/eMMC controller with single-wire, 4-wire, 8-wire data communication mode. Complies with eMMC card 4.4 and 4.5.1 specifications, and compatible with 5.0 specifications Networking – Gigabit Ethernet […]

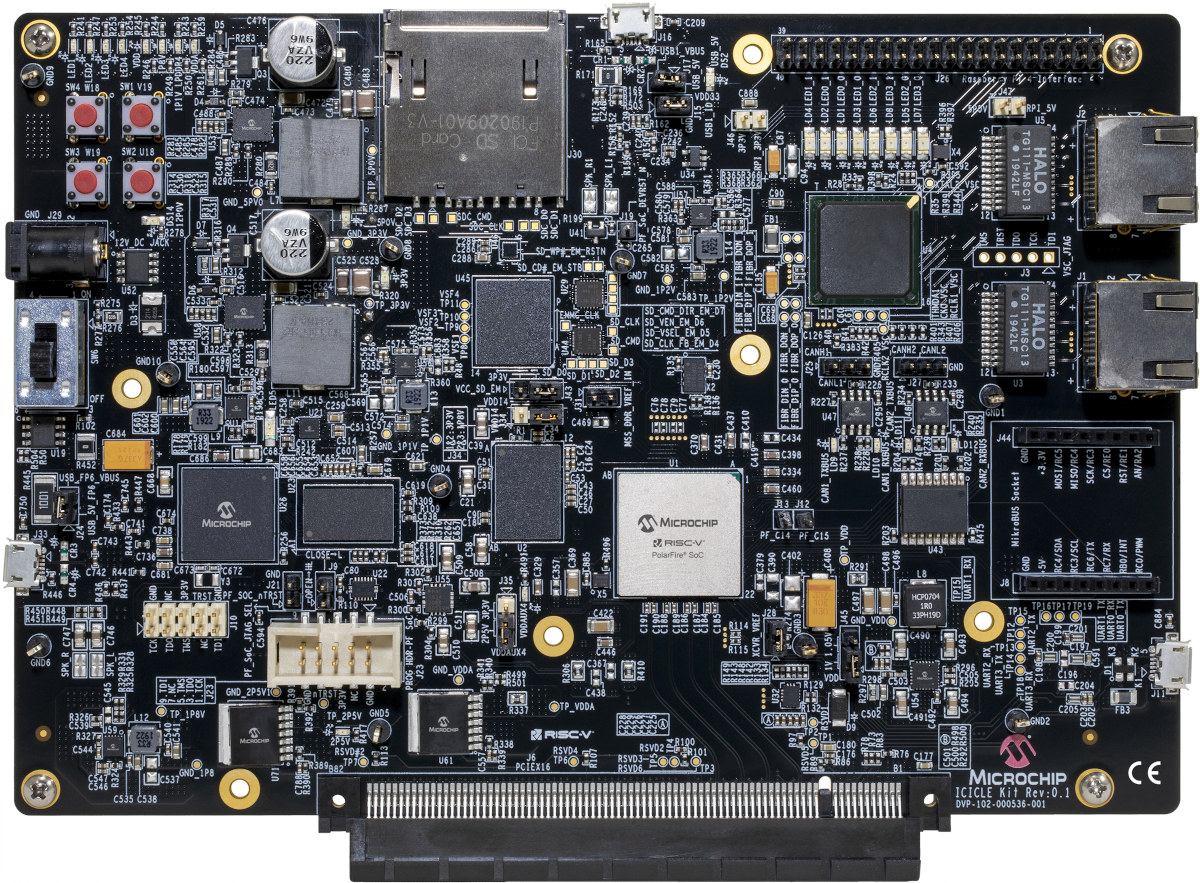

PolarFire SoC Icicle 64-bit RISC-V and FPGA Development Board Runs Linux or FreeBSD (Crowdfunding)

We got some more details about PolarFire RISC-V FPGA SoC late last year, and we were promised a Linux capable 64-bit RISC-V & FPGA development board with PolarFire SoC Icicle kit in Q3 of 2020. We are already in July 2020. So where is the board? Oh, look! It’s right here on Crowd Supply where it is offered for $499, and shipping is expected to start in mid-September. PolarFire SoC Icicle specifications: SoC FPGA – PolarFire SoC MPFS250T-FCVG484EES penta–core RISC-V CPU subsystem (1xRV64IMAC, 4xRV64GC) with 254K LE non-volatile fabric, 784 18 × 18 math blocks, secure boot, 4x 12.7 Gbps SERDES, FCVG484 package (19 × 19 mm, 0.8 mm pitch) System Memory – 2GB LPDDR4 x32 Storage – 1 GBit QSPI Flash, 8GB eMMC Flash or SD card slot (multiplexed) Video Output – HDMI 2.0 (removed from final board) Connectivity – 2x Gigabit Ethernet, Wi-Fi, and Bluetooth USB – 1x […]