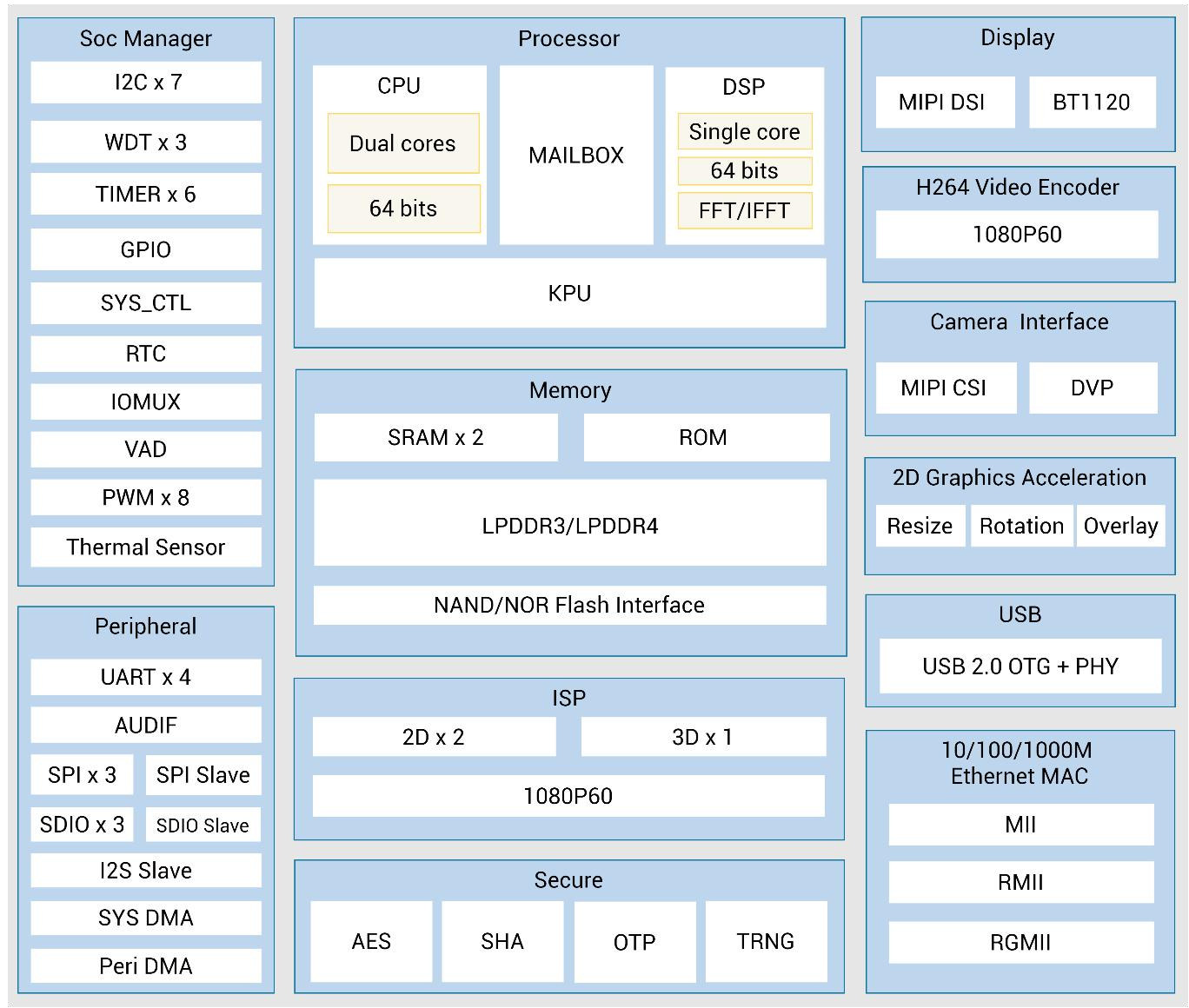

Kendryte K510 is a 64-bit tri-core RISC-V processor clocked at up to 800 MHz with AI accelerators that succeed the 400 MHz Kendryte K210 dual-core RISC-V AI processor released a few years ago first in Kendryte KD233 board, and then boards like Maxduino or Grove AI HAT conveniently programmable with Arduino or Micropython. Canaan formally announced the processor yesterday at the 2021 World Artificial Intelligence Conference claiming K510 had three times the performance of K210 making it suitable for UAV high-definition aerial photography, high-definition panoramic video conferences, robotics, STEAM education, driver assistance scenarios, and industrial and professional cameras. The press release did not have much information, but multiple sources provided additional details to CNX Software, so we have Kendryte K510 specifications: Processor – 2x 64-bit RISC-V processor @ 800 MHz, and 1x 64-bit RISC-V core @ 800 MHz with DSP extension AI subsystem with 3 TOPS in total KPU: General […]

XiangShan open-source 64-bit RISC-V processor to rival Arm Cortex-A76

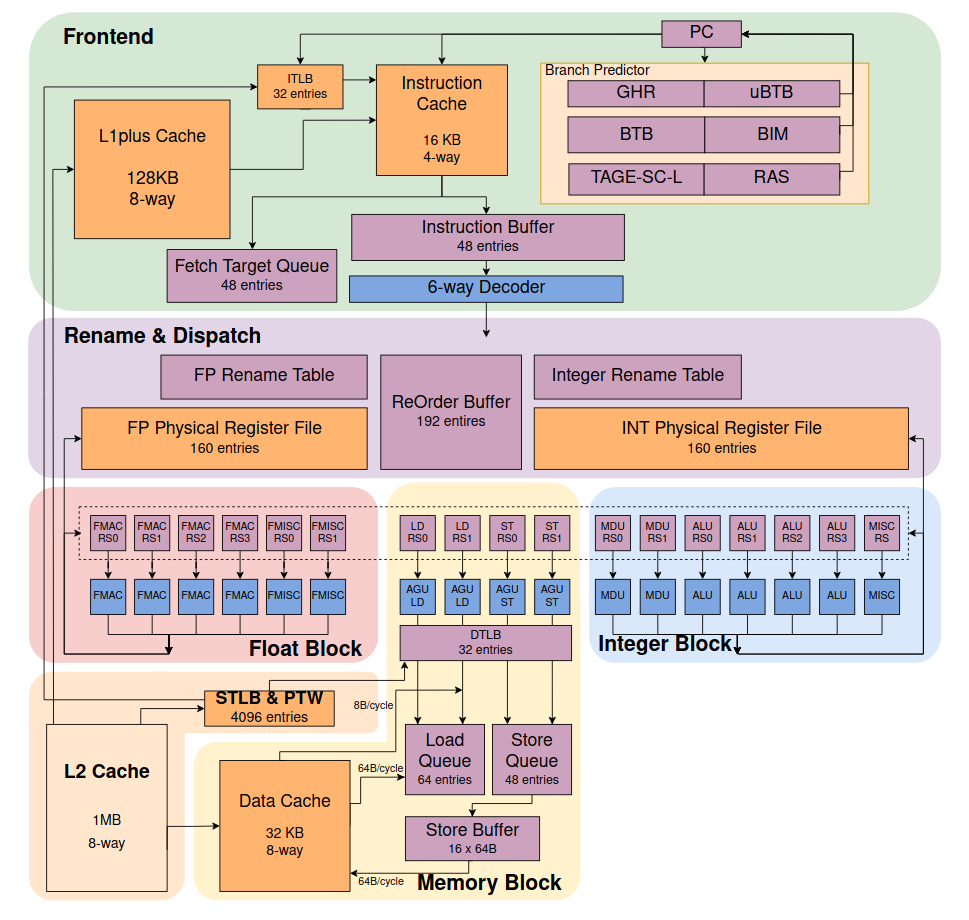

SiFive Performance P550 was supposed to be the most powerful RISC-V core to date, capable of outperforming Arm’s Cortex-A75 core in raw performance, but especially in terms of efficiency, with three times the performance per mm2. But there may be an even more powerful RISC-V processor, albeit developed as a research project, with the Chinese Academy of Science (CAS)’s XiangShan open-source processor presented at the recent RISC-V World Conference China 2021 with the goal of matching Cortex-A76 performance. The project was launched on June 11, 2020, and 25 classmates and teachers participated in the development of Xiangshan with 821 main branch code mergers, 3296 code submissions, more than 50,000 lines of code, and more than 400 documents, mostly in Chinese only for now. This culminated with an 8-core prototype built based on Yanqihu (雁栖湖) architecture using TSMC’s 28nm process with the processor running up to 1.2 or 1.3 GHz that […]

Linux 5.13 Release – Notable changes, Arm, MIPS and RISC-V architectures

Linus Torvalds has just announced the release of Linux 5.13: So we had quite the calm week since rc7, and I see no reason to delay 5.13. The shortlog for the week is tiny, with just 88 non-merge commits (and a few of those are just reverts). It’s a fairly random mix of fixes, and being so small I’d just suggest people scan the appended shortlog for what happened. Of course, if the last week was small and calm, 5.13 overall is actually fairly large. In fact, it’s one of the bigger 5.x releases, with over 16k commits (over 17k if you count merges), from over 2k developers. But it’s a “big all over” kind of thing, not something particular that stands out as particularly unusual. Some of the extra size might just be because 5.12 had that extra rc week. And with 5.13 out the door, that obviously means […]

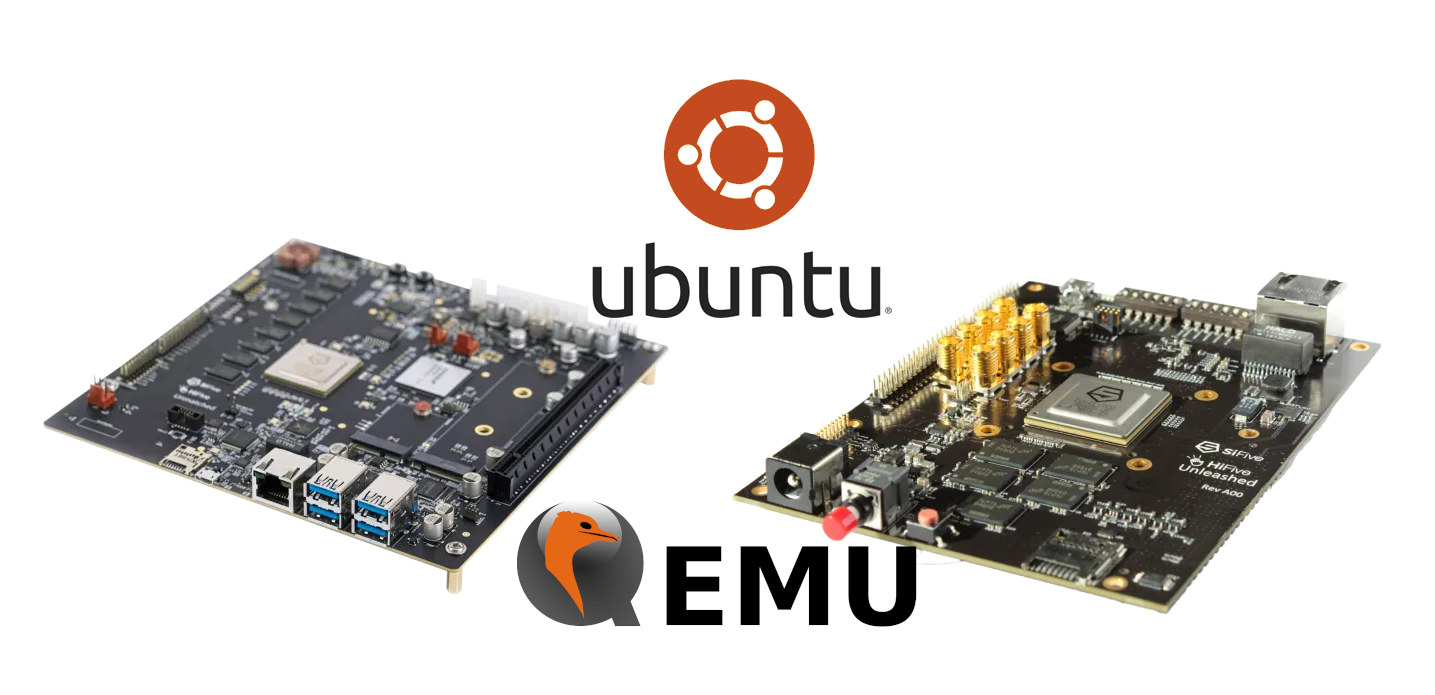

Ubuntu 20.04/21.04 64-bit RISC-V released for QEMU, HiFive boards

Let’s a lot of excitement around RISC-V open architecture, but a lot of work still needs to be done to bring the ecosystem to level with Arm or x86 architecture from the silicon to the software. Progress is made step-by-step and one of these steps is Canonical released Ubuntu 64-bit RISC-V (RISCV64) images for some of SiFive HiFive boards, as well as QEMU open-source emulator. Specifically, Canonical released an Ubuntu 20.04.2 LTS image for HiFive Unleashed & QEMU, and an Ubuntu 21.04 image for HiFive Unleashed, HiFive Unmatched, and QEMU. Note those are only server images, and there’s no desktop image yet like for Ubuntu 21.04 on Raspberry Pi 2/3/4. It’s been possible to run RISC-V Linux in QEMU for at least three years, but when I tried it was a minimal system based on Busybox, so let’s try again with Ubuntu 21.04 following the instructions provided on Discourse. I […]

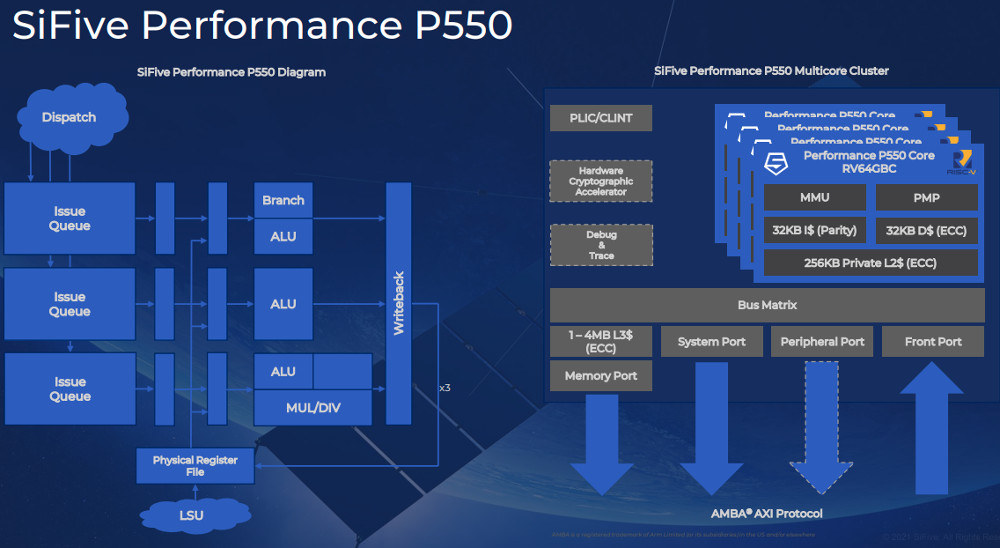

SiFive Performance P550 is the fastest 64-bit RISC-V processor so far

SiFive has announced two RISC-V “Performance” cores with Performance P550 that should be the fastest 64-bit RISC-V processor so far with a SPECInt 2006 score of 8.65/GHz, as well as a Performance P270 Linux capable processor with full support for the RISC-V vector extension v1.0 rc. SiFive Performance P550 P550 highlights: RISC-V RV64GBC ISA 13 stage, 3-issue high-performance out-of-order pipeline Supports multicore coherence with up to 4 cores in a core complex Private 32KB+32KB L1 cache and a private 256KB L2 cache per core Up to 4MB L3 cache in a four-core cluster SPECint 2006 – 8.65/GHz 2.4 GHz in 7nm with a footprint of less than 0.25 mm SiFive compares the Performance P550 core to Arm’s Cortex-A75 with higher performance in SPECint2006 and SPECfp2006 integer/floating-point benchmark, all a much smaller area which would enable a quad-core P550 cluster on about the same footprint as a single Cortex-A75 core. There […]

$3.5 RV-Debugger Plus UART & JTAG debug board comes with BL702 Zigbee & BLE RISC-V SoC

USB to UART debug boards are a necessity for anyone playing with single board computers, at least when using bleeding-edge bootloader or Linux kernel where the target board may not always boot, or when troubleshooting booting problems. Those are often based on FDTI or WCH chips, but Sipeed RV-Debugger Plus features Bouffalo Lab BL702 Zigbee & Bluetooth LE RISC-V SoC instead and offers both UART and JTAG interfaces. So let’s have a look at both the board and SoC. Sipeed RV-Debugger Plus USB to TLL debug boards are meant to be simple and that’s the case for Sipeed latest BL702 board as it comes with a 12-pin connector with Tx/Rx for UART, 8 signals for JTAG, plus 5V, 3.3V, and GND power signals. We can also see pads for Tx/Rx/CTS, a boot button, a crystal oscillator, and a USB-C port to connect to the host computer. What I don’t see […]

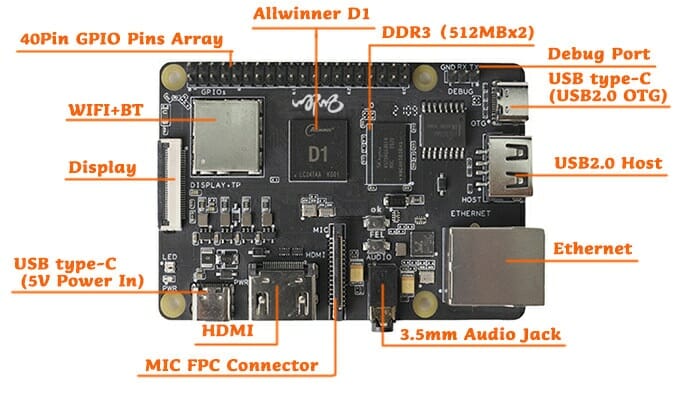

Nezha RISC-V Linux SBC launched for $99 and up

Last month, we wrote about Allwinner D1 SBC & processor that promised to offer a relatively low-cost RISC-V Linux solution. We were not given a name at the time, but there was a logo of Nezha, a fictional character from Chinese literature. The board is now known as the Nezha SBC and has been launched on Indiegogo for $99 and up as a board designed for IoT projects running Linux, but can also be purchased directly on Aliexpress for the same price. [Update: It can also be purchased on Taobao for 599 RMB] Nezha SBC specifications: SoC – Allwinner D1 single-core XuanTie C906 64-bit RISC-V processor @ 1.0 GHz with HiFi4 DSP, G2D 2D graphics accelerators Memory – 1GB DDR3 memory Storage – 256MB SPI NAND flash, MicroSD card slot Video Output – HDMI 1.4 port up to 4Kp30, MIPI DSI & touch panel interface up to 1080p60 Decoding – […]

RISC-V International to give away 1,000 RISC-V development boards

The best way for a new platform to get good software support is to bring hardware into the hands of developers. That’s exactly what RISC-V International is doing by inviting developers to sign up for a RISC-V developer board sponsored by RISC-V and contributing members. There are 1,000 boards on offer with 1GB to 16GB RAM depending on the target project from five companies and organizations namely Allwinner, Beagleboard.org, SiFive, Microchip Technology (previously Microsemi), and RIOS. Here are the stated goals of the giveaway: Spur innovation Enable new opportunities for the next generation of developers to work with the RISC-V ISA Provide a platform For testing To write programs that run on RISC-V Develop software Integrate existing software stacks Optimize ecosystem software Share feedback on the product such as ease to integrate software stacks, develop and test extensions, etc. The company did not provide an exact list of development board […]