StarFive has just announced customers’ delivery of the 64-bit RISC-V Dubhe core based on RV64GC ISA plus bit manipulation, user-level interrupts, as well as the latest Vector 1.0 (V) and Hypervisor (H) instructions. StarFive Dubhe can be clocked up to 2 GHz on a 12nm TSMC process node, and the company also released performance numbers with a SPECint2006 score of 8.9/GHz, a Dhrystone score of 6.6 DMIPS/MHz, and a CoreMark score of 7.6/MHz. A third-party source told CNX Software it should be equivalent to the SiFive Performance P550 RISC-V core announced last summer, itself comparable to Cortex-A75. StarFive Dubhe highlights: Typical frequency – 2.0 GHz @ TSMC 12nm “Industry-leading” Power and Area Efficiency (TSMC 12nm) RISC-V Vector Extension Data types: floating point, fixed point and integer VLEN=128-1024bits ALU & data path width=128 or 256 bits Full vector register grouping (LMUL) support RISC-V Virtualization Extension Pre-integrated Multi-Core with Memory Coherency Support […]

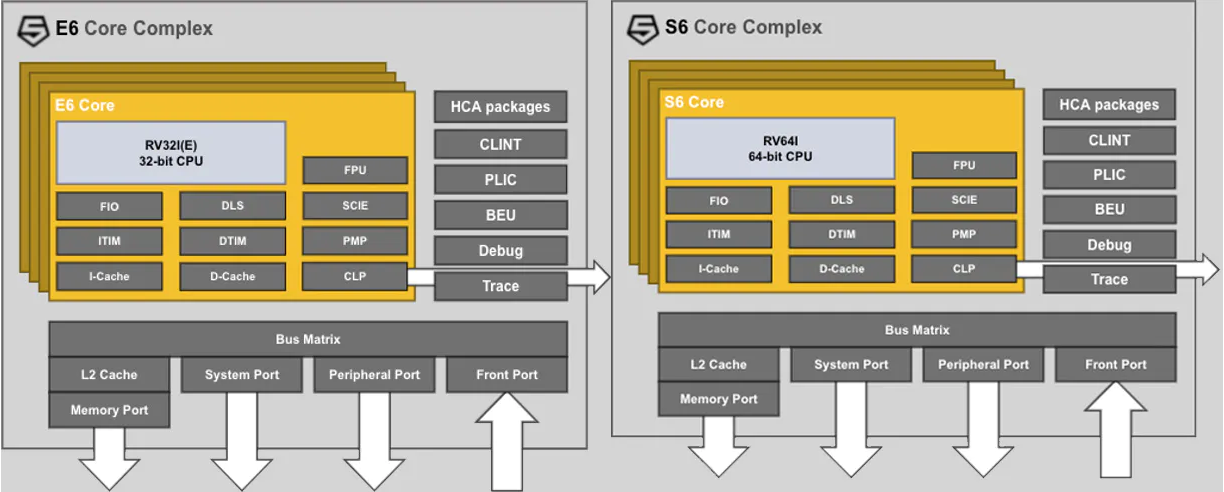

Sifive Essential 6-Series RISC-V processors target Linux, real-time applications

SiFive has been busy. Just a few days after SiFive Performance P650 announcement, the company has announced the SiFive Essential 6-Series RISC-V processor family starting with four 64-bit/32-bit real-time core, and two Linux capable application cores, plus the SiFive 21G3 release with various improvements to existing families. SiFive Essential 6-Series range of RISC-V processors There Essential 6-Seris family is comprised of three sub-families with two processors each: E6 Series with 1.91 DMIPS/MHz, 3.69 CoreMark/MHz E61-MC – Quad-core 32-bit embedded processor E61 – Mid-range performance 32-bit embedded processor (one-core) S6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz S61-MC – Quad-core 64-bit embedded processor S61 – Mid-range performance 64-bit embedded processor (one-core) U6 Series with 2.07 DMIPS/MHz, 3.73 CoreMark/MHz U64-MC – Quad-core 64-bit application processor U64 – Mid-range performance Linux-capable processor (one-core) E6-Series and S6 Series real-time processors have practically the same features except for the 32-bit and 64-bit cores, and a different […]

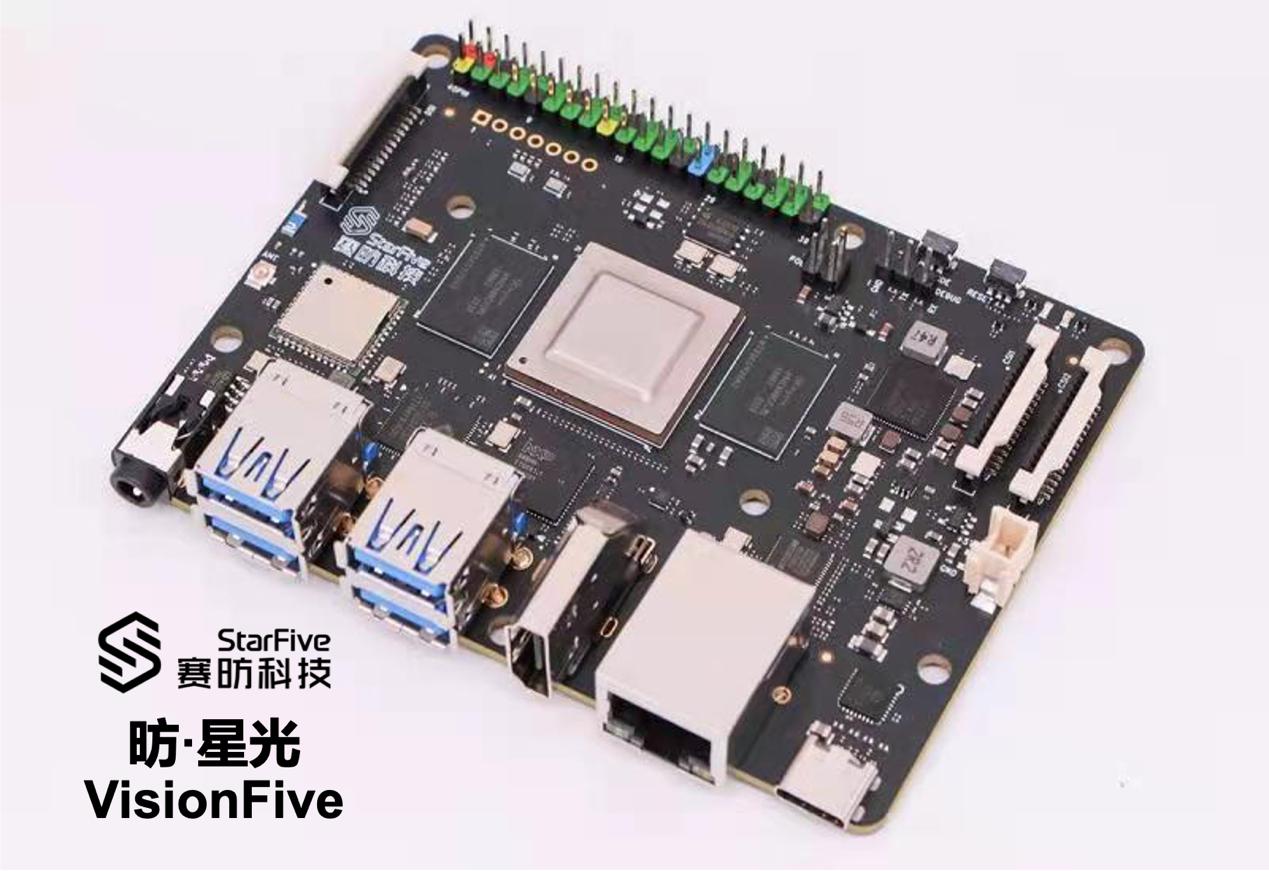

StarFive VisionFive single board computer officially for sale, accelerating RISC-V ecosystem development (Sponsored)

San Francisco, U.S. – Dec. 8, 2021- at RISC-V Summit 2021, StarFive Technology Co., Ltd. (hereinafter “StarFive”), the leader of RISC-V software and hardware ecosystem in China, announced that “VisionFive” single-board computer is officially for sale. The availability of VisionFive signifies a breakthrough in RISC-V hardware for high-end applications to help accelerate the innovations of the global RISC-V industry and promote the improvement and development of the open-source software ecosystem to drive the realization of more innovative top-layer RISC-V applications. VisionFive open-source hardware enables a new level of innovation for the RISC-V ecosystem VisionFive, the first generation of cost-effective RISC-V single-board computer is designed to run Linux, with StarFive’s JH7100 vision processing SoC. The JH7100 SoC is equipped with a 64-bit high-performance RISC-V dual-core processor with a 2MB L2 cache, running at 1.5GHz, which is excellent for high-performance computing. The JH7100 SoC is further equipped with the deep learning processing […]

Imagination introduces Catapult RISC-V CPU cores

As expected, Imagination Technologies is giving another try to the CPU IP market with the Catapult RISC-V CPU cores following their previous unsuccessful attempt with the MIPS architecture, notably the Aptiv family. Catapult RISC-V CPUs are/will be available in four distinct families for dynamic microcontrollers, real-time embedded CPUs, high-performance application CPUs, and functionally safe automotive CPUs. The new 32-/64-bit RISC-V cores will be scalable to up to eight asymmetric coherent cores-per cluster, offer a “plethora of customer configurable options”, and support optional custom accelerators. What you won’t see today are block diagrams and detailed technical information about the cores because apparently, all that information is confidential even though some Catapult RISC-V cores are already shipping “in high-performance Imagination automotive GPUs”. The only way to get more details today is to sign an NDA. Having said that we have some more information about the target markets and development tools. Imagination Capapult […]

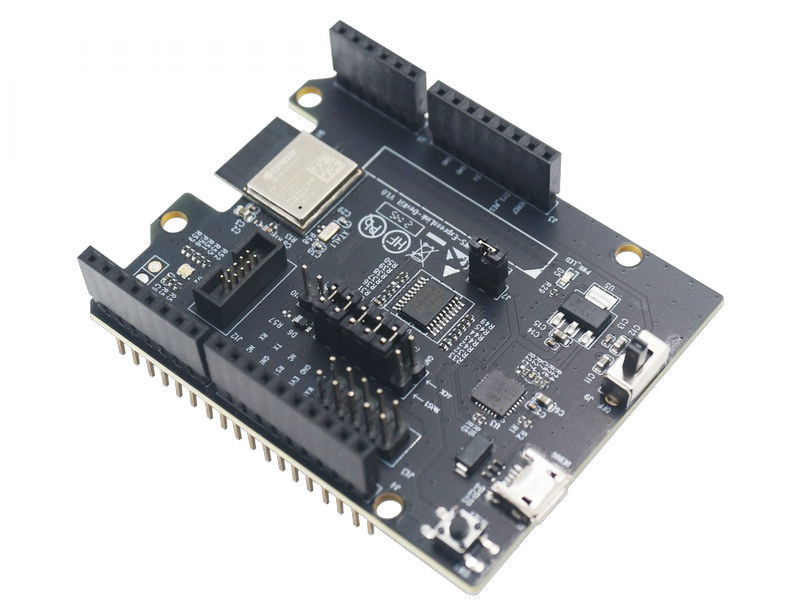

ESP32-C3 AWS IoT ExpressLink module & devkit aim to ease connection to AWS IoT services

Amazon and Espressif have launched another wireless module with the ESP32-C3 AWS IoT ExpressLink module together with a development kit supporting out-of-the-box AWS IoT connectivity, following their earlier collaboration with the launch of the ESP32-PICO-V3-ZERO Alexa Connect Kit Module last summer. Also called the “ESP32-C3-MINI-1-N4-A”, the ESP32-C3 AWS IoT ExpressLink module implements the AWS IoT ExpressLink specification and provides AWS IoT Core connectivity to a host MCU via AT commands over a UART interface. Pre-provisioned and pre-programmed with ease integration the module supports WiFi configuration, messaging, OTA, and device management. The compact (16.6 x 13.2mm) ESP32-C3 module is currently offered as part of the ESP32-C3-AWS-ExpressLink-DevKit development board following the Arduino Zero board form factor allowing it to be plugged into the Arduino board, or easily connect to other host systems such as the Raspberry Pi. The goal is to simplify the deployment of IoT solutions removing the need for […]

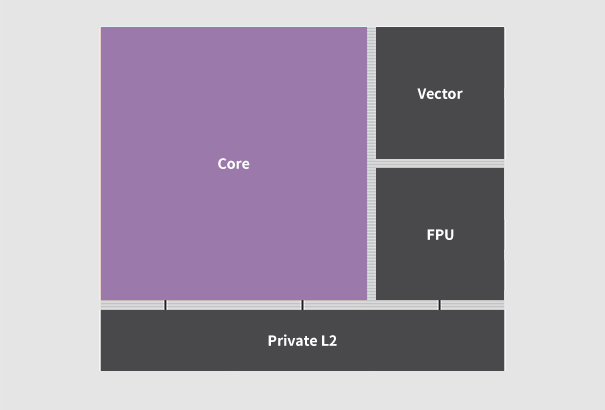

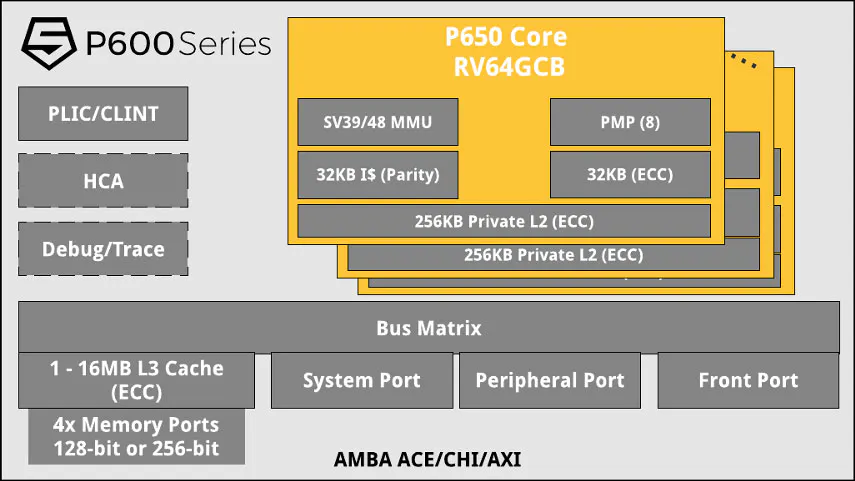

SiFive Performance P650 RISC-V core to outperform Arm Cortex-A77 performance per mm2

About six months have passed since the SiFive announcement of the Performance P550 “fastest 64-bit RISC-V processor” ever, and the company has now introduced an even faster RISC-V core with the Performance P650 that’s expected to match Cortex-A77 performance. Building upon the Performance P550 design, the SiFive Performance P650 is scalable to sixteen cores using a coherent multicore complex, and delivers a 40% performance increase per clock cycle based on SiFive engineering estimated performance in SPECInt2006/GHz, thanks to an expansion of the processor’s instruction-issue width. The company compares P650 to the Arm family by saying it “maintains a significant performance-per-area advantage compared to the Arm Cortex-A77”. SiFive Performance P650 key features: 64-bit RISC-V (RV64GCB) core Sv39/Sv48 Virtual Memory Support Multi-core, multi-cluster processor configurations with up to 16 cores Performance > 11 SpecINT2006/GHz Thirteen stage, four-issue, out-of-order pipeline tuned for scalable performance Private L2 Caches and Streaming Prefetcher for improved memory […]

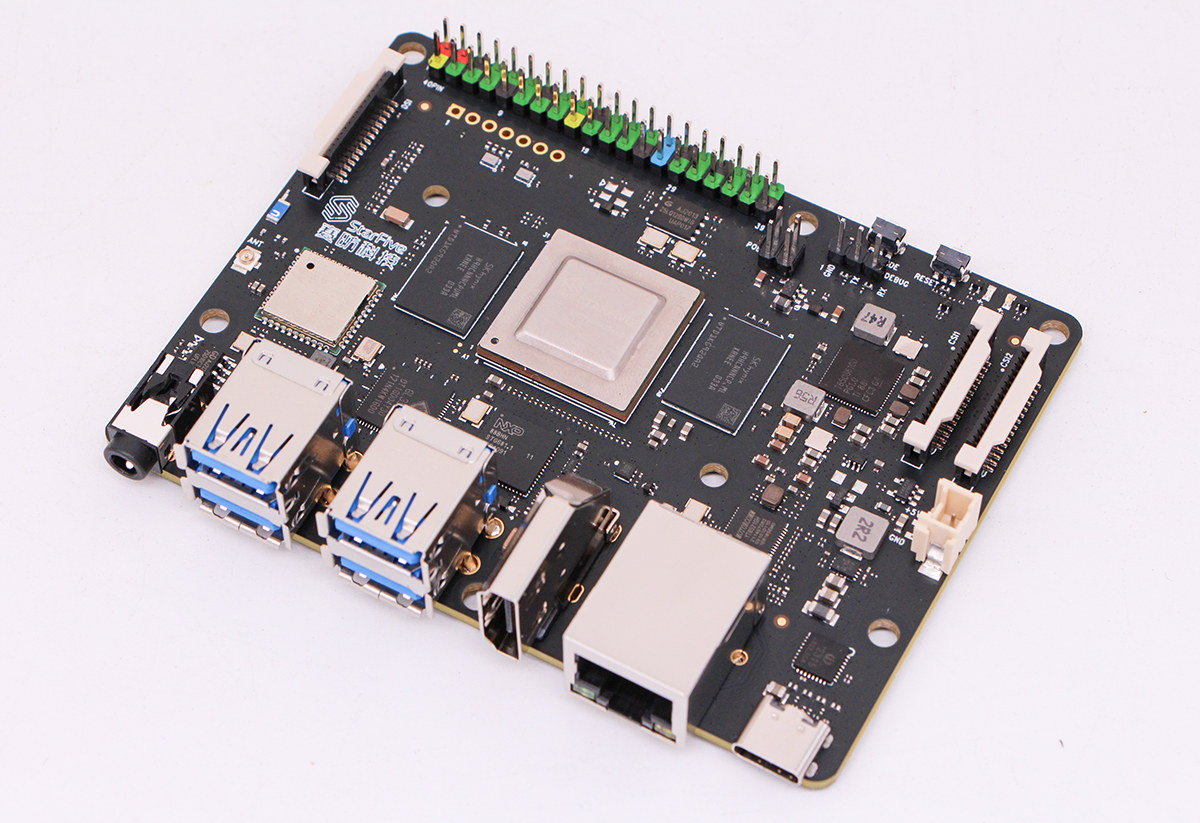

VisionFive V1 RISC-V Linux SBC resurrects BeagleV StarFive single board computer

Last summer we reported that BeagleV StarFive RISC-V SBC would not be manufactured, but all was not lost as StarFive would collaborate with Radxa to make a new single board computer based on their JH7100 dual-core 64-bit RISC-V processor. But thanks to a report on Heise and extra photos acquired by CNX Software, we now have more details about the board that mostly comes with the same features as the BeagleV StarFive, but a completely different layout that brings all the main ports to one side of the board. VisionFive V1 specifications: SoC – StarFive JH7100 Vision SoC with: Dual-core Sifive U74 RISC-V processor @ 1.5 GHz with 2MB L2 cache Vision DSP Tensilica-VP6 for computing vision NVDLA Engine 1 core (configuration 2048 MACs @ 800MHz – 3.5 TOPS) Neural Network Engine (1024MACs @ 500MHz – 1 TOPS) VPU – H.264/H.265 decoder up to 4Kp60, dual-stream decoding up to 4Kp30 […]

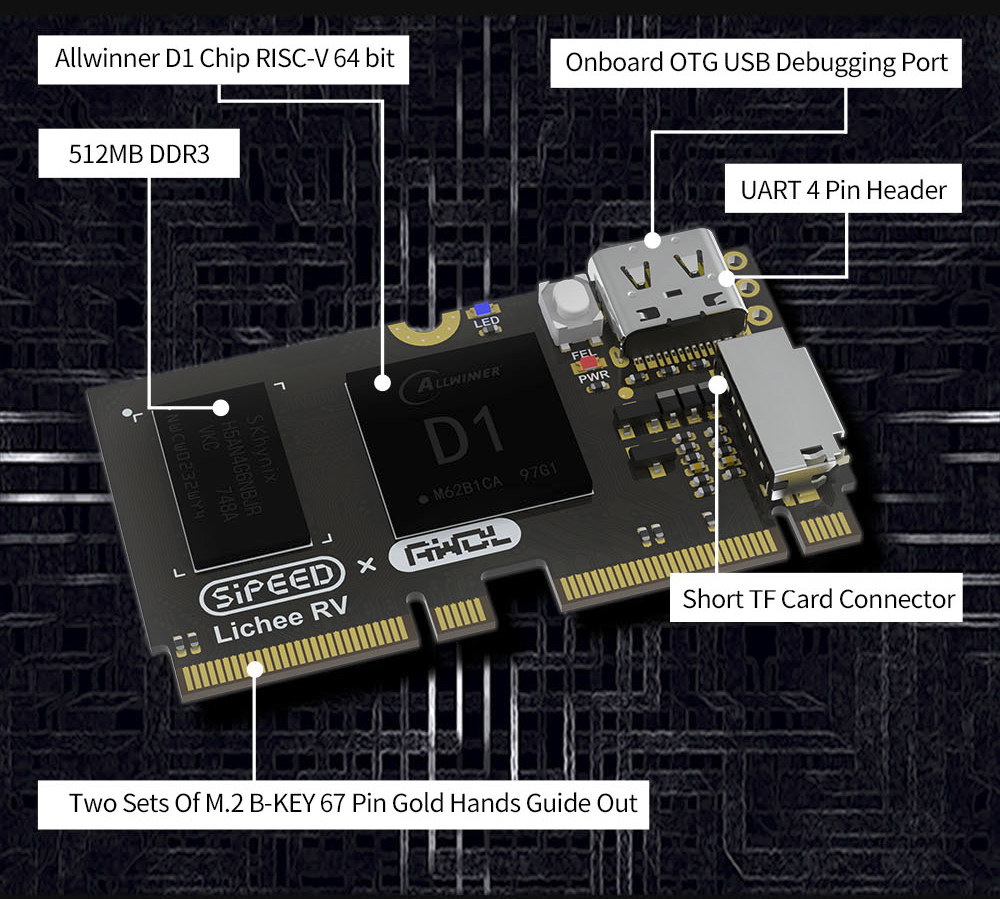

Sipeed LicheeRV – A $16.90 Allwinner D1 Linux RISC-V board

Finally! There’s now a much more affordable Allwinner D1 RISC-V Linux board thanks to Sipeed LicheeRV Nezha CM SBC sold for $16.90 and up on Aliexpress, that’s much cheaper than the $100 asked for Nezha SBC, although still not incredibly cheap as we’ll see from the specifications below. Sipeed LicheeRV is actually both a board and a system-on-on-module with an edge connector, and is equipped with 512MB DDR3, a USB-C OTG port, a MicroSD card socket, and an SPI display interface. The dual M.2 edge connector can be plugged into a carrier board, and they will be a “86 Box” (86x86mm) for HMI display that can be used for home automation. Sipeed Lichee RV specifications: SoC – Allwinner D1 single-core XuanTie C906 64-bit RISC-V processor @ 1.0 GHz with HiFi4 DSP, G2D 2D graphics accelerators Memory – 512MB DDR3 memory @ 792 MHz Storage – MicroSD card slot Video – […]