WiCAN is an ESP32-C3 CAN bus adapter that works over USB, Wi-Fi, and Bluetooth LE, and designed for car hacking and general CAN bus development. The device is available in USB-CAN and OBD-II form factors and comes with firmware that works with RealDash to create nice-looking dashboards with the data. RealDash can be installed on Android, iOS, and Windows 10 operating systems. WiCAN specifications: Wireless module – ESP32-C3-MINI-1 with ESP32-C3 RISC-V microcontroller with 2.4GHz WiFI 4 and Bluetooth 5.0 connectivity, 4 MB flash, PCB antenna CAN 2.0 A/B interface up to 1 Mbps Host interface WiCAN-OBD – OBD-II connector WiCAN-USB – Mini USB port for USB-to-UART up to 6 Mbps Power Supply WiCAN-ODB – 7.5V to 16V (Vbat) WiCAN-USB – 7.5V to 36V via screw-terminal connector Power Consumption – <= 1 mA in battery-saving mode The CAN Bus adapter also supports firmware updates over WiFi, and can be used either […]

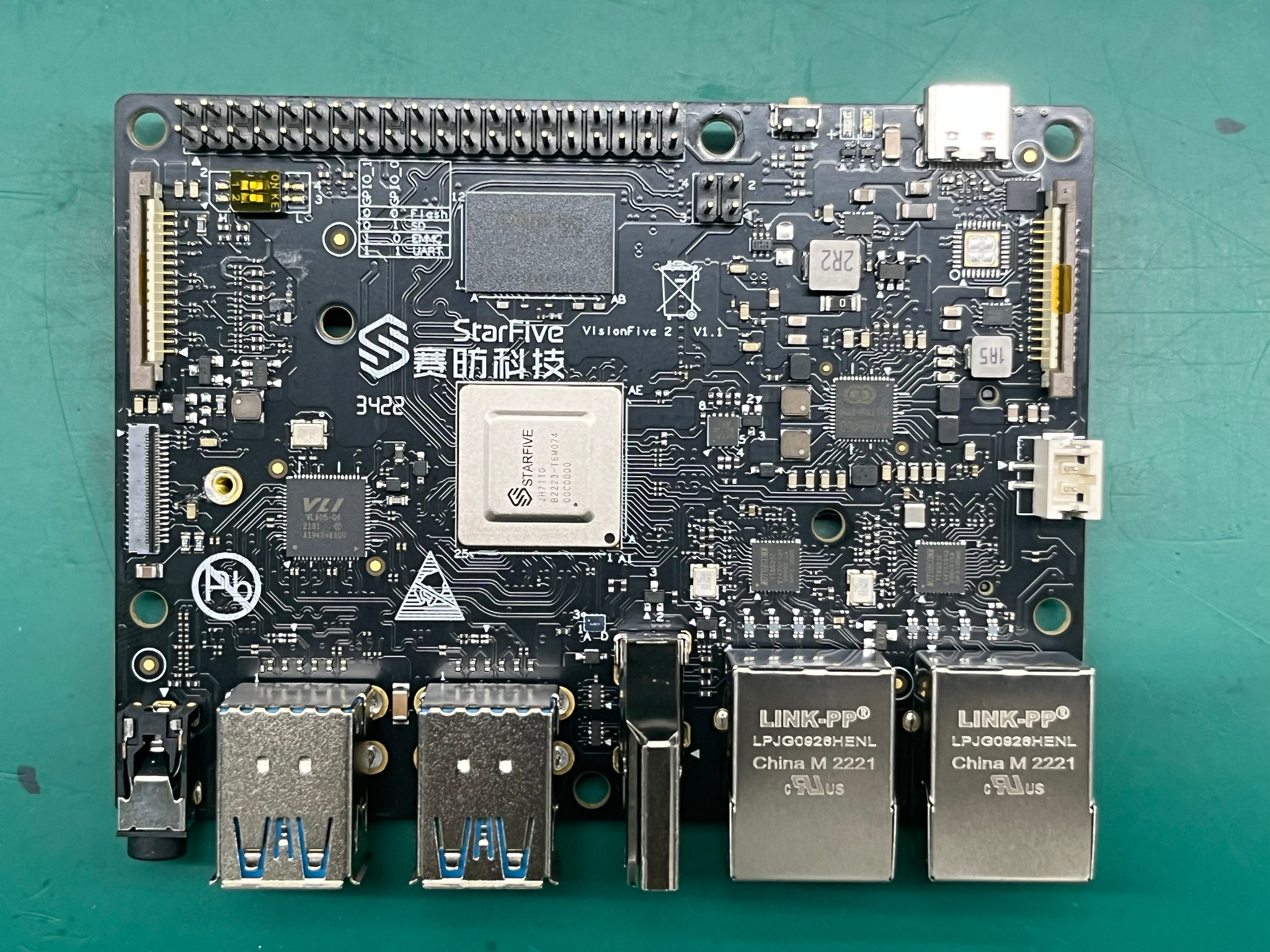

StarFive VisionFive 2 quad-core RISC-V SBC launched for $46 and up (Crowdfunding)

As expected, StarFive has officially unveiled the JH7110 quad-core RISC-V processor with 3D GPU and the VisionFive 2 SBC. I just did not expect the company to also launch a Kickstarter campaign for the board, and the version with 2GB RAM can be had for just about $46 for “early birds”. The VisionFive 2 ships with up to 8GB RAM, HDMI 2.0 and MIPI DSI display interfaces, dual Gigabit Ethernet, four USB 3.0/2.0 ports, a QSPI flash for the bootloader, as well as support for eMMC flash module, M.2 NVMe SSD, and microSD card storage. VisionFive 2 specifications: SoC – StarFive JH7110 quad-core 64-bit RISC-V (SiFive U74 – RV64GC) processor @ up to 1.5 GHz with Imagination BXE-4-32 GPU supporting OpenGL ES 3.2, OpenCL 1.2, Vulkan 1.2 4Kp30 H.265/H.264 video decoder 1080p30 H.265 video encoder System Memory – 2GB, 4GB, or 8GB LPDDR4 Storage – MicroSD card slot, eMMC flash […]

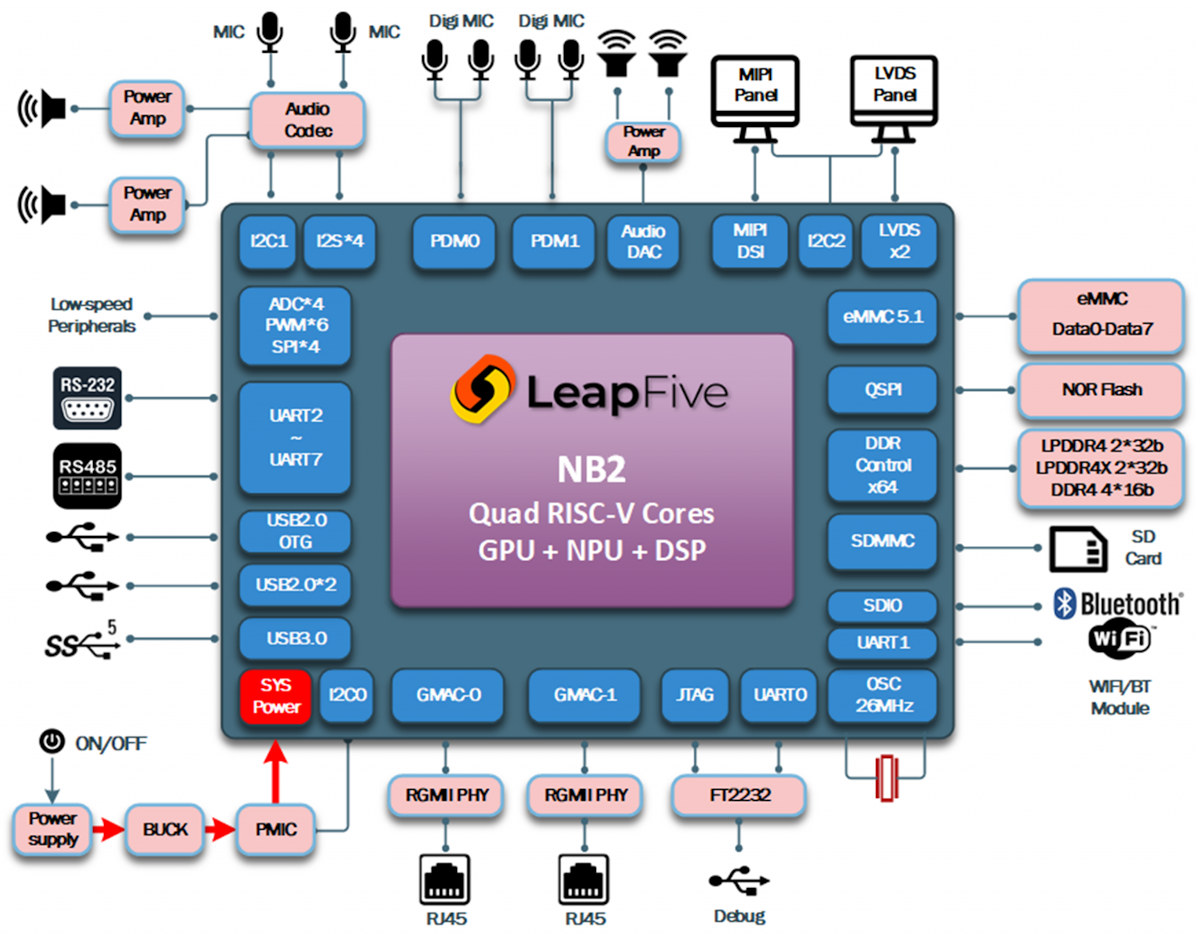

LeapFive NB2 quad-core RISC-V processor comes with GPU, NPU, and DSP

After SiFive and StarFive, here comes LeapFive RISC-V silicon vendor offering the NB2 quad-core 64-bit RISC-V application processor with GPU, NPU, and vision and audio DSPs capable of running Linux. LeapFive NB2 processor is equipped with MIPI DSI and LVDS display interface, dual GbE, USB 3.2/2.0 interfaces, and other peripheral interfaces that make it well-suited to a wide range of applications including Smart Home applications, robotics, industrial gateways, drones, building automation, smart cities, digital signage, medical equipment and more. LeapFive NB2 specifications: CPU – Quad-core SiFive U74 64-bit RISC-V processor @ 1.8 GHz delivering 2.5 DMIPS/MHz Cache – 32KB I-cache, 32KB D-cache, 2MB level 2 cache GPU – “High-performance graphics processor” @ 850 MHz DSP – Dedicated vision DSP, audio DSP NPU – Independent AI engine delivering up to 4 TOPS @ 1.4 GHz VPU – 4Kp60 H.264/H.265 Video encoding and decoding, JPEG image codec System Memory – Up to […]

StarFive VisionFive V1 RISC-V SBC gets Ubuntu 22.04.1 Server image from Canonical

Canonical has been working on RISC-V support for Ubuntu for a while and released Ubuntu 20.04/21.04 64-bit RISC-V images for QEMU and HiFive boards last year. Now the company has released an Ubuntu 22.04.1 Server image for the StarFive VisionFive V1 RISC-V single board computer. While that’s a good development, The VisionFive V1, and other RISC-V platforms, are nowhere close to being Ubuntu-certified hardware, and Canonical posted a note reading “It is an early RISC-V developer access through Ubuntu 22.04.1.” The VisionFive V1 SBC is a pretty good platform for development with a StarFive JH7100 dual-core RISC-V processor, 8GB RAM, Gigabit Ethernet and WiFi connectivity, HDMI output, and four USB 3.0 ports, plus GPIOS headers, and MIPI CSI and DSI connectors. It offers a good middle ground between the high-end (and relatively expensive) HiFive Unmatched mini-ITX motherboard and the low-end Allwinner Nezha single board computer both of which can also […]

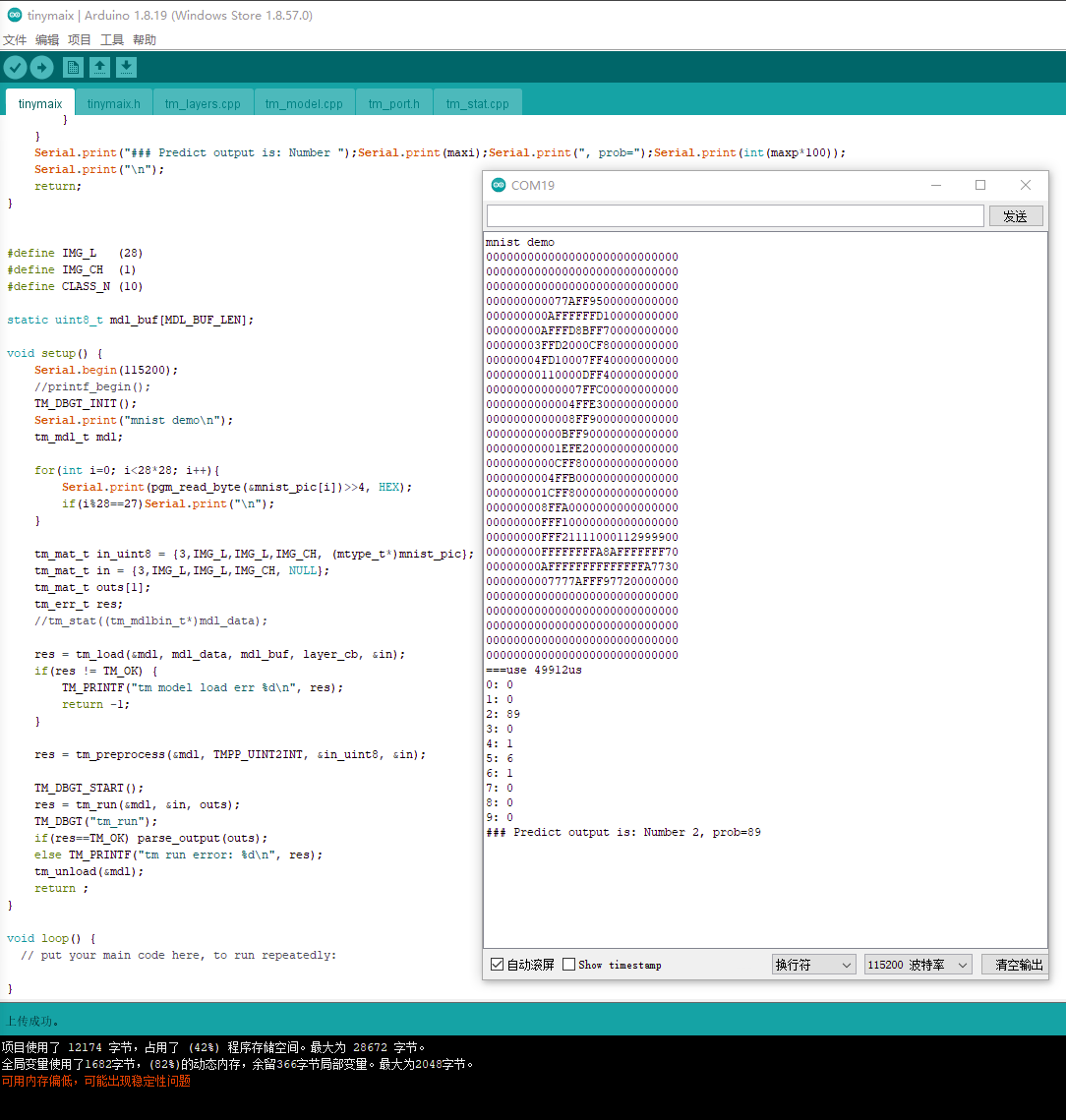

TinyMaix is a lightweight machine learning library for microcontrollers

Sipeed TinyMaix open-source machine learning library is designed for microcontrollers, and lightweight enough to run on a Microchip ATmega328 MCU found in the Arduino UNO board and its many clones. Developed during a weekend hackathon, the core code of TinyMax is about 400 lines long, with a binary size of about 3KB, and low RAM usage, enabling it to run the MNIST handwritten digit classification on an ATmega320 MCU with just 2KB SRAM and 32KB flash. TinyMax highlights Small footprint Core code is less than 400 lines (tm_layers.c+tm_model.c+arch_O0.h), code .text section less than 3KB Low RAM consumption, with the MNIST classification running on less than 1KB RAM Support INT8/FP32 model, convert from keras h5 or tflite. Support multi-architecture acceleration: ARM SIMD/NEON, MVEI, RV32P, RV64V (32-bit & 64-bit RISC-V vector extensions) User-friendly interfaces, just load/run models Supports full static memory config MaixHub Online Model Training support coming soon Sipeed says there […]

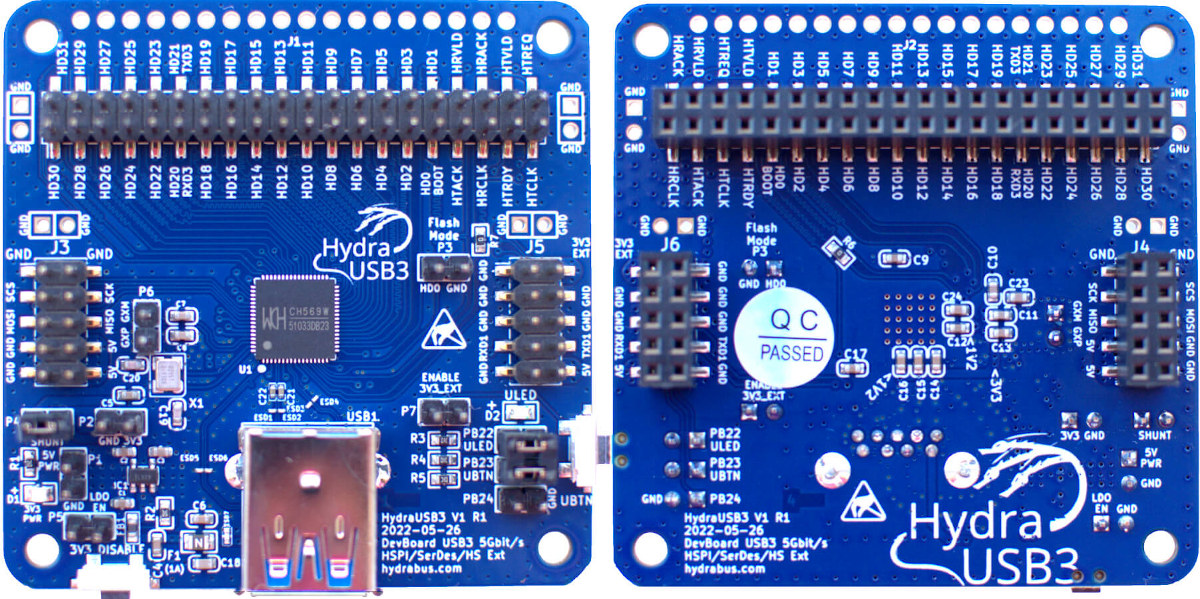

HydraUSB3 RISC-V MCU board combines USB 3.0 with HSPI and SerDes high-speed interfaces

Benjamin VERNOUX has launched the HydraUSB3 V1 board based on WCH CH569 RISC-V MCU as a developer platform to experiment with high-speed protocols like HSPI and SerDes through a USB 3.0 interface. It’s the third board from Benjamin we feature here, after the STM32-based HydraBUS and the HydraNFC v2 shield delivering up to 1600 mW for NFC charging and connectivity. The HydraUSB3 v1 is quite different since it does not involve NFC at all, and instead leverages the CH569’s high-speed interfaces including USB 3.0 (5 Gbps), HSPI (3.8Gbps), and SerDes (>1.2Gbps). HydraUSB3 V1 specifications: MCU – WCH CH569 32-bit RISC-V (RISC-V3A) RV32IMAC MCU @ 120MHz with 16KB 32-bit SRAM, 96KB configurable 128-bit SRAM, 448KB code flash, 32KB data flash USB – 1x USB 3.0 host/device port that supports the USB 3.0 SS built-in PHY (5Gbps) and USB 2.0 built-in PHY FS/LS/HS (480Mbps) High-speed I/Os High-Speed Parallel Interface (HSPI) up to […]

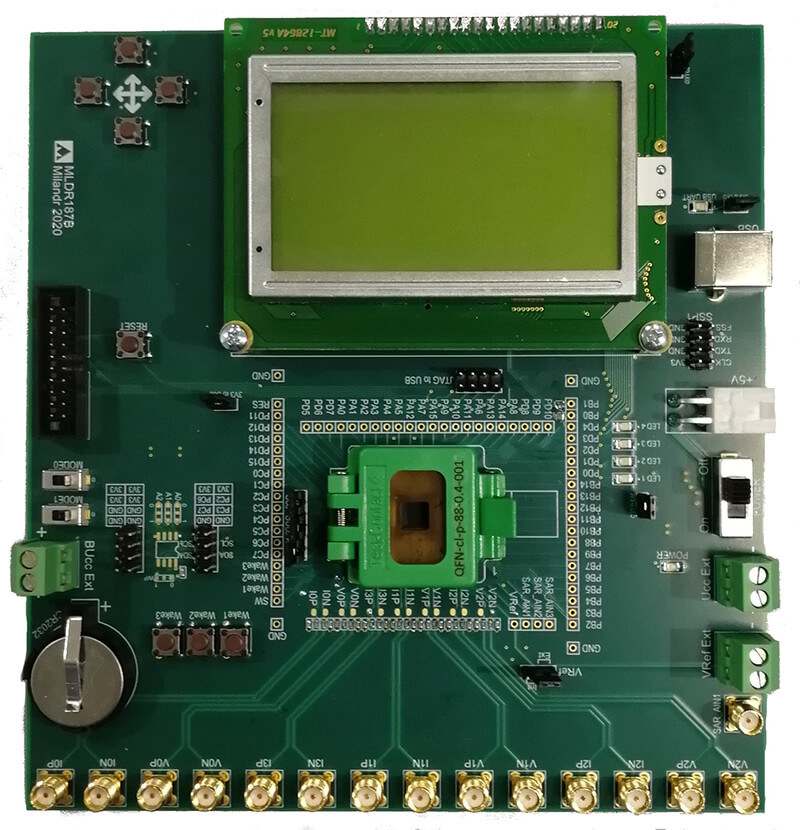

Milandr MDR32F02FI is a RISC-V microcontroller for (Russian) electricity meters

Last year, we wrote about the Made-in-Russia Mikron MIK32 RISC-V microcontroller with features similar to STM32L0 Arm Cortex-M0+, and I was recently told that the first fully packed samples are expected for the end of autumn. But it turns out there’s another Russian company that makes RISC-V microcontrollers, and for instance, the Milandr MDR32F02FI features the open-source BM-310 RISC-V MCU core and is specially designed for electricity meters. It is the second generation of the microcontroller with the first being based on Arm Cortex-M0 core and produced for over 5 years. Milandr MDR32F02FI specifications: CPU – CloudBEAR BМ-310S 32-bit RISC-V core @ 60 MHz Memory – 112KB Storage – 256+8 KB flash, 16KB OTP Electricity meter function 7-channel 24-bit sigma-delta ADC Hardware unit for calculating power consumption Other Peripherals 5x UART, 3x SPI, 1x I2C Up to 55x GPIOs Instrumental ADC – 10-bit with temperature sensor 4x 32-bit timer blocks […]

Linux 5.19 Release – Main changes, Arm, RISC-V and MIPS architectures

Linus Torvalds has just announced the release of Linux 5.19. It should be the last 5.xx version, with Linux 6.0 coming for the next cycle: So here we are, one week late, and 5.19 is tagged and pushed out. The full shortlog (just from rc8, obviously not all of 5.19) is below, but I can happily report that there is nothing really interesting in there. A lot of random small stuff. In the diffstat, the loongarch updates stand out, as does another batch of the networking sysctl READ_ONCE() annotations to make some of the data race checker code happy. Other than that it’s really just a mixed bag of various odds and ends. On a personal note, the most interesting part here is that I did the release (and am writing this) on an arm64 laptop. It’s something I’ve been waiting for for a _loong_ time, and it’s finally reality, […]