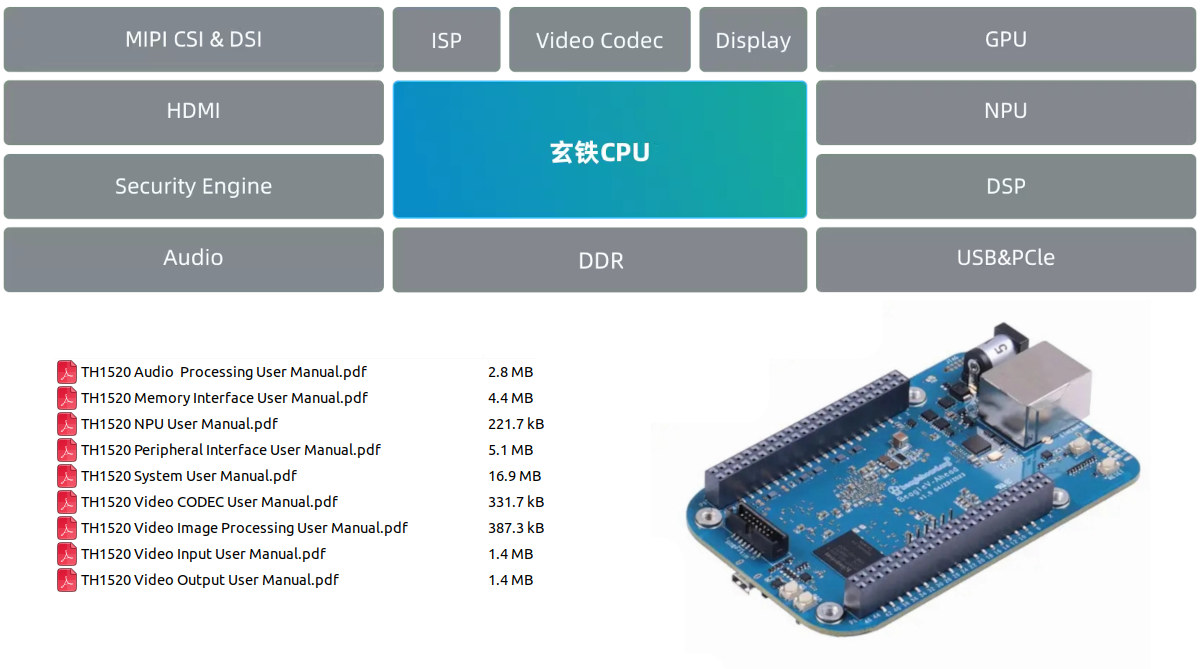

Further Alibaba T-Head TH1520 quad-core RISC-V processor documentation has been released with nine user manuals covering video and audio processing, peripheral interfaces, memory interfaces, system registers, and the built-in NPU for video acceleration. We first noted the TH1520 RISC-V SoC in the expensive web3-focused ROMA laptop in October 2022, but since then there have been some very interesting developments with the release of Sipeed’s Lichee Pi 4A SBC and various other platforms based on the LM4A system-on-module plus the BeagleBoard.org’s BeagleV Ahead. Both boards also have preliminary support in mainline Linux with the Lichee Pi 4A making it to Linux 6.5, and the BeagleV Ahead was added to the just-released Linux 6.6 kernel. However I had not noticed documentation for the processor was not released publicly until now as both Sipeed and Beagleboard.org have now made available nine user manuals in English, and the Sipeed link has the Chinese versions […]

Linux 6.6 LTS release – Highlights, Arm, RISC-V and MIPS architectures

The Linux 6.6 release has just been announced by Linus Torvalds on the Linux Kernel Mailing List (LKML): So this last week has been pretty calm, and I have absolutely no excuses to delay the v6.6 release any more, so here it is. There’s a random smattering of fixes all over, and apart from some bigger fixes to the r8152 driver, it’s all fairly small. Below is the shortlog for last week for anybody who really wants to get a flavor of the details. It’s short enough to scroll through. This obviously means that the merge window for 6.7 opens tomorrow, and I appreciate how many early pull requests I have lined up, with 40+ ready to go. That will make it a bit easier for me to deal with it, since I’ll be on the road for the first week of the merge window. Linus About two months ago, […]

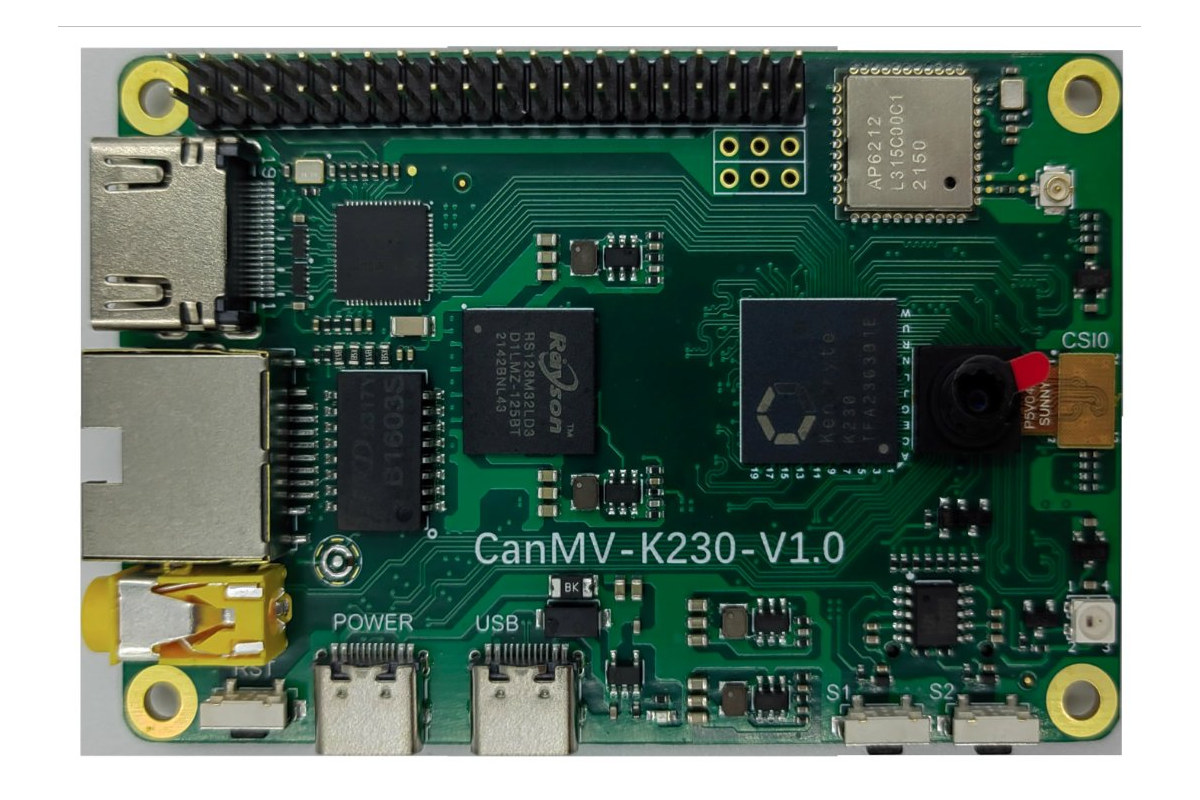

CanMV-K230 AI development board features Kendryte K230 dual-core 64-bit RISC-V processor

CanMV-K230 is a credit card-sized development board for AI and computer vision applications based on the Kendryte K230 dual-core C908 64-bit RISC-V processor with built-in KPU (Knowledge Process Unit) and various interfaces such as MIPI CSI inputs and Ethernet. The first Kendryte RISC-V AI processor was launched in 2018 with the K210 which I tested with the Grove AI HAT and Maixduino board and found fun to experiment with, but noted that performance was limited. Since then the company introduced the K510 mid-range AI processor with a more powerful 3 TOPS AI accelerator, and the K230 entry-level successor to the K210 – which was planned for 2022 in a 2021 roadmap – has now just been launched and integrated into the CanMV-K230 development board. CanMV-K230 specifications: SoC – Kendryte K230 CPU 64-bit RISC-V processor @ 1.6GHz with RISC-V Vector Extension 1.0, FPU 64-bit RISC-V processor @ 800MHz with support for […]

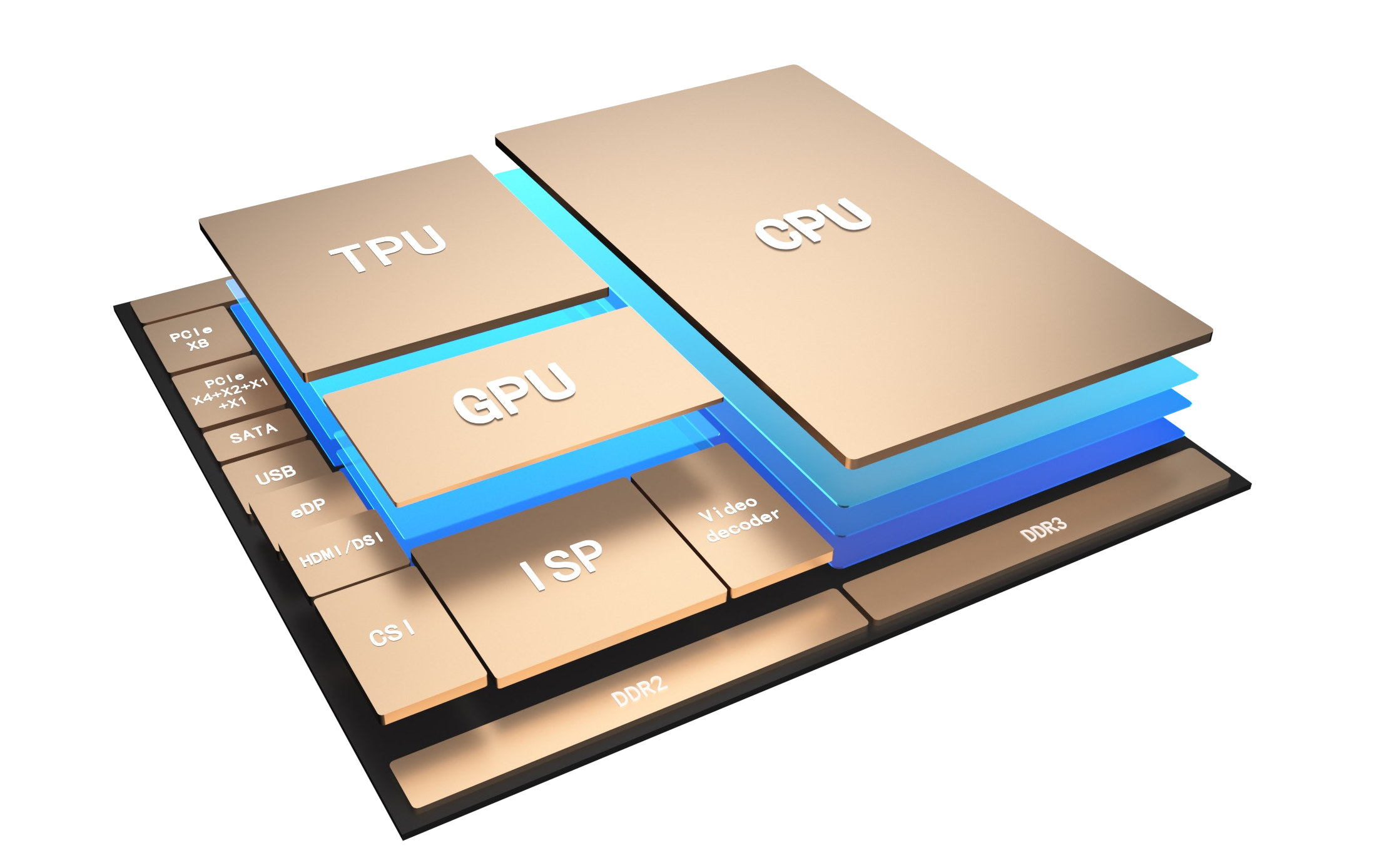

Sophgo SG2380 – A 2.5 GHz 16-core SiFive P670 RISC-V processor with a 20 TOPS AI accelerator

Sophgo SG2380 is an upcoming 2.5 GHz 16-core RISC-V processor based on SiFive Performance P670 cores and also equipped with a 20 TOPS AI accelerator using SiFive Intelligence X280 and Sophgo TPU that will find its way into a $120 desktop-class mini-ITX motherboard in H2 2024. The RISC-V processor also supports up to 64GB RAM, as well as UFS 3.2 and SATA 3.0 storage, comes with an Imagination GPU for 3D graphics and a VPU capable of 4Kp60 H.265, H.264, AV1, and VP9 video decoding, plenty of interfaces, and the system can manage locally deployed larger-scale LLMs like LLaMA-65B without the need for external NVIDIA or AMD accelerator cards. Sophgo SG2380 RISC-V SoC Sophgo SG2380 specifications: CPU 16-core SiFive P670 (RV64GCVH) 64-bit RISC-V processor @ up to 2.5GHz with RISC-V Vector v1.0, Vector Crypto Cluster configuration – 12x 2.5 GHz performance cores, 4x 1.6 GHz efficiency cores Full RISC-V RVA22 […]

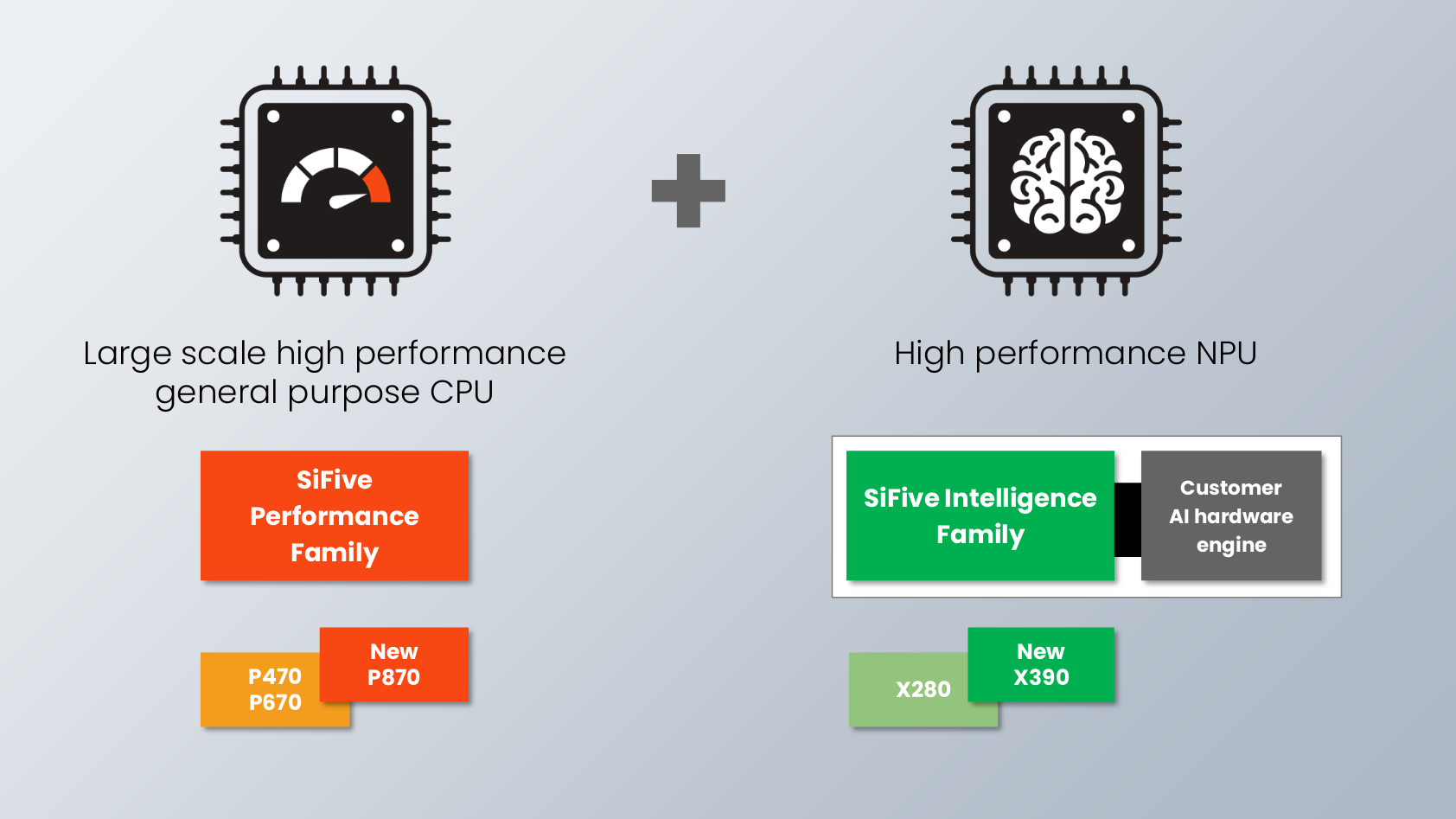

SiFive announces Intelligence X390 NPU, Performance P870 RISC-V core

SiFive has announced two new high-performance IP blocks with the Intelligence X390 NPU and the Performance P870 RISC-V core that should find their way into SoC designed for Generative AI and ML applications. We had already covered the Performance P870 and its automotive sibling – the P870-A – from information in an earlier presentation, but the SiFive Intelligence X390 NPU is new to me and appears to be aimed at generative AI in data centers, although we will very soon be seeing companies implement generative AI at the edge in pretty powerful embedded devices. SiFive Performance P870 highlights: Full support for the RVA23 RISC-V profile specification and Vector 1.0 and Vector Crypto Six-wide, out-of-order 64-bit core Up to a 32-core cluster >12 SpecINT2k6/GHz, or a 50% peak single thread performance upgrade over the previous generation SiFive Performance P670 SiFive Features 2x 128b VLEN RVV Vector crypto and hypervisor extensions IOMMU […]

OpenWrt 23.05 released with MbedTLS by default, Rust packages, over 1,790 supported devices

OpenWrt 23.05 open-source Linux operating system for routers and resource-constrained headless embedded systems has just been released with over 4300 commits since the release of OpenWrt 22.03 a little over a year ago. The new release now supports over 1790 devices or about over 200 new devices compared to the OpenWrt 22.03 release with notable new targets including the ipq807x target for the Qualcomm IPQ807x WiFi 6 SoCs, the mediatek/filogic subtarget for the Mediatek Filogic 830 and 630 SoCs, and the sifiveu target for the HiFive Unleashed and Unmatched RISC-V development boards. OpenWrt 23.05 switches from wolfSSL to MbedTLS as default because the latter has a much smaller footprint and offers a more stable ABI (application binary interface) and LTS releases, but it does lack support for TLS 1.3, so users who need the latter may still switch to wolfSSL if needed. Another highlight of the new OpenWrt release is […]

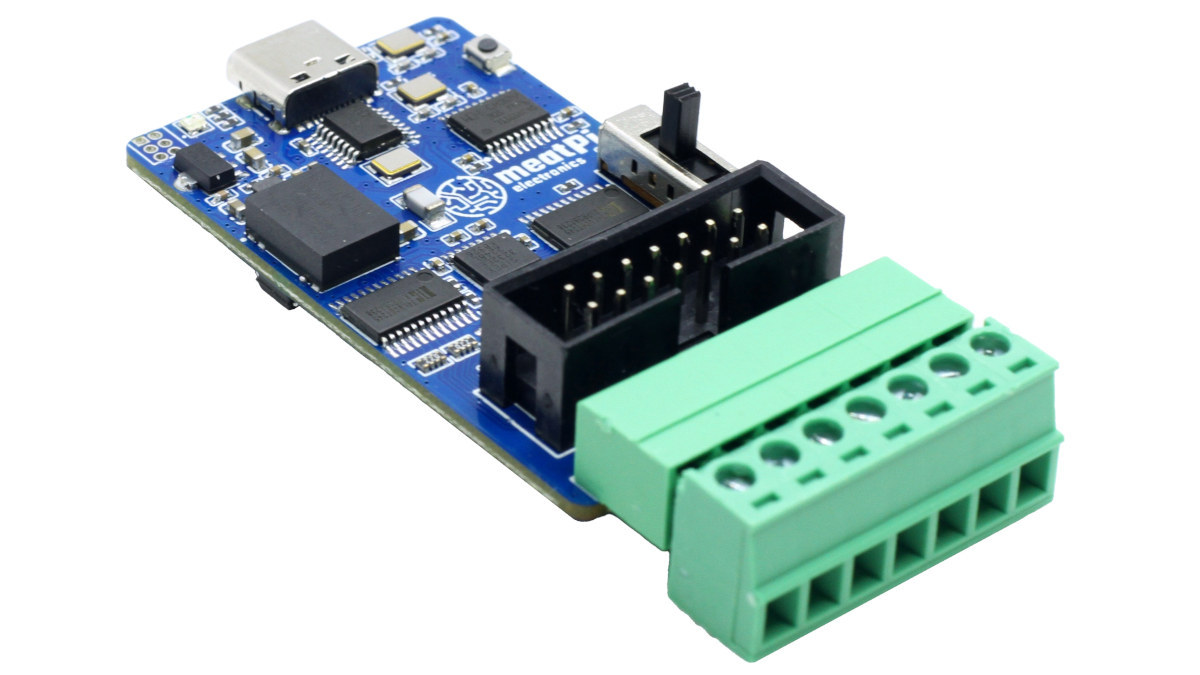

Ollie v2 USB to UART/CAN/RS485/RS232 converter gets USB-C port, plastic enclosure, and more (Crowdfunding)

Ollie v2 is an improved version of the Ollie USB to isolated UART, CAN Bus, RS232, and RS485 converter that gains a USB-C port, a plastic case, the ability to set the voltage from the target board, and various other minor improvements. Like the first version, the Ollie v2 is a portable tool designed for hackers and field engineers that allows them to work with a single device instead of a bunch of USB converters, each handling a single protocol, and isolation makes sure the host, such as a laptop, is protected from high voltages. Ollie V2 specifications: Serial chip – WCH CH344 quad-serial port chip (instead of XR21V1414 in the first design) Host interface – USB Type-C port Isolated interfaces (all with ESD protection) 2x UART ports up to 6 Mbps with 1.8/3.3/5 V or target voltage levels (set by slide switch) CAN 2.0A/B up to 1 Mbps bus […]

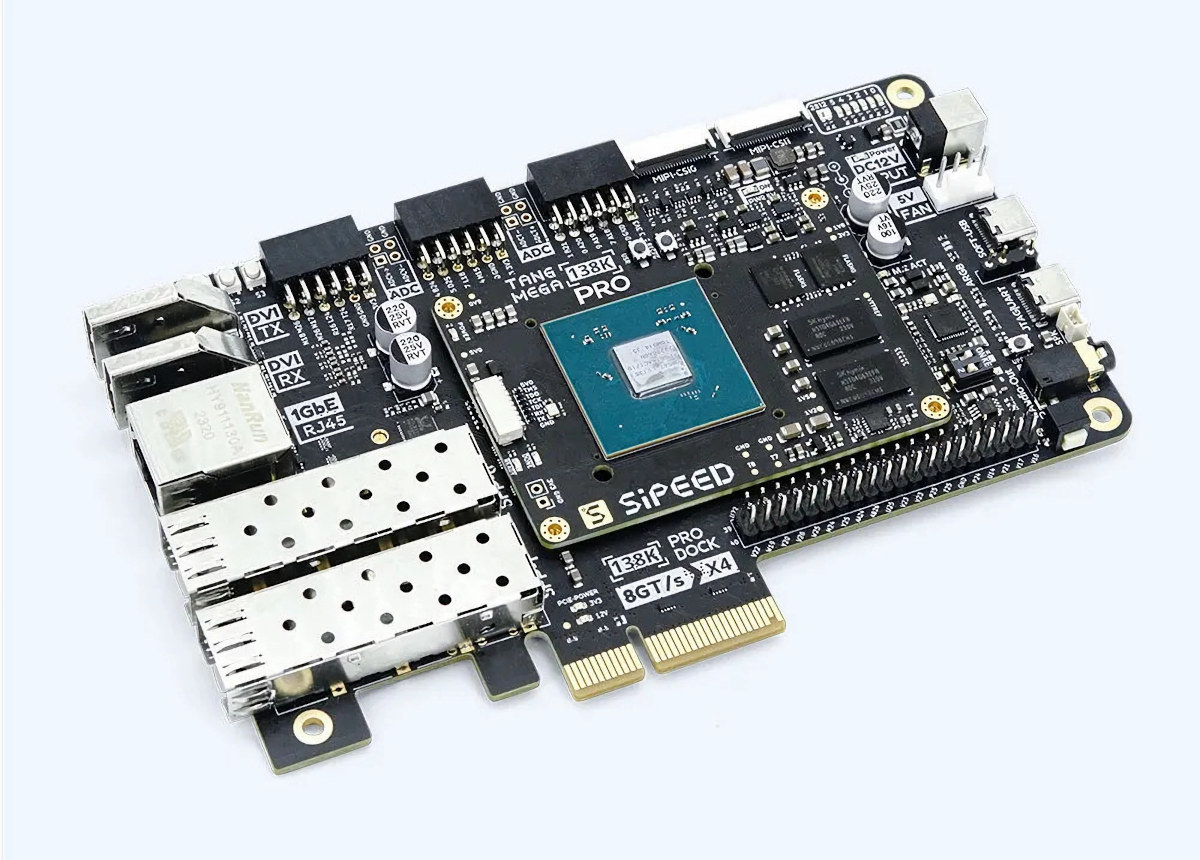

Sipeed Tang Mega 138K Pro Dock features GOWIN GW5AST FPGA + RISC-V SoC

Sipeed has launched another FPGA board part of their Tang family with the Tang Mega 138K Pro Dock powered by a GOWIN GW5AST SoC with 138K logic elements as well as an 800 MHz AE350_SOC RISC-V hardcore unit, and featuring a PCIe 3.0 x4 interface, DVI Rx and Tx, two SFP+ cages, a Gigabit Ethernet RJ45 port, and more. We’ve previously seen companies like AMD (Xilinx) and Microchip produce FPGA SoCs with hard cores such as the Zynq Ultrascale+ family (4x Cortex-A53) or the PolarFire MPSoC (4x 64-bit SiFive U54 RISC-V cores), but it’s the first time I see GOWIN introduce an FPGA + RISC-V SoC, as all the previous parts that came to my attention were FPGA devices. Sipeed Tang Mega 138K Pro Dock specifications: System-on-Module – Sipeed Tang Mega 138K Pro SoC FPGA – GOWIN GW5AST-LV138FPG676A with 138,240 LUT4 1,080 Kb Shadow SRAM (SSRAM) 6,120 Kb Block SRAM […]