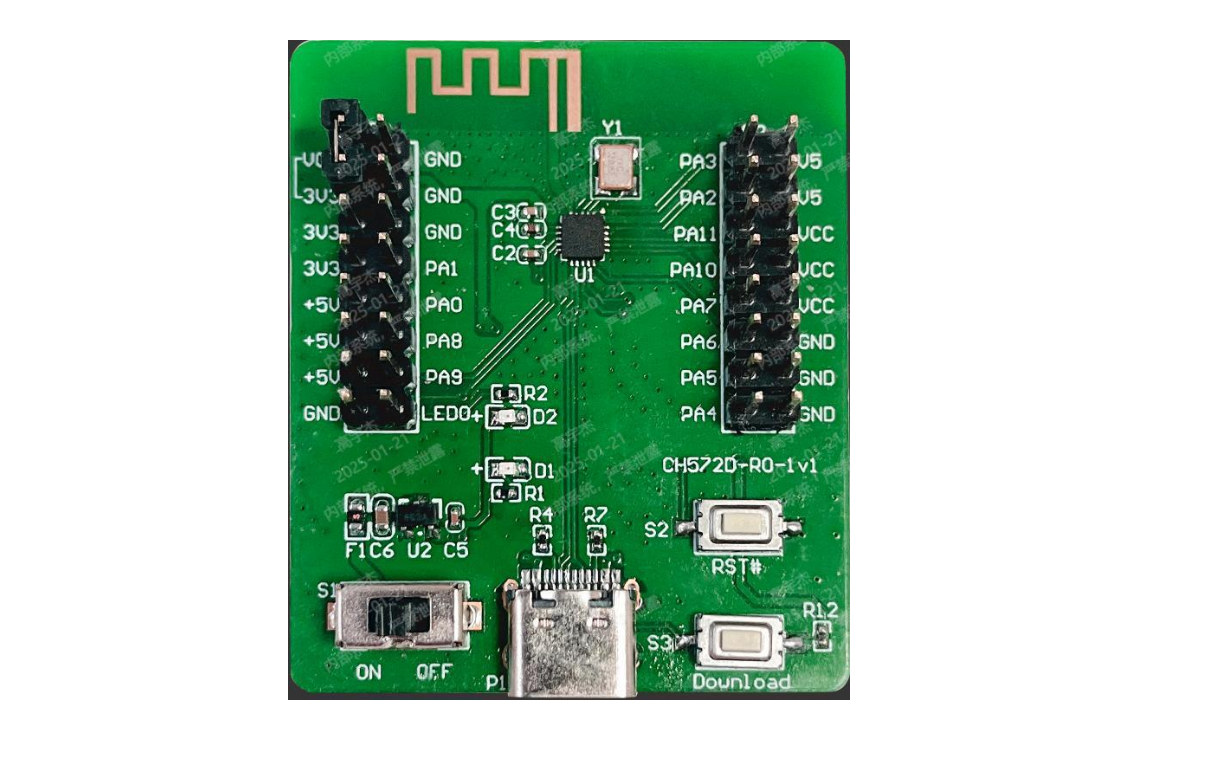

Patrick Yang, CTO at WCH, has recently unveiled the CH570 RISC-V SoC with 2.4GHz wireless and USB 2.0 (host & device) as an upgrade to the popular CH32V003 general-purpose RISC-V MCU with more features at the same low price (10 cents). CH570 also comes with 12KB SRAM and 256KB flash (vs 2KB SRAM and 16KB flash for the CH32V003), offers up to twelve GPIO, six PWM, I2C, UART, SPI, and a 20-channel key detection module. There’s also the CH572 with the same features, except it also supports Bluetooth LE 5.0. As a side note, I wrote about the CH572 RISC-V MCU with BLE in 2019, but I guess it was scrapped likely because it had OTP instead of flash…, and the new CH572 (2025) is different. WCH CH570/CH572 specifications: CPU core QingKe 32-bit RISC-V3C core @ up to 100 MHz (RV32IMBC instruction set and custom instructions) Low-power 3-stage pipeline High-speed […]

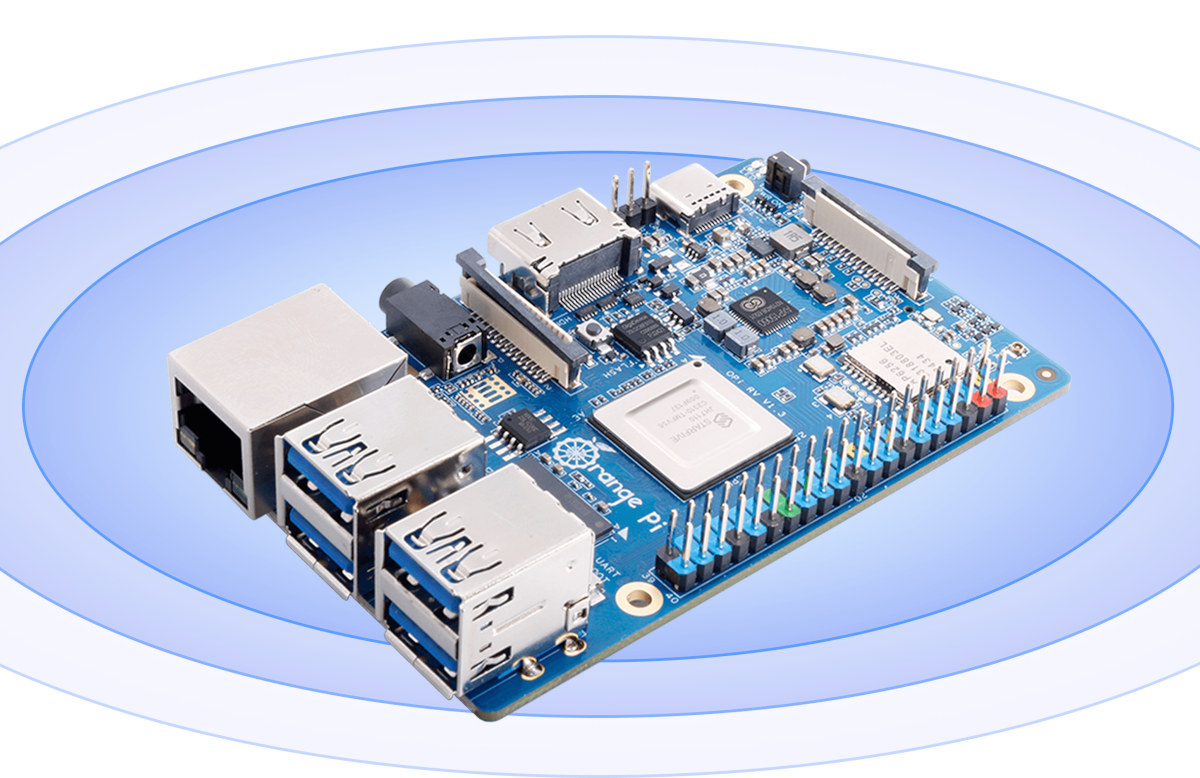

Orange Pi RV RISC-V SBC with StarFive JH7110 SoC launched for $30 and up

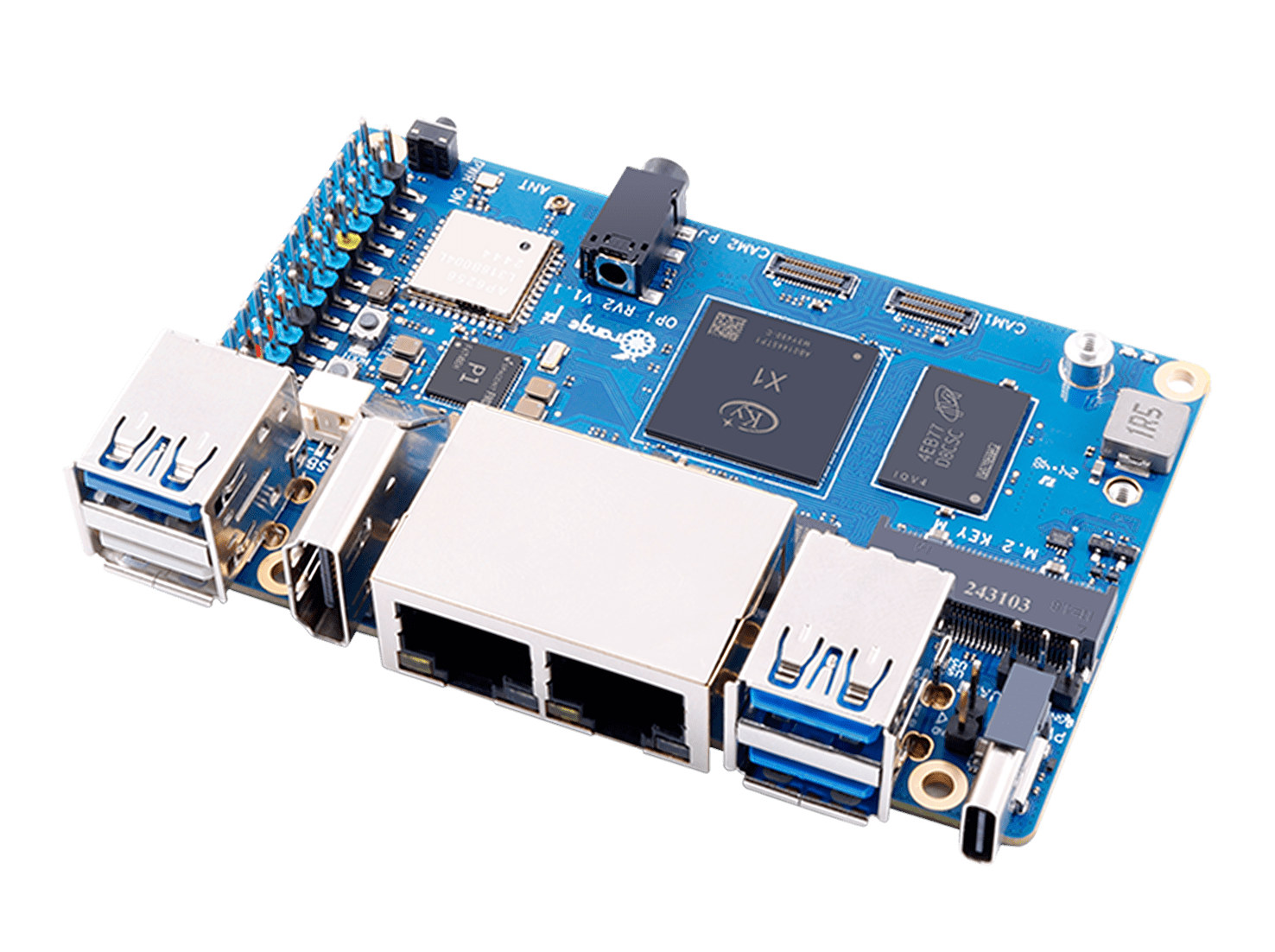

The Orange Pi RV SBC powered by a StarFive JH7110 RISC-V SoC was first introduced at the Orange Pi Development Conference 2024, a little over one year ago. But somehow, the company first launched the Orange Pi RV2 SBC based on Ky X1 SoC (rebranded Spacemit K1) earlier this month, and has only started taking orders for the Orange Pi RV board. The credit card-sized SBC ships with 2GB to 8GB RAM, supports M.2 NVMe SSD storage, provides gigabit Ethernet, built-in WiFi 5 and Bluetooth 5.0, four USB 3.0 ports, HDMI and MIPI DSI video interface, a MIPI CSI camera interface, a 40-pin GPIO header, and more. Orange Pi RV specifications: SoC – StarFive JH7110 CPU – Quad-core RISC-V processor (RV64GC) at 1.5 GHz GPU – Imagination BXE-4-32 GPU with support for OpenCL 1.2, OpenGL ES 3.2, Vulkan 1.2 VPU H.264 & H.265 4Kp60 decoding H.265 1080p30 encoding JPEG encoder / […]

Linux 6.14 release – Main changes, Arm, RISC-V, and MIPS architecture

Linus Torvalds has just announced the release of Linux 6.14 on LKML: So it’s early Monday morning (well – early for me, I’m not really a morning person), and I’d love to have some good excuse for why I didn’t do the 6.14 release yesterday on my regular Sunday afternoon release schedule. I’d like to say that some important last-minute thing came up and delayed things. But no. It’s just pure incompetence. Because absolutely nothing last-minute happened yesterday, and I was just clearing up some unrelated things in order to be ready for the merge window. And in the process just entirely forgot to actually ever cut the release. D’oh. So yes, a little delayed for no good reason at all, and obviously that means that the merge window has opened. No rest for the wicked (or the incompetent). Below is the shortlog for the last week. It’s nice and […]

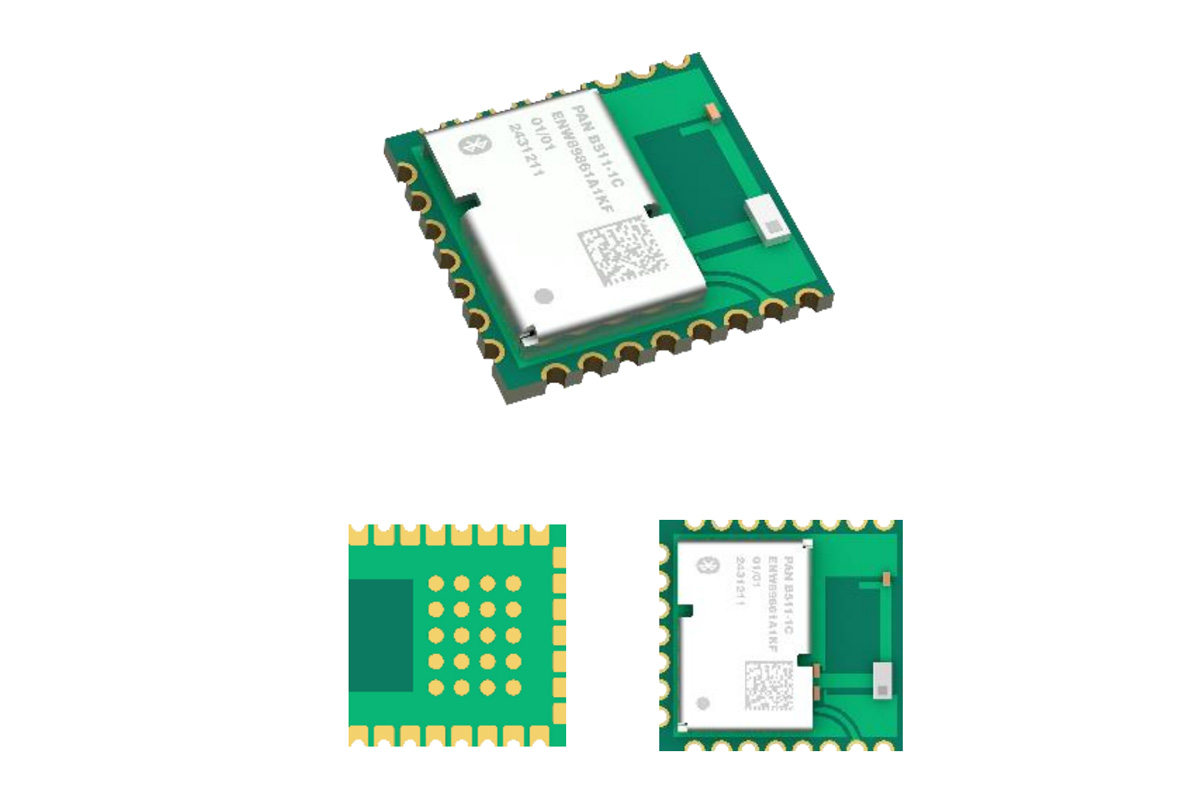

Panasonic PAN B511-1C Bluetooth 6.0 and 802.15.4 module features castellated holes and LGA footprint

Panasonic industry has recently introduced the PAN B511-1C Bluetooth 6.0 and 802.15.4 module based on the Nordic Semi nRF54L15 SoC and designed for ultra-low-power wireless communication. The compact module integrates a chip antenna, 32MBit flash memory, two Crystals, and the Nordic nRF54L51 which provides a 128 MHz Arm Cortex-M33 microcontroller with Bluetooth 6.0 (LE), Thread, Zigbee, and Matter, along with multiple peripherals such as SPI, UART, I2S, PWM, and ADC. The PAN B511-1C also implements security features to support secure boot, secure firmware updates, cryptographic acceleration, and tamper detection, making it suitable for a range of IoT, industrial automation, smart home, medical (wearables), and battery-powered applications. PAN B511-1C module specification: SoC – Nordic Semiconductor nRF54L15 MCU cores Arm Cortex-M33 with Arm TrustZone @ 128MHz RISC-V coprocessor for software-defined peripheral Memory – 256KB SRAM Storage – 1.5MB non-volatile memory Wireless Bluetooth 6.0 Data rates – 2Mbps, 1Mbps, 500kbps, 125kbps Features AoA / […]

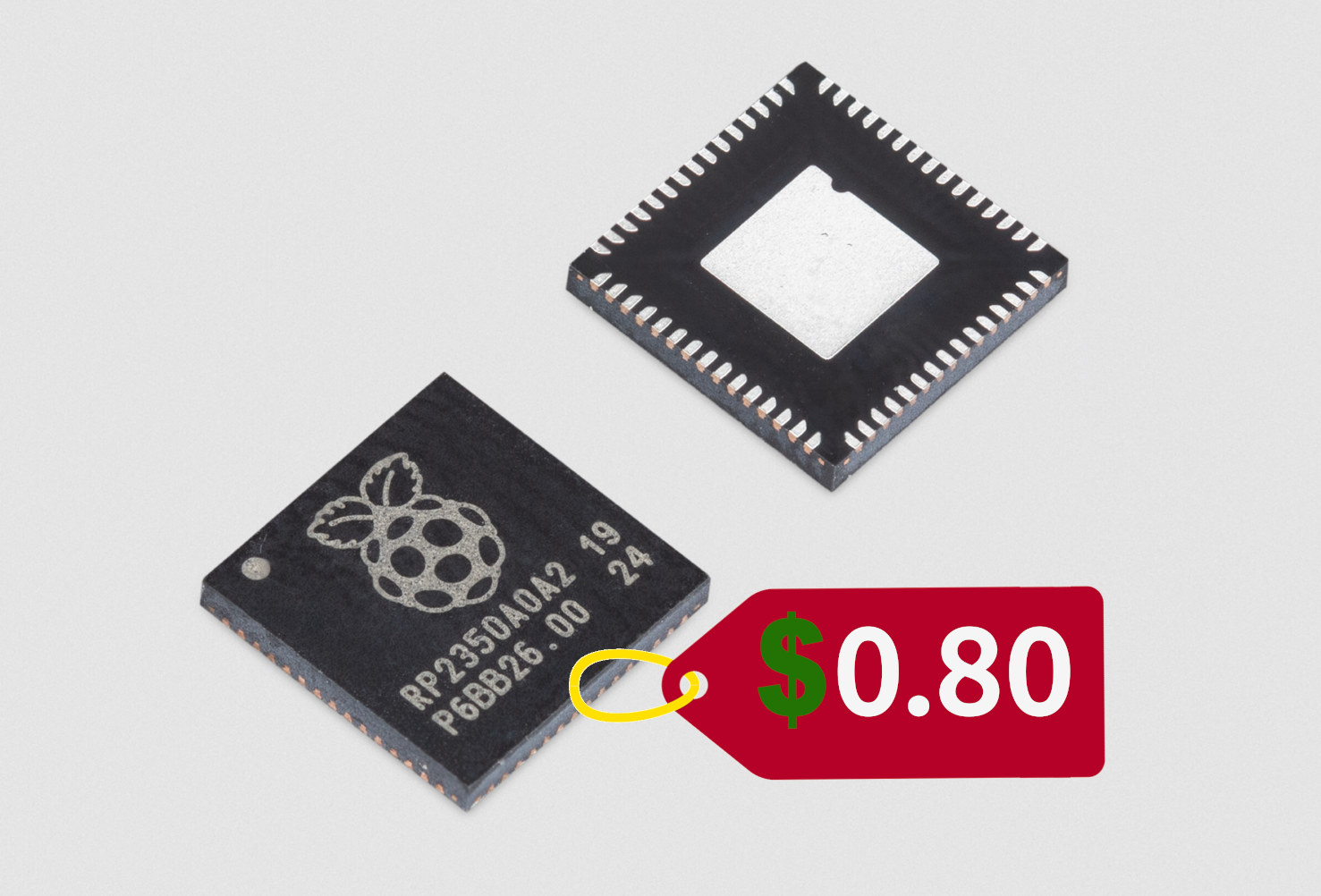

You can now buy Raspberry Pi RP2350 MCU for 80 cents and up, RP2354A and RP2354B variants coming soon

The Raspberry Pi RP2350 dual-core Cortex-M33/RISC-V MCU was first unveiled along with the Raspberry Pi Pico 2 in August 2024. Since then we have covered many Raspberry Pi RP2350 news and boards, but the microcontroller was hard to source for hobbyist and low-volume projects, which partially explains why companies like NextPCB had promotions offering free PCBA prototyping services for RP2350 designs. The good news is that Raspberry Pi has just announced general availability for the RP2350 microcontrollers starting at $0.80 per unit for the RP2350A in 3,400-piece reels, or $1.1 in single quantity, so anybody can buy the MCUs from their favorite distributor. The British company also announced the RP2354A and RP2354B variants with 2MB of stacked flash memory would soon be available to select partners and mass production will ramp up later this year. Here’s the current official pricing information for the RP2040 and RP2350 microcontrollers. Users can simply […]

Updated PineTab-V RISC-V tablet ships with Debian 12-based Linux image

Pine64 has launched an updated version of the PineTab-V RISC-V tablet with the same StarFive JH7110 SoC, 8GB RAM, and 128GB eMMC flash, but a few small hardware changes, and a Debian-based Linux image maintained by StarFive themselves. The PineTab-V is not exactly a new RISC-V tablet since it was launched in 2023, but at the time it was reserved for developers since it shipped with nothing… Users had to install the OS (that did not support the display yet) themselves, and work on the software/OS to improve it. The new model still targets developers and enthusiasts/early adopters, but at least now there’s a Debian 12 image optimized for the PineTab-V. The hardware is mostly the same, except Pine64 added an accelerometer, a status LED, an ID for the PineTab-V in the EEPROM, and a fix for slow charging while the tablet is turned off. PineTab-V (2025) specifications: SoC – […]

Orange Pi RV2 – A $30+ RISC-V SBC powered by Ky X1 octa-core SoC with a 2 TOPS AI accelerator

While the Orange Pi RV RISC-V SBC introduced at the Orange Pi Developer Conference 2024 last year is yet to be launched (should be up in a few days), the company has just launched the Orange Pi RV2 powered by the Ky X1 octa-core RISC-V SoC with a 2 TOPS AI accelerator, up to 8GB LPDD4X, optional eMMC flash moduyle, two M.2 sockets for storeage, dual gigabit Ethernet, WiFi 5, and more. While RISC-V has made a lot of progress over the years, Linux RISC-V SBCs were often synonymous with relatively expensive hardware for developers, since software is often unsuitable for production, at least for applications using graphics. The Orange Pi RV2 addresses the cost issue since the octa-core RISC-V SBC sells for just $30 to $49.90 depending on the configuration. Orange Pi RV2 specifications: SoC – Ky X1 CPU – 8-core 64-bit RISC-V processor GPU – Not mentioned VPU […]

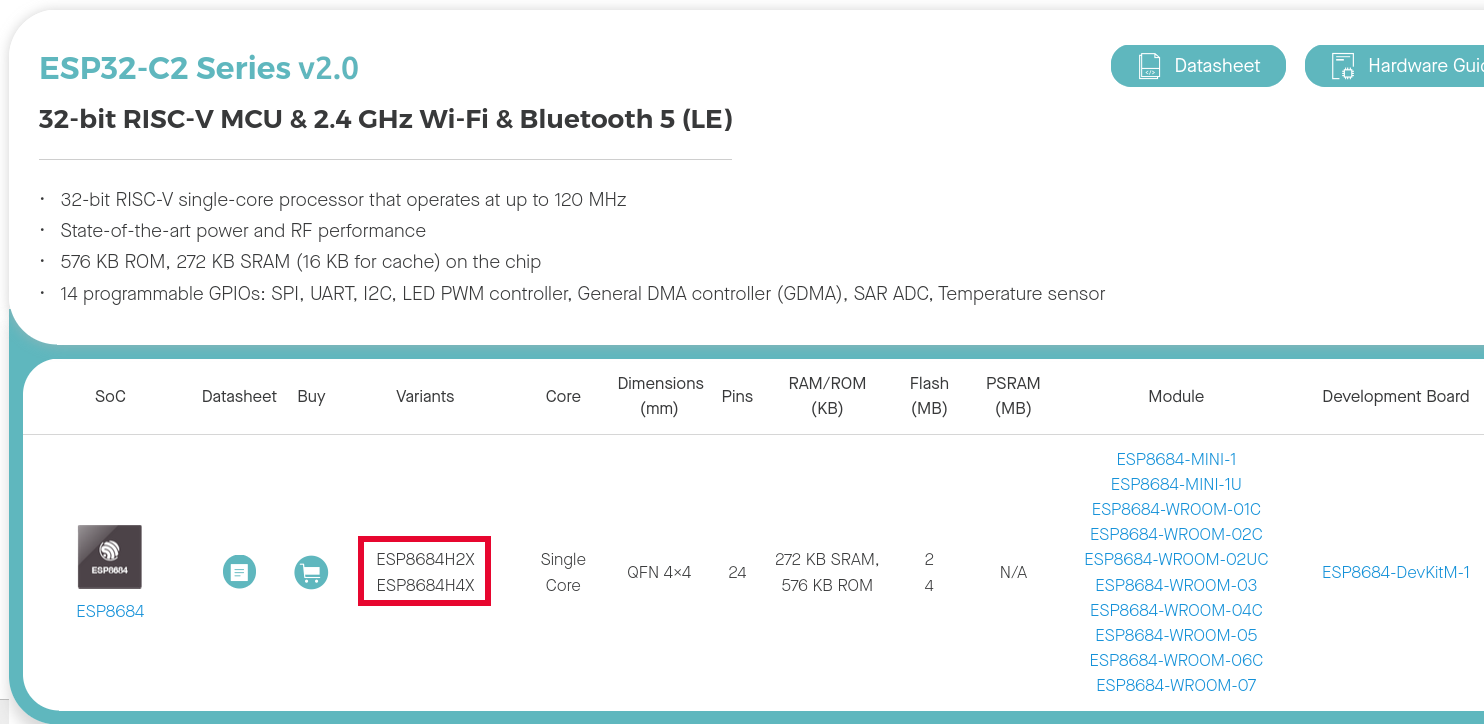

ESP32-C2 v2.0 wireless SoC adds 20 KB of additional SRAM, 100 KB of extra flash

Espressif ESP32-C2 (ESP8684) has been updated to v2.0 with 20 KB of additional SRAM, 100 KB of extra flash, with some improvements in terms of erase and program performance. The ESP32-C2 was first unveiled in April 2024 with limited details, and launched in October of the same year as the ESP8684 SiP combining ESP32-C2 die with 4MB flash, as well as a few ESP8684 modules and the ESP8684-DevKitM-1 development board. The ESP32-C2 is meant to be a cost-down version of the ESP32-C3 with less RAM and peripherals, and the ESP32-C2 v2.0 slightly improved on that with parts adding X to the name: ESP8684H2X (2MB flash) and ESP8684H4X (4MB flash). Modules and devkit names are also impacted, albeit not shown yet in the screenshot below. The part names had to be updated because chip revision v2.0 and previous chip revisions are not software-compatible, so Espressif had to update the ordering codes […]