Brillo Project was renamed to Android Things with the release of a developer preview back in December 2014, and the operating system enabling developers and companies to build and maintain Internet of Things devices at scale. The OS has now graduated so-to-speak with the release of Android Things 1.0 with long-term support for production devices, and this was to be expected as several Android Things devices were announced earlier this year. The new release adds supports for new system-on-modules (SoMs) based on the NXP i.MX8M, Qualcomm SDA212, Qualcomm SDA624, and MediaTek MT8516 SoCs. These modules are certified for production use with guaranteed long-term support for 3 years, and development hardware and reference designs for these SoMs will be available in the coming months. The Raspberry Pi 3 Model B and NXP i.MX7D boards and system-on-modules are still supported, but support for NXP i.MX6UL devices will be deprecated. Check out the […]

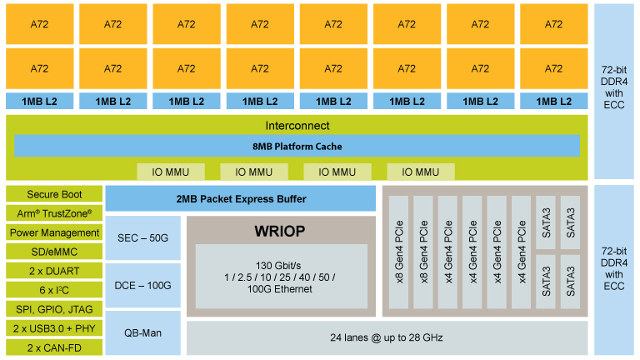

NXP QorIQ LayerScape LX2160A is a 16-core Arm Cortex A72 Communication Processor with 100 Gbit/s Ethernet

NXP Semiconductors has been working on a high-end communication processor with their QorIQ LayerScape LX2160A SoC equipped with 16 Arm Cortex A72 cores, 16 Ethernet ports supporting 1 to 100 Gbit/s, as well as 24 PCIe Gen4 lanes, and four SATA 3.0 ports. NXP LX2160A key specifications / features: Processor – 16x Arm Cortex-A72 CPU cores, running up to 2.2GHz with 8MB L2 cache, 8MB platform cache Memory I/F – 2 x DDR4 72b including ECC, up to 3200 MT/s, maximum capacity of 256 GB Storage – 4 x SATA3.0 Ethernet Up to 16 Ethernet ports Supported Ethernet speeds include 1, 2.5, 10, 25, 40, 50, and 100 gigabits per second 130Gbps Layer 2 Ethernet switch PCIe – Up to 24 PCIe Gen4 lanes, supporting ports as wide as x8 24 SerDes lanes, operating up to 28GHz Acceleration Engines – 50Gbps security accelerator, 100Gbps data compression/decompression engine Security – Secure […]

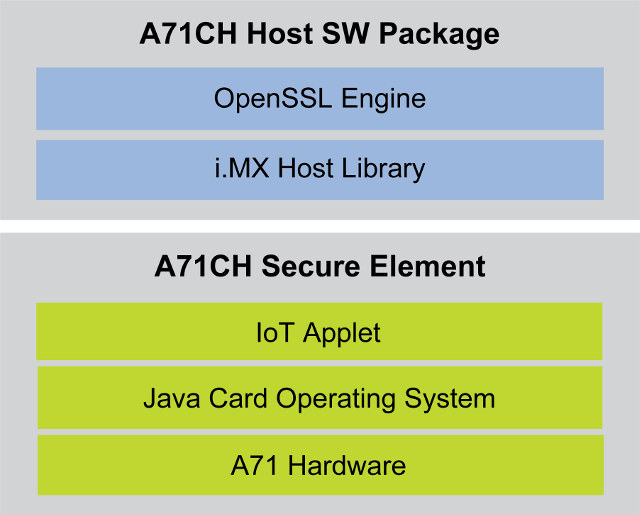

NXP Unveils A71CH Secure Element Chip for Secure Peer-to-Peer or Cloud Connections

The industry clearly has an issue at hand with the security of the Internet of Things, and the problem is complex as some devices are easily accessible due to bad configuration (e.g. default username/password), while others may have security flaws at various levels of the software stack from the low level bootloaders to the operating systems, and applications. Nowadays, devices also need to be upgradeable, and communicate with the cloud, and that introduces other attack vectors in case malignant firmware is installed instead, or a man-in-the-middle attack occurs. While some people may claim security can be achieved by software only, we are seeing security evolving towards combined software and hardware solutions, for example with Arm Trustzone built into SoCs, but some companies are also introducing Secure Element chip, which Samsung has already done and integrated into their Artik modules to secure data from the hardware to the cloud. NXP has […]

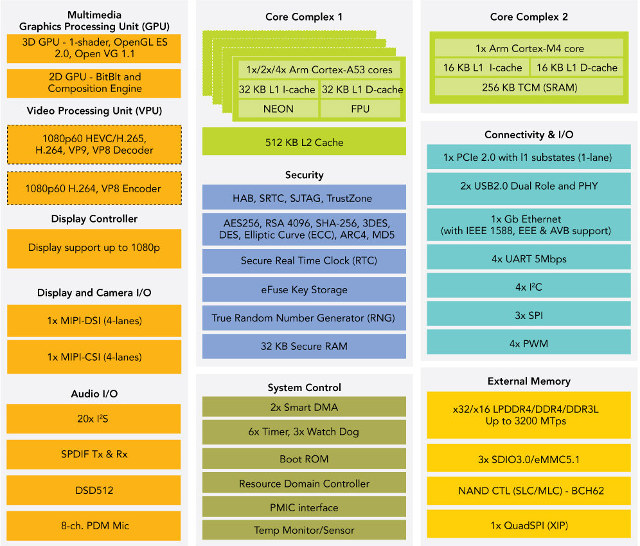

NXP i.MX 8M Mini Low Power Cortex A53/Cortex M4 Processor to be Manufactured using 14LPC FinFET Process Technology

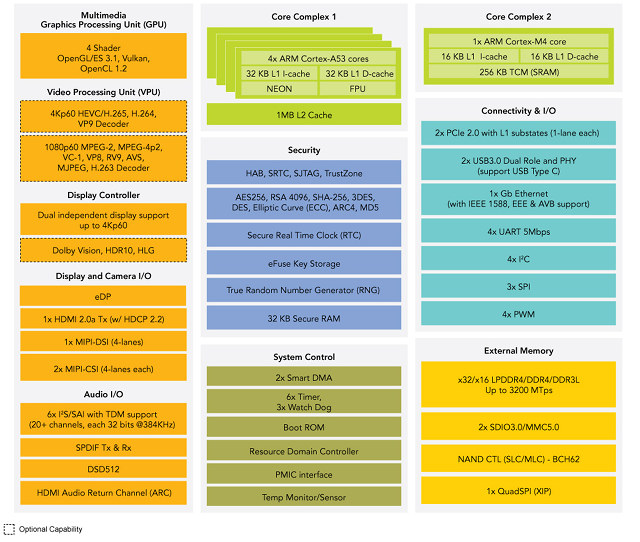

NXP i.MX 8, i.MX 8M, and i.MX 8X processors are barely available, but the company has already announced another member of their i.MX8 family with i.MX 8M Mini processors with one to four Cortex A53 application cores, one Cortex-M4F real-time core, 2D/ 3D graphics accelerator, and support for 1080p video playback and output. Apart from the lack of 4K support, that looks about the same as i.MX 8, but there’s one important difference: the manufacturing process. i.MX 8M Mini processors are manufactured using 14LPC FinFET process technology allowing the Cortex A53 cores to reach 2.0 GHz, and the Cortex-M4F core can be clocked up to 400+ MHz. Some video interfaces have also been removed from the new processor such as embedded DisplayPort and HDMI 2.0a. NXP i.MX 8M Mini key features: Application cores – One to four Arm Cortex-A53 cores up to 2GHz Real-time core – Arm Cortex-M4 at speeds […]

Develop NXP i.MX 8M Voice Controlled Smart Devices with MCIMX8M-EVK Evaluation Kit

We first heard about NXP i.MX 8M processsors in October 2016, and at the end of last year, WandPi 8M development board was unveiled with shipping scheduled for Q2 2018 once the processor will start manufacturing. Other exciting i.MX 8M projects include Purism Librem 5 smartphone, MNT Reform DIY modular computer, and I’m sure there will be others development board & products, and plenty of system-on-modules introduced with the processor in 2018. NXP i.MX 8M processor also got in the news at CES 2018, because it will be one of the hardware platforms certified for Android Things, and NXP also issued a press release to announced the processor’s multimedia capability with be used in voice controlled devices with or without video. The PR refers to Gartner Research saying that “voice commands will dominate 50 percent of all searches in the next two years”, and explains that with thinner and thinner […]

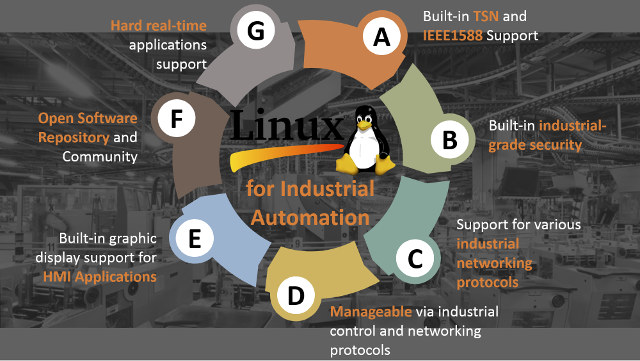

NXP Announces OpenIL Industrial Real-Time Linux Distribution for Industry 4.0

NXP has announced the release of OpenIL industrial Linux distribution with real-time OS extensions and Time-Sensitive Networking (TSN) support for factory-automation for the Industry 4.0 era. The OpenIL distribution includes support for per-stream policing, time-aware shaping of network traffic, and 801.1AS time synchronization, and supports NXP Layerscape SoCs and boards such as LS1028A dual ARMv8 processor, or LS1021A-IOT IoT gateway. Some notable OpenIL features include: Xenomai real-time extensions to Unix, making porting relatively easy from an RTOS like VxWorks or pSOS Extensible Markup Language (XML) and NETCONF-based network configuration utilities for TSN Generalized precision time protocol (gPTP) with the linuxptp daemon Drivers for the Ethernet Interfaces and the NXP SJA1105T TSN switch Support for edge computing services Optional instantiation of the Ubuntu user-space filesystem layout You’ll find the source code on Gihub, and some more information on OpenIL.org website. NXP appears to be the only company involved in the project, […]

Octo SPI / HyperBus Interface is Designed for High Speed Serial Flash, RAM, and MCP

So far, if you needed high speed storage with low pin count in your MCU based board, you could use QSPI (Quad SPI) NOR flash, but earlier this month I wrote about STM32L4+ MCU family, which added two Octo SPI interfaces. I had never heard about Octo SPI previously. Those two interfaces can be used with single, dual, quad, or octal SPI compatible serial flash or RAM, and support a frequency of up to 86 MHz for Octal SPI memories in STM32L4+ MCU. STMicro OctoSPI interface also supports Cypress/Spansion Hyperbus mode to connect to HyperFlash or HyperRAM chip, or even HyperFlash + HyperRAM Multi-Chip packages (MCP), and variable or fixed external memory latency as defined by the Hyperbus protocol specification. The latter reveals Hyperbus supports performance up to 400 MB/s (provided the controller support 200 MHz), and relies on either 11 bus signals using 3.0V I/O (Single-ended clock CK), or […]

Emcraft Releases Linux BSP for NXP i.MX RT1050 Cortex M7 Evaluation Board

NXP iMX RT series is a family of ARM Cortex M7 processors clocked at 600 MHz, making the solution a “crossover embedded processor” bridging the gap between real-time capabilities of micro-controllers and the performance of application processors. This week, NXP provided some benchmark numbers for i.MX RT1050 processor, which delivers a CoreMark score of 3020, DMIPS of 1284, and 20ns interrupt latency at 600 MHz, which means it could be a good candidate for embedded Linux, and Emcraft Systems has just released a uCLinux BSP for the NXP i.MX RT1050 EVK board. The BSP features U-Boot v2017.09-rc1, Linux Kernel 4.5 with relevant device drivers such as key I/O interfaces, Wi-Fi, SD card, LCD, etc…, and GNU development tools such as a GCC 4.7 toolchain, GDB, and so on. The company has made a demo with a GUI application designed with Crank Software’s Storyboard Suite, and running in Linux on the […]