Linus Torvalds has just released Linux 5.0: Ok, so the last week of the 5.0 release wasn’t entirely quiet, but it’s a lot smaller than rc8 was, and on the whole I’m happy that I delayed a week and did an rc8. It turns out that the actual patch that I talked about in the rc8 release wasn’t the worrisome bug I had thought: yes, we had an uninitialized variable, but the reason we hadn’t immediately noticed it due to a warning was that the way gcc works, the compiler had basically initialized it for us to the right value. So the same thing that caused not the lack of warning, also effectively meant that the fix was a no-op in practice. But hey, we had other bug fixes come in that actually did matter, and the uninitialized variable _could_ have been a problem with another compiler. Regardless – all […]

Linux 4.20 Release – Main Changes, Arm and MIPS Architectures

After Greg K-H handling Linux 4.19 release, Linus Torvalds is back at the helm, and released Linux 4.20 just before Christmas: Let’s face it, last week wasn’t quite as quiet as I would have hoped for, but there really doesn’t seem to be any point to delay 4.20 because everybody is already taking a break. And it’s not like there are any known issues, it’s just that the shortlog below is a bit longer than I would have wished for. Nothing screams “oh, that’s scary”, though. And as part of the “everybody is already taking a break”, I can happily report that I already have quite a few early pull requests in my inbox. I encouraged people to get it over and done with, so that people can just relax over the year-end holidays. In fact, I probably won’t start pulling for a couple of days, but otherwise let’s just […]

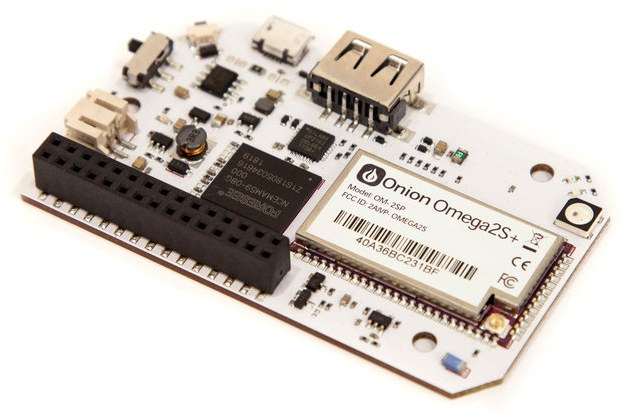

Onion Omega2 Pro OpenWrt Linux IoT Board Comes with 8GB Storage (Crowdfunding)

Onion Omega2 and Omega2 Plus are MediaTek MT7688 MIPS based WiFi boards for IoT applications that were launched in 2016 for as low as $5. Both boards run OpenWrt (LEDE at the time), and Omega2 Plus included more memory and storage with respectively 128MB RAM, 32MB flash and a micro SD card. But Onion team found out that many users needed more storage space, and they’ve now come up with Omega2 Pro model with the same processor, 128MB RAM, and large 8GB flash considering we’re talking about a board running OpenWrt 18.06 here. Onion Omega2 Pro specifications: Wireless Module – Onion Omega2S+ with SoC – MediaTek MT7688 MIPS processor @ 580 MHz System Memory – 128MB DDR2 RAM Connectivity – 2.4 GHz 802.11 b/g/n Wi-Fi 4 Antenna – 2 dBi directional chip antenna (on mainboard) & u.FL connector for external antenna (on-module) Storage – 8 GB eMMC flash USB – […]

Wave Computing to Open Source MIPS Architecture

There has been a lot of talks about RISC-V open source, royalty-free instructions set architecture this year, including the launch of RISC-V MCUs and Linux capable RISC-V processors, and corresponding development boards such as Hifive Unleashed. This even lead Arm to create a – now shutdown – microsite telling why people should stick with Arm instead of RISC-V. While RISC-V was clearly on the rise this year, MIPS architecture once a dominant players in routers and set-top box has been on the decline, even prompting Blu to write a guest review entitled “Baikal T1 MIPS Processor – The Last of the Mohicans?” hinting at the near extincsion of MIPS based solutions. But there may be hope, or at least a last ditch effort, with Wave Computing purchasing MIPS from Imagination Technology earlier this year, and now announcing the MIPS Open Initiative to effectively open source 32-bit and 64-bit MIPS ISA […]

Linux 4.19 Release – Main Changes, Arm and MIPS Architectures

With Linus Torvalds taking a leave from the Linux kernel project, Greg Kroah-Hartman was the one to release Linux 4.19 last Sunday: Hi everyone! It’s been a long strange journey for this kernel release… While it was not the largest kernel release every by number of commits, it was larger than the last 3 releases, which is a non-trivial thing to do. After the original -rc1 bumps, things settled down on the code side and it looks like stuff came nicely together to make a solid kernel for everyone to use for a while. And given that this is going to be one of the “Long Term” kernels I end up maintaining for a few years, that’s good news for everyone. A small trickle of good bugfixes came in this week, showing that waiting an extra week was a wise choice. However odds are that linux-next is just bursting so […]

Baikal T1 MIPS Processor – The Last of the Mohicans?

CNXSoft: Guest post by Blu about Baikal T1 development board and SoC, potentially one of the last MIPS consumer grade platforms ever. It took me a long time to start writing this article, even though I had been poking at the test subject for months, and I felt during that time that there were findings worth sharing with fellow embedded devs. What was holding me back was the thought that I might be seeing one of the last consumer-grade specimen of a paramount ISA that once turned upside-down the CPU world. That thought was giving me mixed feelings of part sadness, part hesitation ‒ to not do some injustice to a possibly last-of-its-kind device. So it was with these feelings that I took to writing this article. But first, a short personal story. Two winters ago I was talking to a friend of mine over beers. We were discussing CPU […]

Linux 4.18 Release – Main Changes, Arm and MIPS Architecture

Linus Torvalds has just announced the release of Linux 4.18: One week late(r) and here we are – 4.18 is out there. It was a very calm week, and arguably I could just have released on schedule last week, but we did have some minor updates. Mostly networking, but some vfs race fixes (mentioned in the rc8 announment as “pending”) and a couple of driver fixes (scsi, networking, i2c). Some other minor random things (arm crypto fix, parisc memory ordering fix). Shortlog appended for the (few) details. Some of these I was almost ready to just delay to until the next merge window, but they were marked for stable anyway, so it would just have caused more backporting. The vfs fixes are for old races that are really hard to hit (which is obviously why they are old and weren’t noticed earlier). Some of them _have_ been seen in real […]

Linux 4.17 Release – Main Changes, Arm & MIPS Architectures

Linus Torvalds released Linux 4.17 last Sunday: So this last week was pretty calm, even if the pattern of most of the stuff coming in on a Friday made it feel less so as the weekend approached. And while I would have liked even less changes, I really didn’t get the feeling that another week would help the release in any way, so here we are, with 4.17 released. No, I didn’t call it 5.0, even though all the git object count numerology was in place for that. It will happen in the not _too_distant future, and I’m told all the release scripts on kernel.org are ready for it, but I didn’t feel there was any real reason for it. I suspect that around 4.20 – which is I run out of fingers and toes to keep track of minor releases, and thus start getting mightily confused – I’ll switch […]