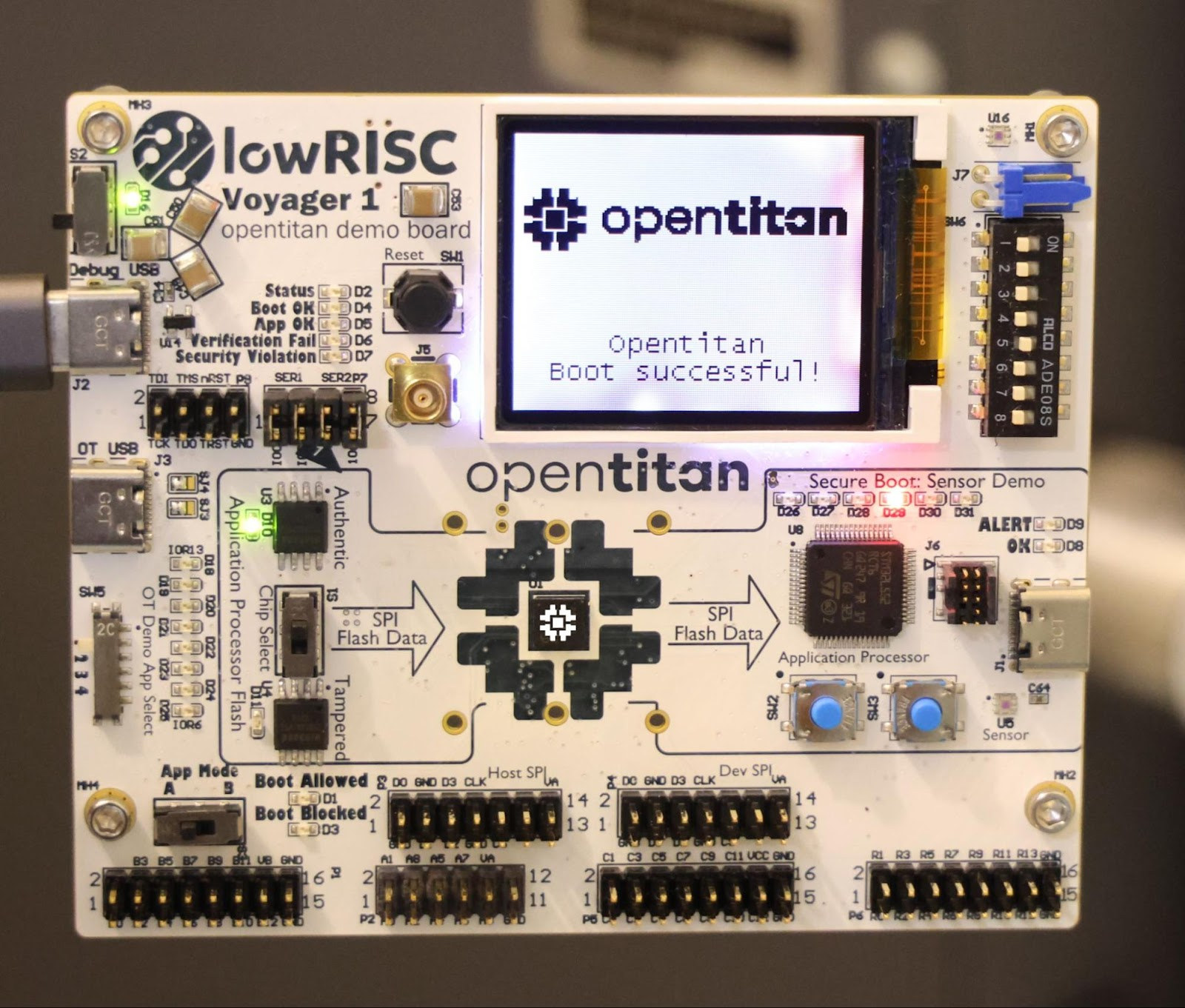

Google has announced the start of the fabrication of a Nuvoton security chip featuring OpenTitan open-source silicon Root of Trust (RoT), the first such production-ready chip. It will soon be available in lowRISC’s Voyager 1 demo board, and later this year in Chromebooks and data centers. We first wrote about OpenTitan open-source Root of Trust (RoT) chips in 2020 as a collaboration between Google, Seagate, Nuvoton, Western Digital, lowRISC, as well as some other companies, projects, and universities that aimed at “building a transparent, high-quality reference design and integration guidelines for silicon root of trust (RoT) chips”. OpenTitan itself reached commercial availability last year, after the first engineering samples were released in 2023, and Google now says the Nuvoton chip (yet to have a proper name) is the first production-ready OpenTitan chip. Hardware Root of Trust (RoT) are small secure microcontrollers that are the equivalent of Certificate Authorities (CAs) to […]

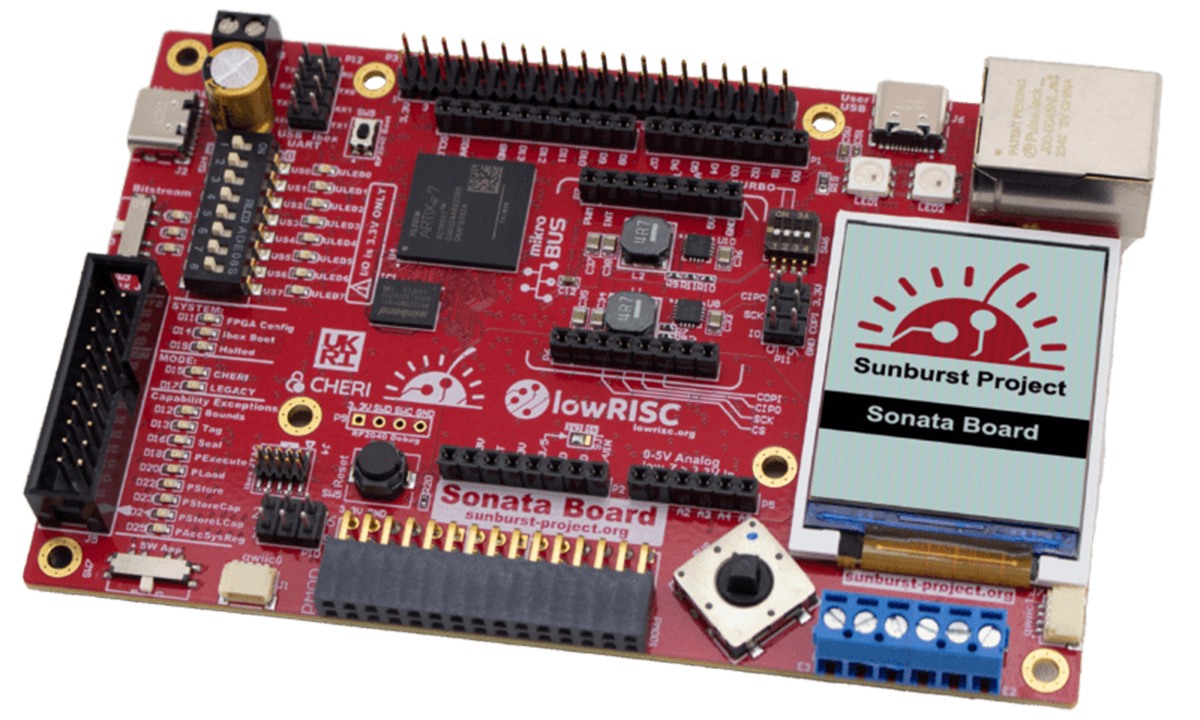

Sonata v1.0 RISC-V platform combines AMD Artix-7 FPGA and Raspberry Pi RP2040 MCU, features CHERIoT technology for secure embedded systems

lowRISC has released Sonata v1.0, a stable platform developed under the Sunburst project. Designed for embedded systems engineers, Sonata supports CHERIoT technology, enabling features like compartmentalization and enhanced memory safety. It provides a reliable foundation for building secure embedded systems. CHERIoT is a security-focused technology built on lowRISC’s RISC-V Ibex core, based on CHERI research from the University of Cambridge and SRI International. It addresses memory safety issues like buffer overflows and use-after-free errors using CHERI’s capability-based architecture. The CHERIoT capability format includes permissions for memory access, object types for compartmentalization, and bounds to restrict accessible memory regions. These features enable scalable and efficient compartmentalization, making it suitable for securely running untrusted software in embedded systems. Sonata v1.0 leverages this architecture to isolate components like network stacks and kernels within the CHERIoT RTOS. The lowRISC Sonata v1.0 specifications: FPGA – AMD Xilinx Artix-7 (XC7A35T-1CSG324C) CPU – AMD MicroBlaze soft-core based on […]

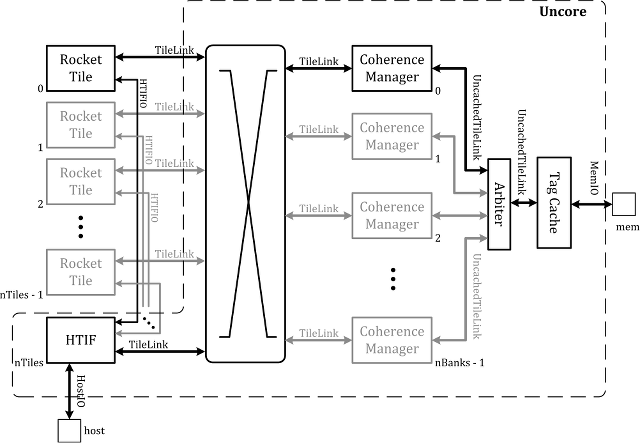

lowRISC Open Source SoC Project Announces its First Release with Tutorials for Simulators and Zedboard

lowRISC project aims to produce a completely open-source SoC (System-on-Chip) based on the 64-bit RISC-V instruction set architecture, as well as a corresponding development board, thus eventually producing a fully open hardware systems. The project has now announced its first release “tagged memory preview release” with a tutorial explaining how this has all been designed, and how to run simulations with software tools, or FPGA boards such as Zedboard. The project is based on Rocket core, written in Chisel language by the RISC-V team at UC Berkeley. Chisel can generate code to produce a cycle-accurate C++ emulator, Verilog optimised for FPGAs or Verilog for use in an ASIC flow.If you want to try it out, you’ll need a Linux machine, preferably running Ubuntu 14.04 64-bit, with GNU GCC 4.8 installed, and follow the tutorial in order to get the source code, and build tools such as riscv64-unknown-elf-gcc compiler, and […]

Google Summer of Code 2015 is Now Open for Student Applications

Google has now announced that students applications for Google Summer of Code (GSoC) are now open. Students can get paid up to $5,500 to work on various open source projects selected for the event. Fewer companies have been accepted this year, and even big names like the Linux Foundation and Mozilla got their application rejected. There are still over 137 open source projects to work on including: MinnowBoard project – Potential software projects for the Intel Atom embedded board include making low speed I/O buses more accessible via intermediate open source libraries (e.g. SMBus/PMBus/Wiring libraries), and improving the open source firmware. lowRISC SoC project – Potential projects: Schematic Viewer for Netlists (SVG/JavaScript), open source FPGA compilation flow using Yosys, accessing the OpenCores ecosystem, etc… BeagleBoard.org – Lots of project ideas relying on the BeagleBone Black board, dealing with Linux kernel support for embedded devices and interfaces, ARM processor support in […]