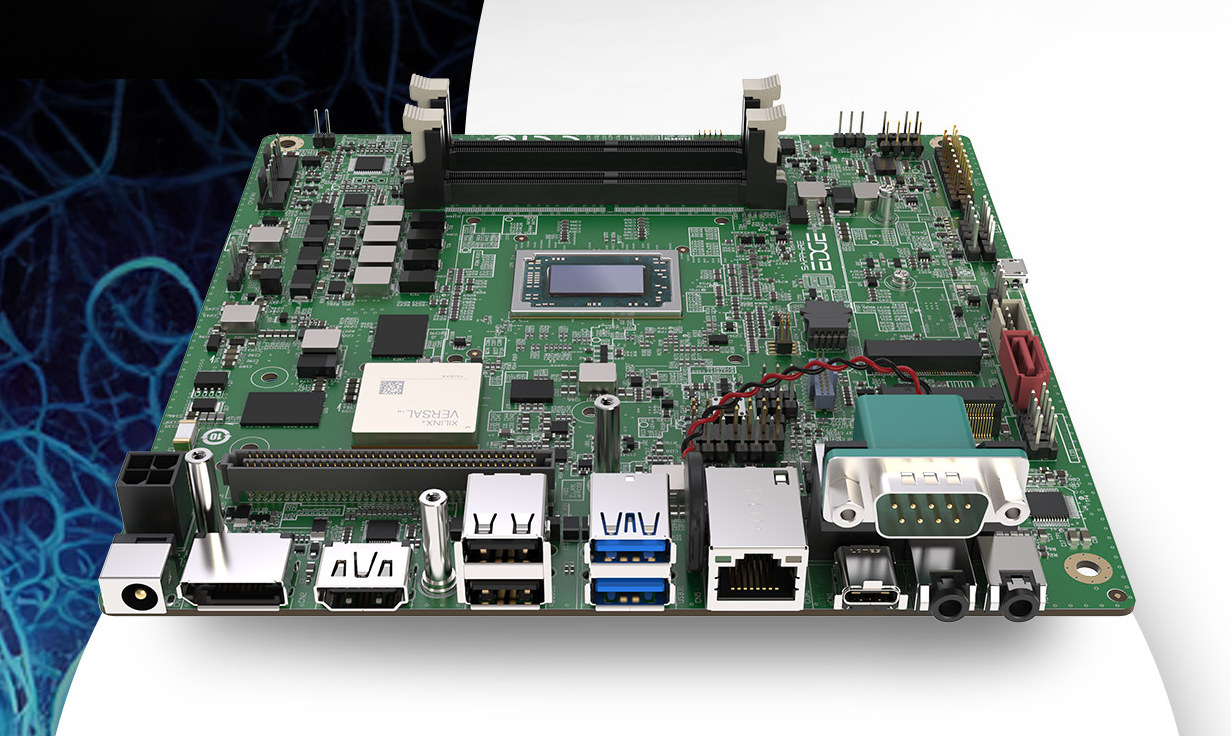

Sapphire Edge+ VPR-4616-MB is a new mini-ITX motherboard on the “new” AMD Embedded+ “architecture” comprised of an AMD Ryzen Embedded R2314 processor and an AMD Versal AI Edge VE2302 adaptive SoC (also called FPGA SoC…). The motherboard supports up to 64GB ECC/non-ECC DDR4 memory for the CPU, 8GB of memory for the adaptive SoC, supports SATA and NVMe storage, dual video output, 2.5GbE networking, and offers a range of USB ports and M.2 sockets for expansion. AMD Embedded+ solutions target sensor fusion, AI inferencing, industrial networking, control, and visualization applications. SAPPHIRE Edge+ VPR-4616-MB specifications: AMD Embedded+ Architecture Adaptive SoC Subsystem Main IC – AMD Versal AI Edge VE2302 with dual Arm Cortex-A72 core processor @ up to 1.6 GHz, dual-core Arm Cortex-R5F, 23 TOPS AI engine, FPGA fabric, etc… System Memory – 2x 4GB LPDDR4 Storage 1Gbit OSPI NOR flash for local boot 64 Kbit EEPROM for Board-ID Expansion 160-pin […]

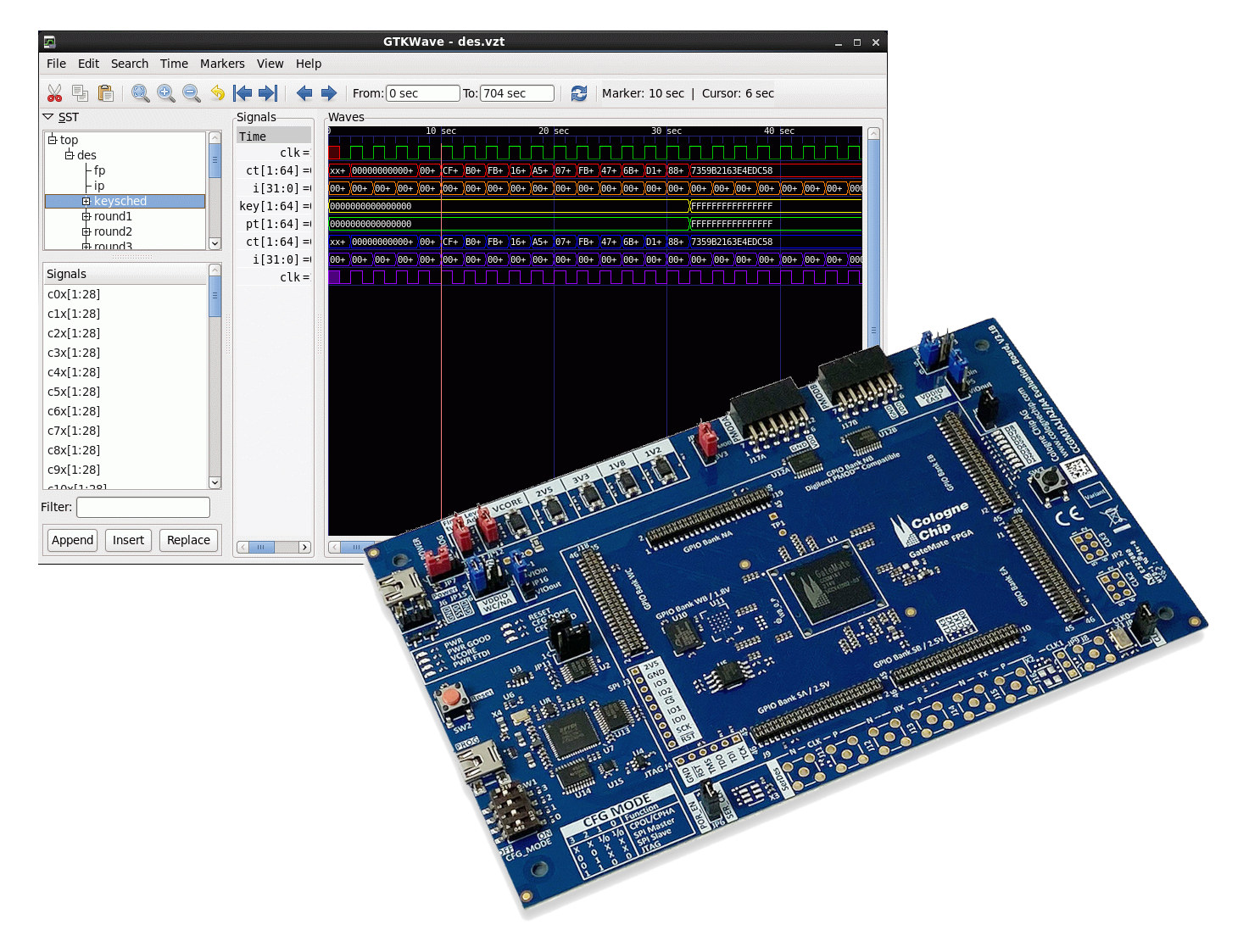

Cologne Chip releases an open-source integrated logic analyser (ILA) for GateMate FPGA chips

Cologne Chip’s “Integrated logic analyzer” (ILA) project is an open-source Verilog implementation of a logic analyzer running on the company’s GameMate A1 FPGA and designed to capture internal signals. When we first covered the GameMate A1 FPGA we noted Cologne relies on the open-source Yosys framework coupled with a proprietary, but free-of-charge, place & route tool contrary to most other FPGA vendors that only offer closed-source proprietary development tools. The German company has now released the GateMate integrated logic analyzer project to help customers debug their FPGA designs. The project includes the digital circuit of the ILA designed in the hardware description language Verilog and a Python program (ILA Control Program) used to configure the configuration of the ILA from the design under test (DUT) and provide an interface with the user during the debugging process. The user will also need a GateMate FPGA toolchain and GTKWave open-source program to […]

iW-RainboW-G58M is a compact module based on the Intel Agilex 5 SoC FPGA series

iWave Systems, an embedded systems solutions company based in India, has announced the launch of the iW-RainboW-G58M system-on-module (SoM). The module is based on Intel’s Agilex 5 SoC FPGA E-series family, a lineup of affordable, midrange FPGAs for intelligent edge and embedded applications. The Agilex 5 E-series is optimized to deliver better performance-per-watt than its predecessors at a smaller form factor. They feature an asymmetric applications processor system comprising two Arm Cortex-A76 cores and two Cortex-A55 cores for optimized performance and power efficiency. The Arm cores in the Agilex 5 SoC FGPA family are more powerful than the Cortex-A53 cores in the Intel Agilex 7 and 9 products, but those have faster high-speed interfaces and more logic elements. The Agilex 5 SoM is suitable for development in fields like wireless communications, video/broadcast, and industrial test and measurement sectors. The last iWave module we covered, the iW-RainboW-G55M, was based on a […]

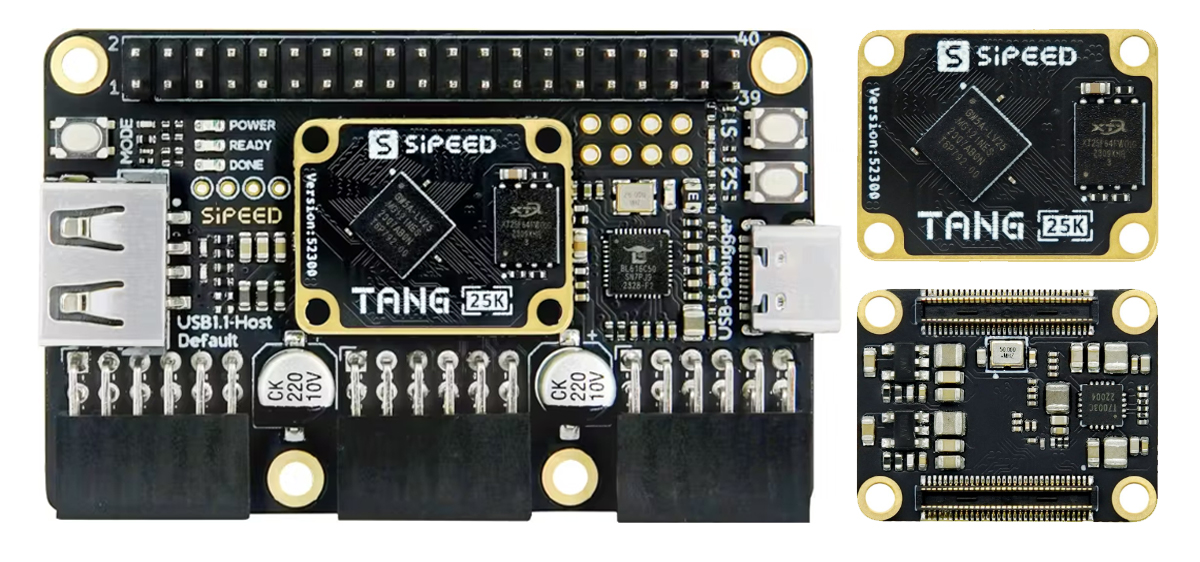

Sipeed Tang Primer 25K board features 23,040 Logic Cells for FPGA prototyping and development

Sipeed has recently introduced the Tang Primer 25K, an FPGA board powered by Gowin Semi GW5A-LV25MG121 chip. This board features 23,040 LUTs, USB Host capability, and an optional SDRAM module that unlocks vintage gaming. We have previously covered many FPGA boards like Sipeed Tang Mega 138K Pro, Fudan Micro JFM7K325T, ILYGO T-FPGA, and many other development boards by Sipeed including the Sipeed Tang Nano 20K with a Gowin GW2A FPGA. You can check those out if interested. The Tang Primer 25K development board is divided into the 25K SoM Board and the 25K Dock Board together they offer a comprehensive set of features: GW5A-LV25MG121 specifications: 23040 LUT4 23040 Registers (FF) 28x 18×18 Multipliers 6x PLLs Memory/Storage: 64Mbit NOR Flash 180K Distributed S-SRAM 1008K B-SRAM (bits) 56 Number of B-SRAM I/O Interfaces: 3x PMOD 40-pin header 2x buttons 8x I/O banks 75x General IO MIPI IO – 4lane Data USB Ports: […]

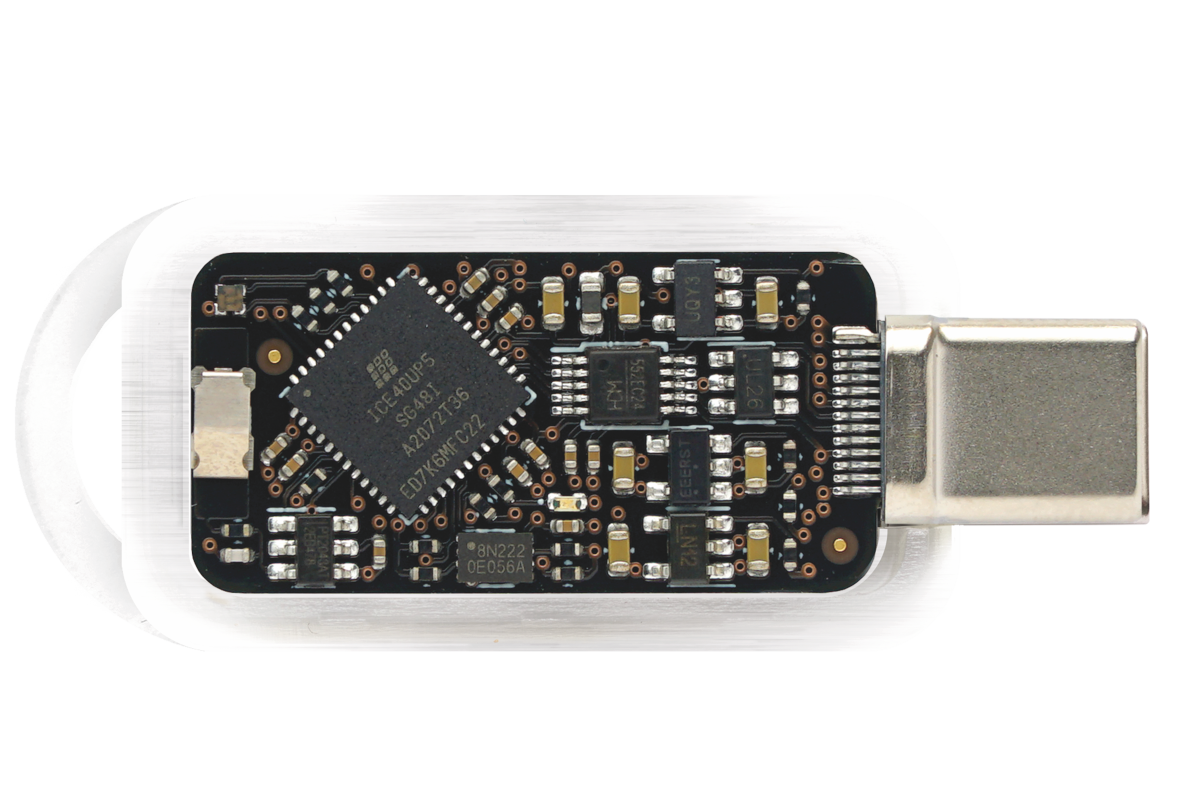

Tillitis Tkey is an open-source RISC-V security key in a USB-C case

Tillitis’ TKey is a small, simple security key in a USB-C form factor, and described as a “new type of flexible USB security token” that is inspired by DICE (Device Identifier Composition Engine) and measured boot powered by a simple 32-bit RISC-V core, the PicoRV32, in a Lattice iCE40 UP5K FPGA. While we have covered hardware security modules in the past, this is the first security key we have seen that is based on an FPGA running a RISC-V core. The security token lacks persistent, onboard storage, unlike alternatives such as Yubikey Neo. Apps need to be loaded onto the key every time it is connected to a host device. It uses measured boot to generate a unique identifier for each application and is more secure than the alternatives since private keys are not stored on the device. Also, the hardware and software for the TKey are completely open-source for […]

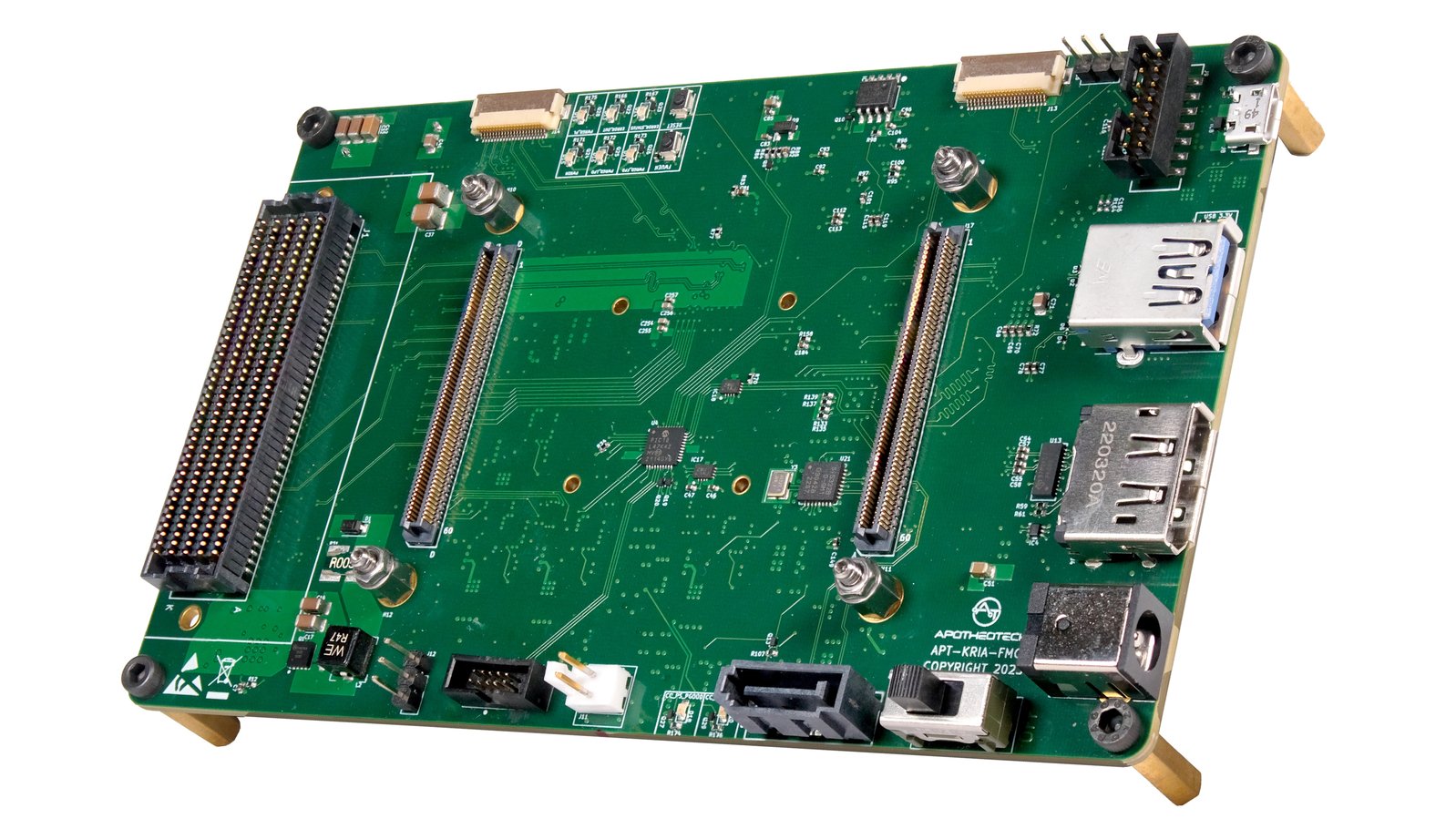

Aper-Oculus is an open-source camera development board for AMD Xilinx’s Kria SoM (Crowdfunding)

The Aper-Oculus board is an open-source hardware camera carrier board for the AMD Xilinx Kria system-on-modules aimed at high-speed computer vision applications. The carrier board is built around the Sony SLVS-EC (Scalable Low-Voltage Signaling with Embedded Clock), a high-speed interface standard that delivers high-resolution video output to the FPGA. It also features several connectivity options, including dual MIPI connectors, USB 3.0, DisplayPort, and SATA to accommodate the varying demands of AI and robotics projects. The Kria K24 and K26 SOMs are adaptive system-on-modules designed for edge and vision applications. These small modules are ruggedized and come with hardware acceleration enabled out-of-the-box. The Kria lineup also includes a series of starter kits, such as the KR260 Robotics Starter Kit, which are designed for early evaluation and development. Aper-Oculus specifications: Processor-Board Support – Compatible with AMD Xilinx Kria SOMs Video Interface – SLVS-EC for high-speed, high-quality video input Expansion – FMC connector […]

International Black Friday and Cyber Monday 2023 deals and coupon codes

We’ve been writing about international Black Friday and Cyber Monday deals and coupon codes since 2014, as US-centric promotions such as Amazon’s Black Friday and Cyber Monday deals are not always available to the international audience of CNX Software. So once again, we’ve searched at Black Friday and Cyber Monday 2023 international promotions and discount codes from specific manufacturers as well as popular online stores such as Aliexpress, Banggood, and others. Aliexpress Black Friday and Cyber Monday event Aliexpress will have a Black Friday (and Cyber Monday) event in 2023, but we have limited details at this time since it will only start on November 23, contrary to some of the other deals we’ll feature below which are already up and running. But the event will have two periods: Nov 20-22 PT – Warm Up event where users can find and add items to the cart before purchasing during the […]

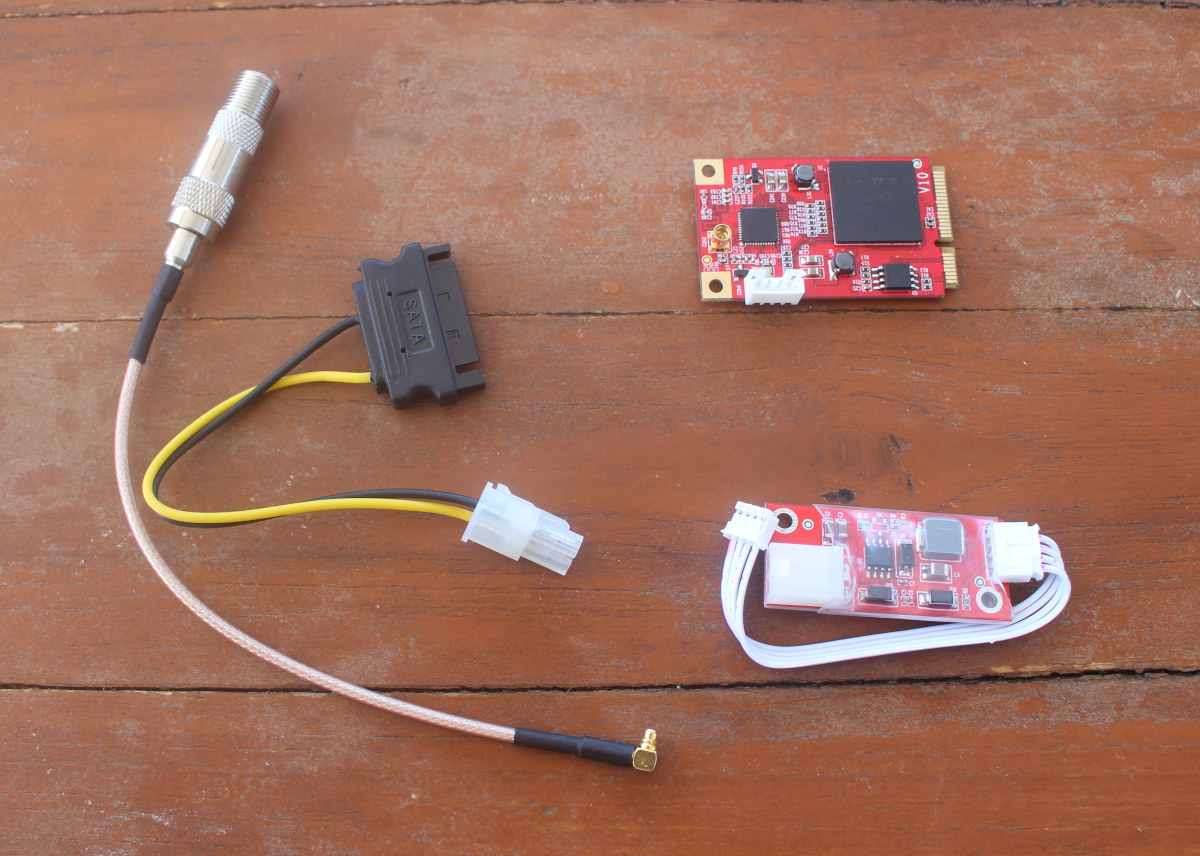

Giveaway Week 2023 – TBS7901 mini PCIe DVB-S2X/S2 module

The second prize of Giveaway Week 2023 is a TBS7901 mini PCIe DVB-S2X/S2 module designed to be connected to a PC or board with a mini PCIe socket in order to watch, record, or broadcast free-to-air video received from a satellite dish. I received both M.2 and mPCIe DVB-S2X modules last August, but I haven’t had time to test any of those yet. So I’m keeping the M.2 module for my own testing once time permits and will be giving away the mini PCIe module to one of CNX Software readers. The module comes with a coaxial antenna cable, as well as a TBS-7901PW power board and SATA power cable since DVB-S/S2/S2X satellite TV requires 13V and 18V DC as well which will be outputted won’t the power board using the 12V from a PSU. You’ll probably need a Windows machine too since TBS provides Windows drivers for the TBS7901 […]