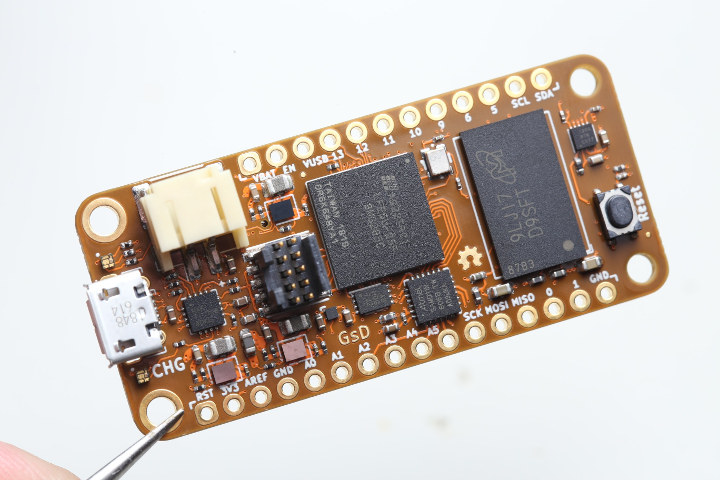

Lattice ECP5 FPGA powered OrangeCrab is the work of Greg Davill who designed the Adafruit Feather-compatible board in KiCAD, crowdsourced schematics/PCB checking and published his progress on Twitter, and published the files of the open source hardware board on Github. OrangeCrab board hardware specifications: FPGA – Lattice ECP5 25/45/85 variants System Memory – Up to 8Gbit DDR3 Memory (x16) Storage – 128Mbit QSPI FLASH Memory (Bitstream + User storage), 4-bit MicroSD socket USB – Micro USB connector, full-speed direct USB connection to FPGA Programming – 10-pin FPGA programming header Expansion – I/O’s broken out via 30 through holes: GPIO, SPI, I2C, Analog, … 7x diff pairs, 1x single ended only Misc – Reset Button, charge LED (Green: external power, Yellow: when charging, No color: when running off battery), 48MHz Oscillator Power Supply – 5V via USB port, battery header for LiPo battery + battery charger chip Dimensions – Adafruit Feather […]

Intel Agilex SoC FPGA Features Four Arm Cortex-A53 Cores

Intel announced their new Agilex FPGA family manufactured with a 10nm process earlier this April, but it only caught my eyes recently when I saw “Agilex SoC FPGA” listed in Linux 5.2 Arm’s changelog. The Intel SoC FPGA is there simply because it comes with four Arm Cortex-A53 cores. Three family have been announced so far, although the later is shown as coming soon: Intel Agilex F-Series FPGAs and SoCs – Transceiver support up to 58 Gbps, increased DSP capabilities, high system integration, and 2nd Gen Intel Hyperflex architecture for a wide range of applications in Data Center, Networking, and Edge. Option to integrate the quad-core Arm Cortex-A53 processor. Intel Agilex I-Series SoC FPGAs – Optimized for high performance processor interface and bandwidth intensive applications. Coherent attach to Intel Xeon processors with Compute Express Link, hardened PCIe Gen 5 support and transceiver support up to 112 Gbps. Intel Agilex M-Series […]

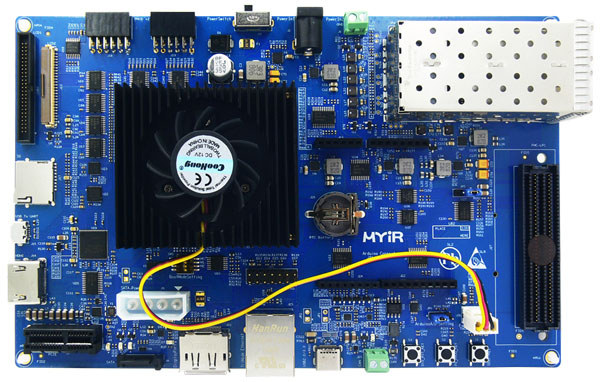

MYIR Announces Xilinx Zynq UltraScale+ MPSoC SoM and Development Board

MYIR Technology has been selling Xilinx Zynq-7000 FPGA + Arm systems-on-module since 2016, but the Chinese company has now announced new modules based on the more powerful Xilinx Zynq Ultrascale+ MPSoC with Arm Cortex-A53 cores, Arm Cortex-R5 cores, and Ultrascale FPGA fabric, as well as a corresponding development board. MYC-CZU3EG Zynq UltraScale+ MPSoC CPU Module CPU module specifications: MPSoC – Xilinx Zynq UltraScale+ XCZU3EG-1SFVC784E (ZU3EG, 784 Pin Package) MPSoC with quad-core Arm Cortex-A53 processor @ 1.2 GHz, dual-core Cortex-R5 processor @ 600 MHz, Arm Mali-400MP2 GPU, and 16nm FinFET+ FPGA fabric (154K logic cells, 7.6 Mb memory, 728 DSP slices) System Memory – 4GB DDR4 @ 2,400MHz Storage – 4GB eMMC Flash, 128MB QSPI Flash On-module chips Gigabit Ethernet PHY USB PHY Intel Power Module Clock Generator 2x Samtec 0.5mm pitch 160-pin high-speed headers bringing out Networking – Gigabit Ethernet USB – USB 2.0 interface 4x PS GTR transceivers along with […]

Arm Techcon 2019 Schedule – Machine Learning, Security, Containers, and More

Arm TechCon will take place on October 8-10, 2019 at San Jose Convention Center to showcase new solutions from Arm and third-parties, and the company has now published the agenda/schedule for the event. There are many sessions and even if you’re not going to happen it’s always useful to checkout what will be discussed to learn more about what’s going on currently and what will be the focus in the near future for Arm development. Several sessions normally occur at the same time, so as usual I’ll make my own virtual schedule with the ones I find most relevant. Tuesday, October 8 09:00 – 09:50 – Open Source ML is rapidly advancing. How can you benefit? by Markus Levy, Director of AI and Machine Learning Technologies, NXP Over the last two years and still continuing, machine learning applications have benefited tremendously from the growing number of open source frameworks, tools, […]

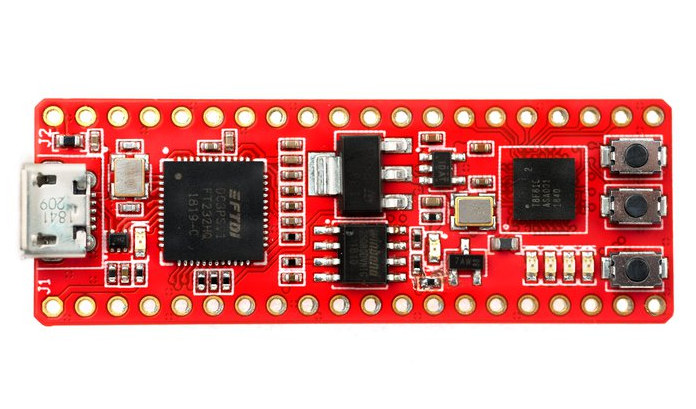

$30 FireAnt Development Board Features Efinix Trion T8 FPGA (Crowdfunding)

When I think FPGA, company names such as Xilinx, Altera (now Intel), or even Microsemi come to my mind. But there are also other companies such as Anlogic or Lattice Semi that offer FPGA chips. Today I’ve come across another FPGA silicon vendor, namely Efinix, with their Trion T8 FPGA found in XIPS Technology’s tiny FireAnt development board targeting makers and hardware designers. FireAnt specifications: FPGA – Efinix Trion T8 (T8F81C2) with 7384x LE counts, 8x embedded multipliers, 1x low-power oscillator, 1x PLL, 122.88 kbit internal RAM; Package – BGA-81 (5×5 mm) Storage – 8 Mbit serial NOR Flash Expansion – 2x 20-pin headers (soldered or unpopulated) with up to 35 GPIOs Debugging & Programming Micro USB 2.0 port via FTDI FT232HQ USB to serial chip JTAG signals in bottom layer Misc – Onboard 33.333 MHz crystal oscillator for PLL; 6x LEDs including 4 user configurable; 3x buttons (Reset, BTN1, […]

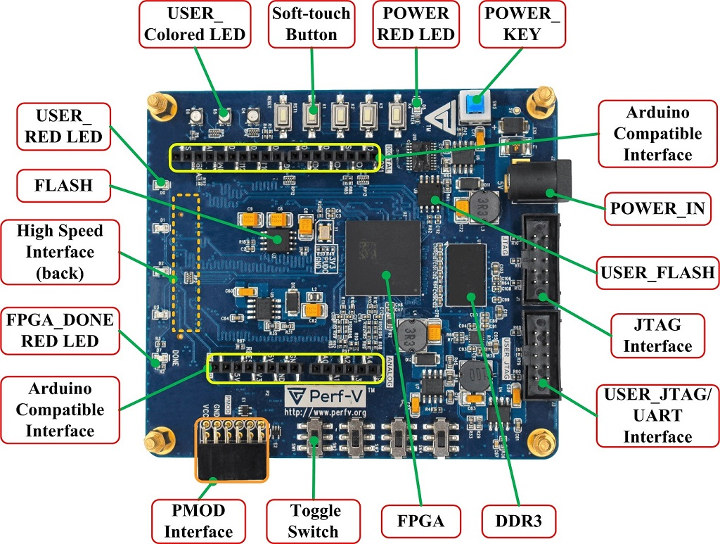

Perf-V is another FPGA based RISC-V Development Board

There are already some RISC-V development boards with silicon featuring RISC-V instruction set such as SiFive’s HiFive1 or Kendryte KD233 board. But beauty of RISC-V is that you can customize the instructions set, and if that’s your goal, an FPGA board provides the flexibility you need. While in theory you could use pretty much any FPGA board with enough logic elements, it may help to get started with boards that are designed for this purpose since the company already ported a RISC-V core to their platform and you can start from there. We’ve already covered a few of those including LicheeTang and Fomu boards, as well as ARIES M100PF PolarFire FPGA system-on-module. Today, I’ve come across another of those RISC-V FPGA board. Meet Perf-V board with the following specifications: FPGA – Xilinx Artix-7 XC7A35T-1FTG256C with 33280 Logic Cells, 90 DSP, 41600 CLBs, 1800 Kbit Block RAM, and 5 CMTs; Optional […]

Amungo NUT2NT+ is an Open Source High Precision GNSS Board (Crowdfunding)

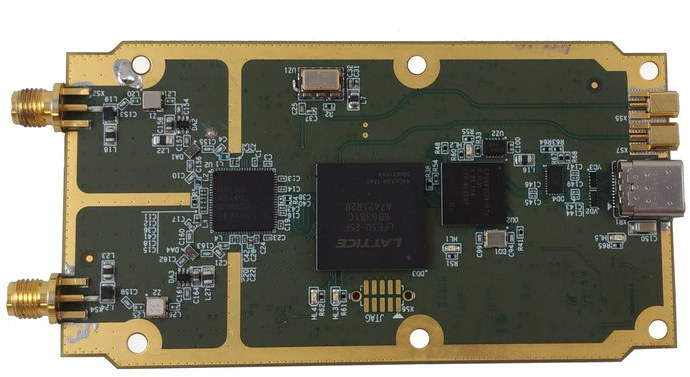

Amungo Navigation NUT2NT+ is an open-source hardware four-channel, all-frequency, GNSS RF-to-bits receiver for precision, satellite-based positioning. Connected to the right antennas, the board can achieve centimeter positioning resolution by connecting to multiple navigation satellite systems including GPS, GLONASS, Galileo, BeiDou, and IRNSS. Amungo claims that while several startups and large companies already offer proprietary GNSS positioning solutions NUT2NT+ is the only open source option in this class of GNSS devices. NUT2NT+ key features and specifications: Receiver chip – NTLab NT1065 4-Channel RF Front-End IC FPGA – Lattice ECP5 with 12K LUTs + 28 DSP blocks (LFE5U-12) opened for custom design USB – 1x USB 3.1 Type-C port via CYUSB3014 USB 3.0 controller: Clock – 10 MHz TCXO, soldered RF inputs – 2x bands dedicated; – 5 dB referred noise floor ADC – 2-bit resolution up to 99 MHz Samples transfer – Continuous full stream, from 10 to 50 Mbytes/sec GNSS […]

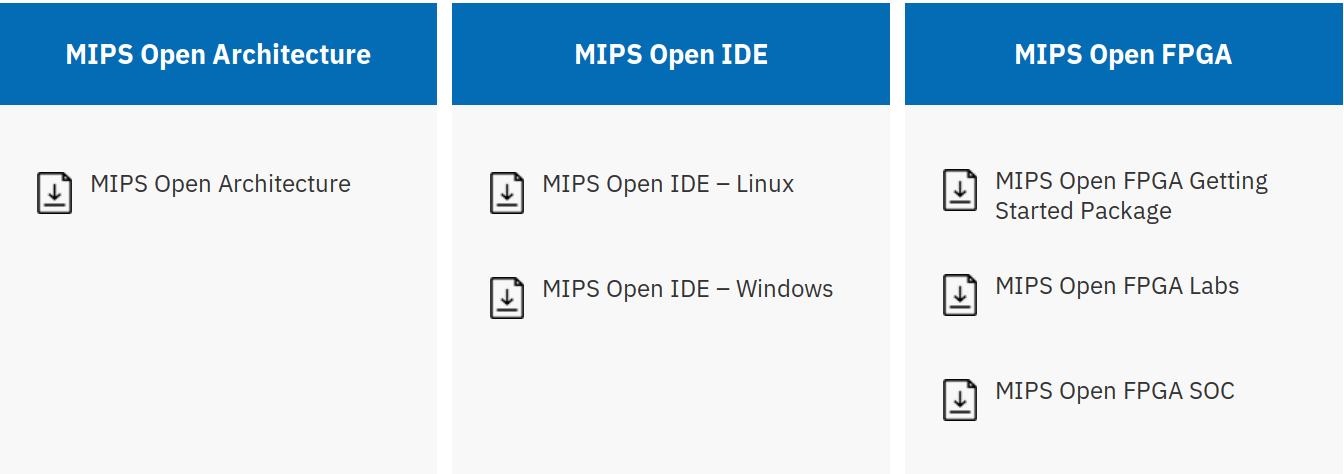

Wave Computing Announces the First MIPS Open Source Release

In a surprise announcement last year, Wave Computing revealed their plans to open source MIPS architecture, and more specifically the new MIPS Release 6 architecture. The company has now started to deliver the goods with the release of the first MIPS Open Program components. Specific components of the first release include: MIPS ISA – The latest R6 version of the MIPS 32-and-64-bit architecture, including extensions such as virtualization, multi-threading, SIMD, DSP and microMIPS code compression MIPS Open Tools – Integrated development environment for embedded real-time operating systems and Linux-based systems for embedded products that enable developers to build, debug and deploy applications on MIPS-based hardware and software platforms; MIPS Open Field Programmable Gate Arrays (FPGAs)– A complete training program for community members that includes: Getting Started Package – Provides the MIPS FPGA system as a set of Verilog files, plus an overview and instructions on how to use the MIPS […]