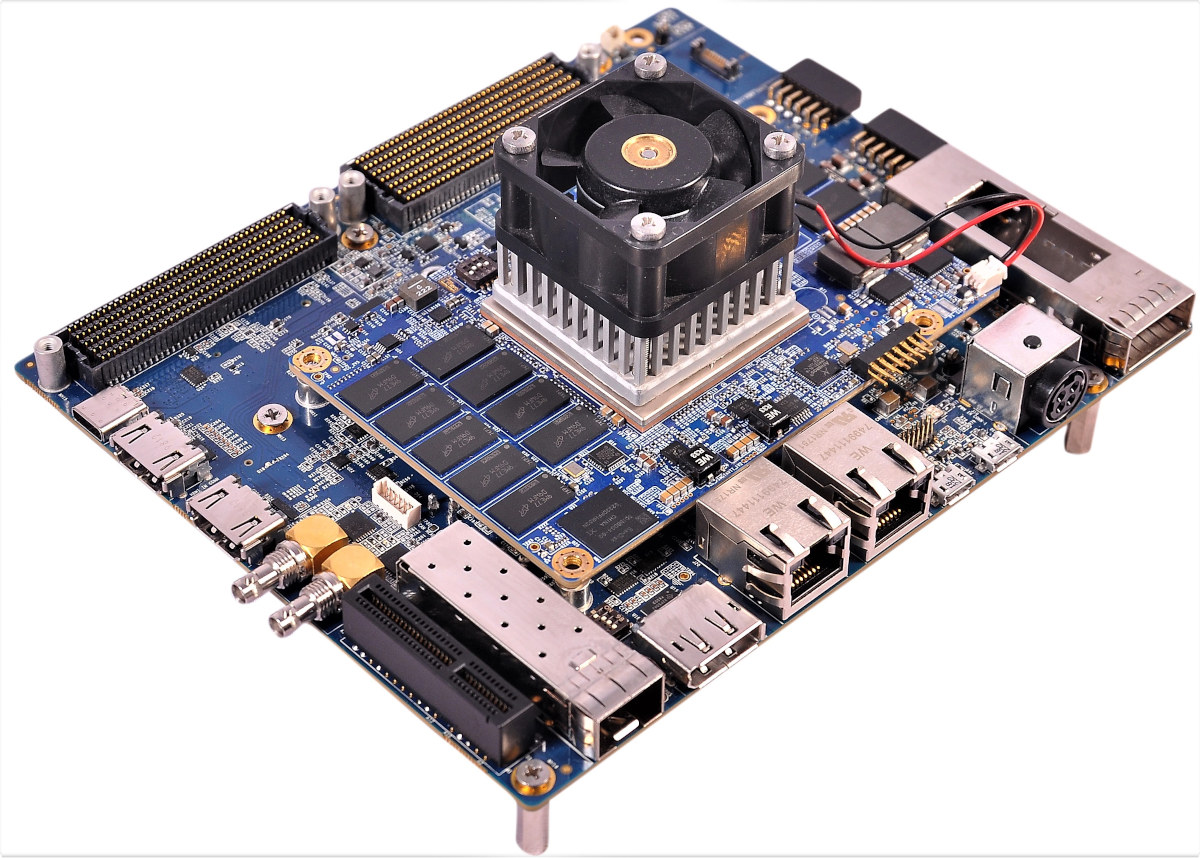

iWave Systems iW-RainboW-G35D is a development kit powered by Xilinx Zynq UltraScale+ ZU19EG Arm Cortex-A53 and FPGA MPSoC coupled with 4GB DDR4 RAM with ECC for the processing system (PS) & 4GB dual-channel DDR4 RAM for the programmable logic (PL). The board is equipped with HDMI 2.0 output/input ports supporting 4Kp60 UHD resolutions, a 10GbE SFP+ cage, FMC+, FMC, FireFly, and QSFP connectors for high-speed transceivers, and more. iW-RainboW-G35D specifications: iW-RainboW-G35M SoM Xilinx Zynq Ultrascale+ ZCU19EG MPSOC (-1 speed) with four Cortex-A53 cores @ 1200 MHz, dual-core Arm Cortex-R5 MPCore up to 600MHz, FPGA fabric with 1,143K logic cells, and Arm Mali-400 MP2 GPU (lower-end ZCU17EG and ZCU11EG MPSoC are also available) System Memory 4GB DDR4 RAM for PS 4GB Dual DDR4 RAM for PL Storage – 8GB eMMC Flash (for boot code) Transceivers PS-GTR Transceivers x 4 @ 6Gbps PL-GTH Transceivers x 32 @ 16.3Gbps PL-GTY Transceivers x 16 […]

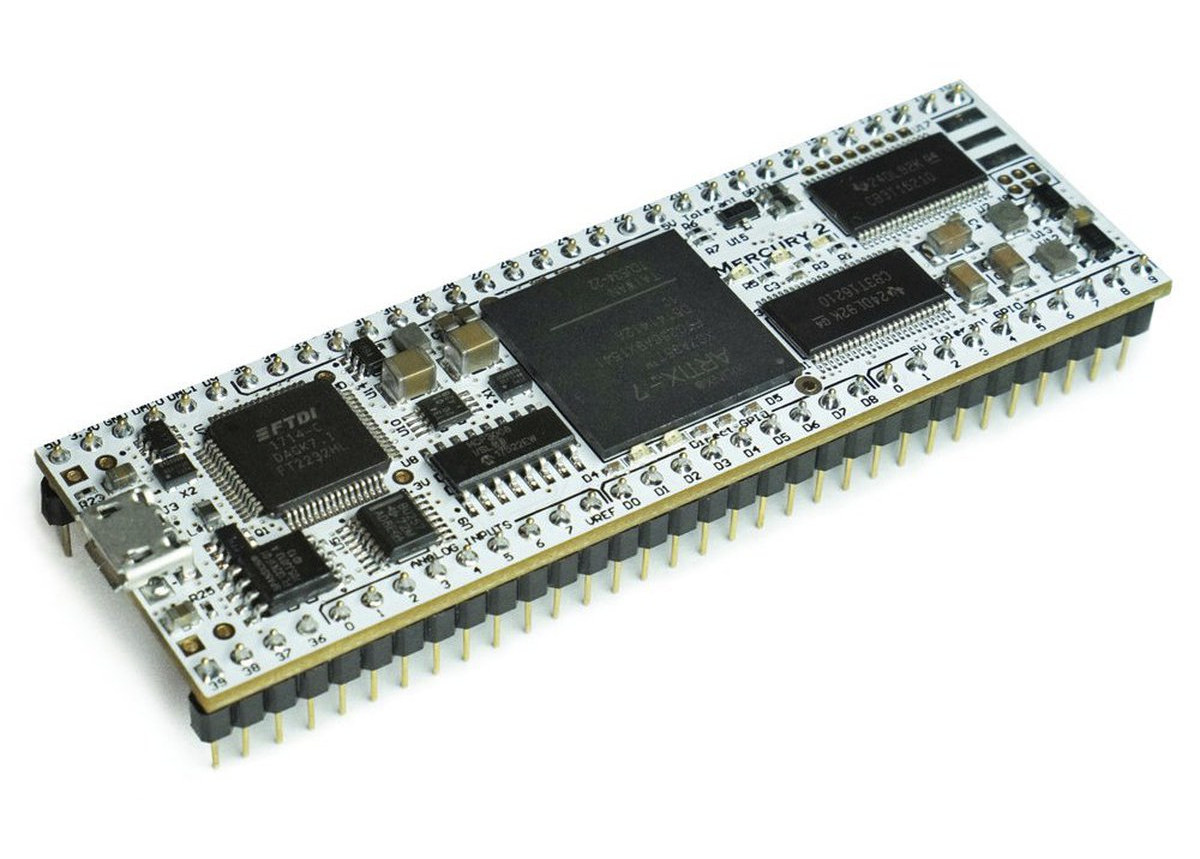

FPGA Meets Breadboard with Mercury 2 Xilinx Artix-7 FPGA Development Board

While we now come across more and more FPGA development boards, very few are designed to be inserted into a breadboard. We’ve previously covered TinyFPGA BX, Fipsy, and QuickFeather FPGA breadboard-friendly boards. All those boards are however based on entry-level FPGAs like Lattice Semi ICE40 or QuickLogic EOS S3, and if you’d like a more powerful FPGA board that fits into a breadboard, MicroNova Mercury 2 development board may meet your requirements with a Xilinx Artix-7 FPGA. MicroNova Mercury 2 specifications: FPGA – Xilinx Artix-7A FPGA (XC7A35T) with 33,280 logic cells or XC7A100T with 101,440 logic cells System Memory – 4 Mbit (512K x 8-bit) asynchronous SRAM Storage – 32 Mbit SPI flash for configuration & user data Networking – On-board Microchip LAN8720A 10/100M Ethernet PHY USB – Dual-channel high-speed USB 2.0 micro USB port (ch A for config, ch B for user) 2x 32-pin headers Fast Ethernet signals 8-channel, […]

MYIR launches FZ5 EdgeBoard AI Box for AI on the Edge

Back in July of this year (2020), MYRI technology announced the MYIR’s FZ3 deep learning accelerator card powered by the Xilinx Zynq UltraScale+ ZU3EG Arm FPGA MPSoC and it is capable of delivering up to 1.2TOPS computing power. With only a few months since that launch, MYRI technology is now announcing another two related sets of products – FZ5 EdgeBoard AI Box and the FZ5 Card. The FZ5 EdgeBoard AI Box is an AI-focused computing platform that is based on the FZ5 AI Accelerator card which is an upgrade of the FZ3 card. The FZ5 looks more like a single board computer than an actual computing card. The FZ5 accelerator is powered by the Xilinx Zynq UltraScale+ ZU5EV MPSoC which features a 1.5 GHz quad-core Arm Cortex-A53 64-bit application processor, a 600MHz dual-core real-time Arm Cortex-R5 processor, a Mali400 embedded GPU and is capable of delivering up to 2.4 TFLOPS as compared […]

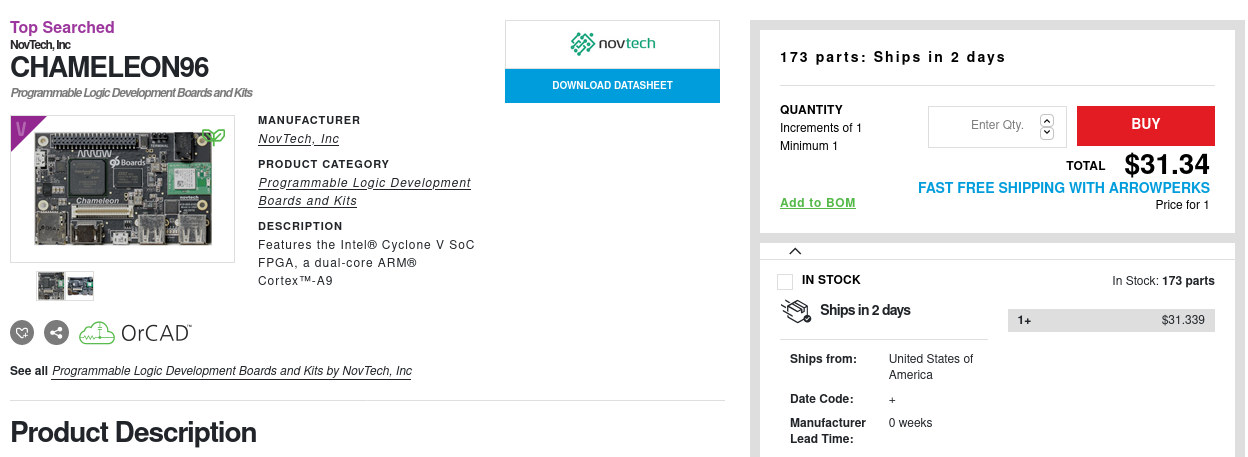

Arrow Chameleon96 Arm + Cyclone V FPGA Board Sold for $32 (Promo)

First introduced in 2017, Arrow Chameleon96 96Boards SBC comes with an Intel / Altera Cyclone V SE SoC featuring a dual-core Arm Cortex A9 processor clocked at up to 800 MHz and FPGA fabric with 110K Logic Elements. It used to sell for $129, but Arrow & appears to have a promotion now where the Novtech board sells for just $31.34 with free shipping[Update: all available boards are gone, and the product is now out of stock]. It looks like a good opportunity for people interested in playing around with an Arm Linux FPGA platform. Here’s a reminder of Chameleon96 board specifications which the company shamelessly copied from CNX Software: SoC – Intel PSG / Altera Cyclone V SE 5CSEBA6U19I7N with a dual-core ARM Cortex A9 processor @ up to 800 MHz and FPGA fabric with 110K Logic Elements Chips, Ports, and Features connected to FPGA: Integrated USB-Blaster II JTAG […]

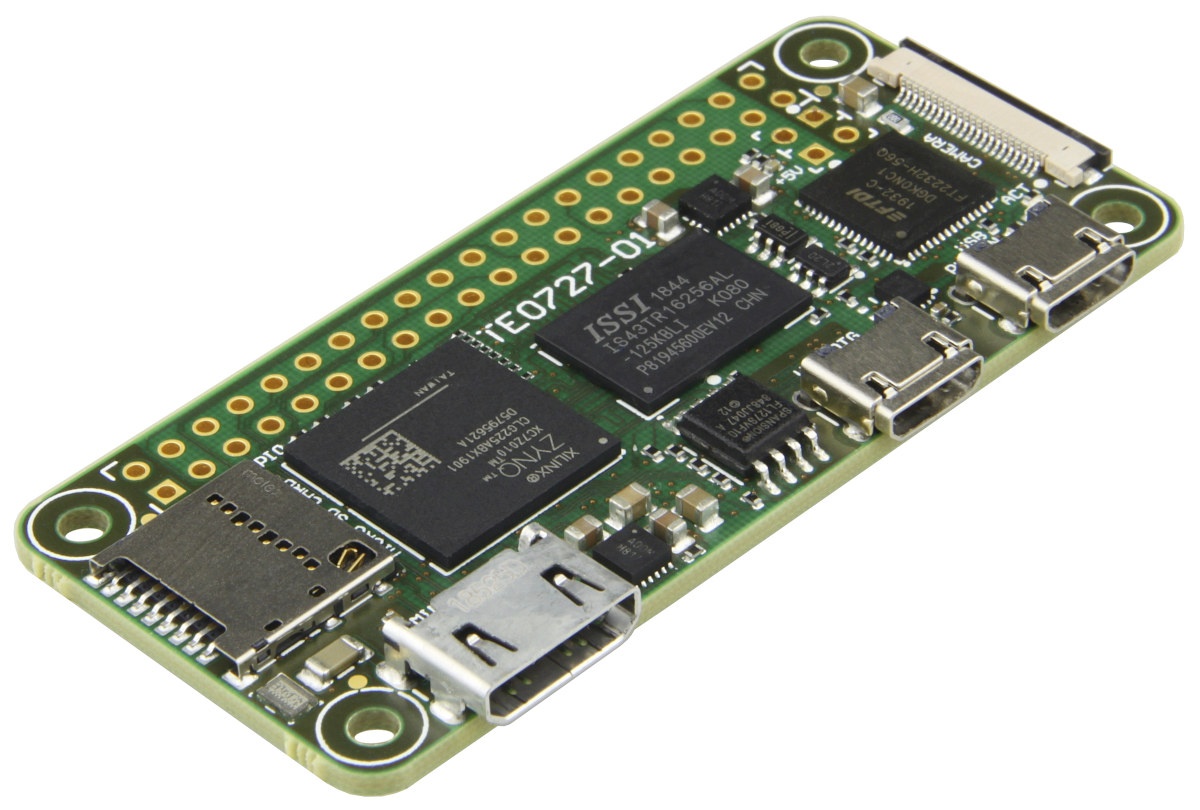

ZynqBerryZero Brings Xilinx Zynq-7010 FPGA SoC to Raspberry Pi Zero Form Factor

Trenz Electronic introduced ZynqBerry in 2017 as a Xilinx Zynq FPGA board following Raspberry Pi 2/3 Model B form factor, and the company has now just launched another Raspberry Pi inspired FPGA board with ZynqBerryZero following Raspberry Pi Zero form factor. ZynqberryZero is equipped with a Xilinx Zynq-7000 series FPGA & Arm Cortex-A9 SoC combined with 512 MB RAM and 16MB flash, and offers all Raspberry Pi Zero ports namely a 40-pin GPIO header, two micro USB ports, a mini HDMI connector, a CSI connector, and micro SD card slot. ZynqBerryZero specifications: SoC – Xilinx Zynq XC7Z010-1CLG225C with dual-core Cortex-A9 clocked up to 667 MHz, FPGA fabric with 28K logic cells, 2.1Mbit block RAM, and 80x DSP slices System Memory – 512 MB DDR3L SDRAM Storage – 16 MB Flash memory, MicroSD card slot Video Output – Mini HDMI connector, type C Camera – CSI-2 connector USB – 1x Micro […]

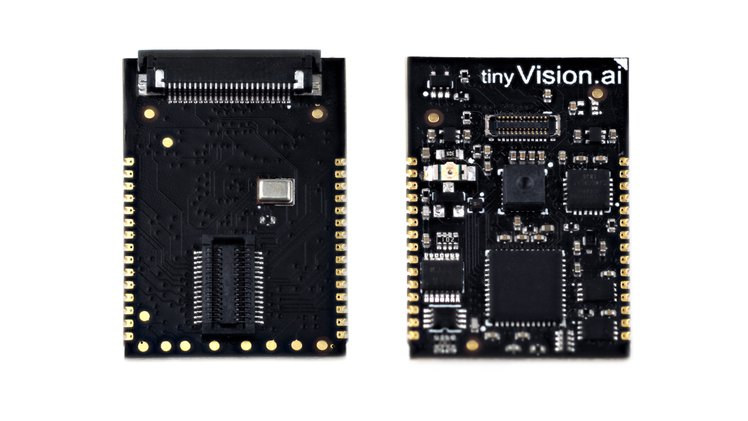

Vision FPGA SoM Integrates Audio, Vision and Motion-Sensing with Lattice iCE40 FPGA (Crowdfunding)

tinyVision.ai’s Vision FPGA SoM is a tiny Lattice iCE40 powered FPGA module with integrated vision, audio, and motion-sensing capability with a CMOS image sensor, an I2S MEMS microphone and a 6-axis accelerometer & gyroscope. The module enables low power vision (10-20 mW) for battery-powered applications, can interface via SPI to a host processor as a storage device, comes with open-source toolchain and sample code, and is optimized for volume production. Vision FPGA SoM specifications: FPGA – Lattice iCE40UP5k FPGA with 5K LUT’s, 1 Mb RAM, 8 MAC units Memory – 64 Mbit QSPI SRAM for temporary data Storage – 4 Mbit QSPI Flash for FPGA bitstream/code storage Sensors Himax HM01B0 CMOS image sensor Knowles MEMS I2S microphone, expandable to a stereo configuration with an off-board I2S microphone InvenSense IMU 60289 6-axis Gyro/accelerometer I/Os 4x GPIOs with programmable IO voltage SPI host interface with programmable IO voltage Misc – Tri-color LED, […]

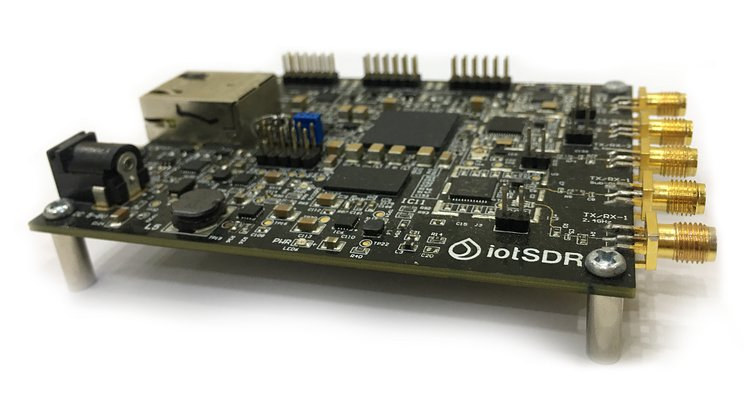

IoTSDR Linux Board Targets the Development of IoT Gateways with Standard or Custom IoT Protocols (Crowdfunding)

Xilinx Zynq-7010/-7020 powered iotSDR board by EmbedINN enables the development of IoT gateways with support for LoRa, SigFox, WeightLess, Bluetooth, BLE, 802.15.4, ZigBee, as well as custom IoT protocols. The board also supports GPS, Galileo, Beidou, and GLONASS navigation systems thanks to a Maxim Integrated MAX2769 GNSS chip. iotSDR key hardware features and specifications: SoC (one or the other) Xilinx Zynq-Z7010 (XC7Z010-1CLG400C) dual-core Arm Cortex-A9 processor with 256 kb on-chip memory, FPGA fabric with 28,000 logic cells, 17,600 LUTs, 2.1 Mb block RAM, 80 DSP slices Xilinx Zynq-Z7020 (XC7Z020-1CLG400C) dual-core ARM Cortex-A9 processor with 256 kb on-chip memory, FPGA fabric with 85,000 logic cells, 53,200 LUTs, 4.9 Mb block RAM, 220 DSP slices System Memory – 512 MB DDR3 Storage 128 Mbit QSPI flash memory for firmware Microchip AT24MAC602 SPI EEPROM for RF transceiver MCU firmware and data Radios “IoT” Radios RF Transceivers – 2x Microchip/Atmel AT86RF215 European band – […]

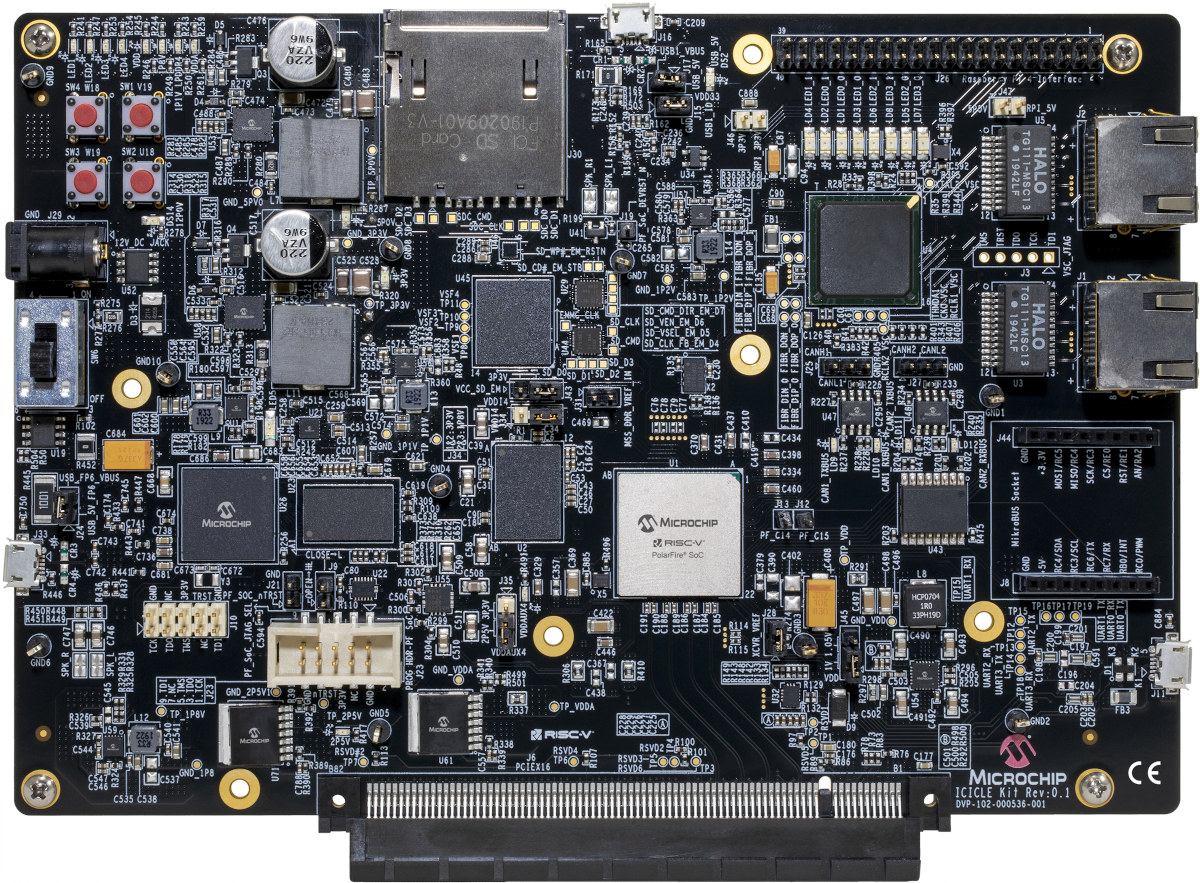

PolarFire SoC Icicle 64-bit RISC-V and FPGA Development Board Runs Linux or FreeBSD (Crowdfunding)

We got some more details about PolarFire RISC-V FPGA SoC late last year, and we were promised a Linux capable 64-bit RISC-V & FPGA development board with PolarFire SoC Icicle kit in Q3 of 2020. We are already in July 2020. So where is the board? Oh, look! It’s right here on Crowd Supply where it is offered for $499, and shipping is expected to start in mid-September. PolarFire SoC Icicle specifications: SoC FPGA – PolarFire SoC MPFS250T-FCVG484EES penta–core RISC-V CPU subsystem (1xRV64IMAC, 4xRV64GC) with 254K LE non-volatile fabric, 784 18 × 18 math blocks, secure boot, 4x 12.7 Gbps SERDES, FCVG484 package (19 × 19 mm, 0.8 mm pitch) System Memory – 2GB LPDDR4 x32 Storage – 1 GBit QSPI Flash, 8GB eMMC Flash or SD card slot (multiplexed) Video Output – HDMI 2.0 (removed from final board) Connectivity – 2x Gigabit Ethernet, Wi-Fi, and Bluetooth USB – 1x […]