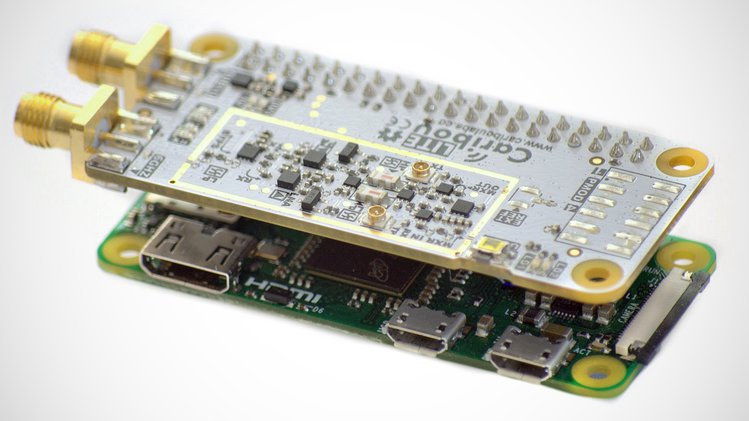

CaribouLite RPi HAT is an open-source dual-channel software-defined radio (SDR) Raspberry Pi HAT – or rather uHAT – that works in the sub-GHz ISM range and optionally the 30 MHz – 6 GHz range for the full version. Developed by Israel-based CaribouLabs, the micro HAT is equipped with a Lattice Semi ICE40LP1K FPGA, a Microchip AT86RF215 RF transceiver, two SMA antenna connectors, a Pmod expansion connector, and designed for any Raspberry Pi board with a 40-pin GPIO header. CaribouLite RPi HAT specifications: FPGA – Lattice Semi ICE40LP with 1.28 kLE RF Chipset – Microchip AT86RF215 Sub-GHz / 2.4GHz transceiver Qorvo’s RFFC5072 integrated Mixer IC (for full version only) Tuning Range CH1 Full version – 30 MHz – 6 GHz ISM version – 2.4 – 2.4835 GHz CH2 – Sub-1GHz Max Sampling Rate – 4 MSPS ADC/DAC Resolution – 13-bit Max RF Bandwidth – 2.5 MHz Transmit Power – up to […]

Renesas introduces sub 50 cents FPGA family with free Yosys-based development tools

Renesas has just unveiled the ForgeFPGA family of low-cost low-power FPGA’s to go for under 50 cents in (large) volumes following their acquisition of Dialog Semiconductors last August, who previously designed the GreenPAK programmable mixed-signal matrix. The company says its FPGAs consume half the power of competing FPGAs with a standby current of under 20uA, the price point will enable the use of FPGA in new markets and IoT products, and the tools will be free, at least as in beer, without any license to acquire or install. The full specifications are not available yet, but the ForgeFPGA Family will come with a maximum of 5,000 gates of logic, and the first devices ship with 1K and 2K Look Up Tables (LUTs), and as just mentioned, will operate at ultra-low power as low as 20 microamps in standby. ForgeFPGA is expected to target the same market as GreenPAK notably embedded […]

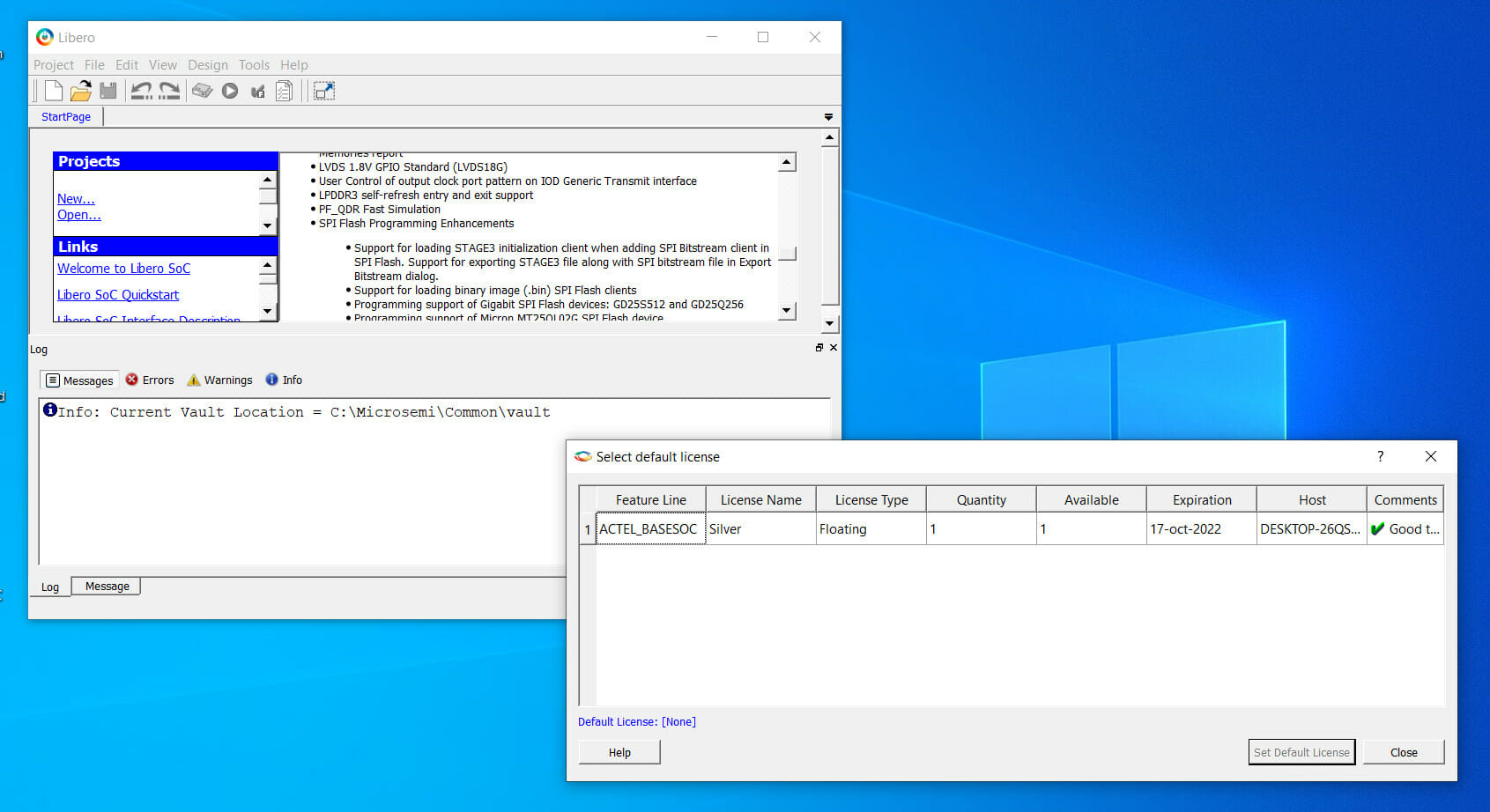

My experience installing Libero SoC in Ubuntu and Windows 10

A few weeks ago, I received Microchip PolarFire SoC FPGA Icicle Kit with FPGA fabric and hard RISC-V cores capable of handling Linux. I wrote “Getting Started with Yocto Linux BSP” tutorial for the board, and I had initially titled the current post “Getting Started with FPGA development using Libero SoC and Polarfire FPGA SoC”. I assumed I would write one or two paragraphs about the installation process, and then show how to work with Libero SoC Design Suite to create an FPGA bitstream. But instead, I spent countless hours trying to install the development tools. So I’ll report my experience to let readers avoid some of the pitfalls, and hopefully save time. (Failing to) Install Libero SoC v2021.v2 on Ubuntu 20.04 If we go to the download page, we’ll see Libero SoC v2021.2 for Windows and Libero SoC v2021.2 for Linux. Since my computer is running Ubuntu 20.04, I decided […]

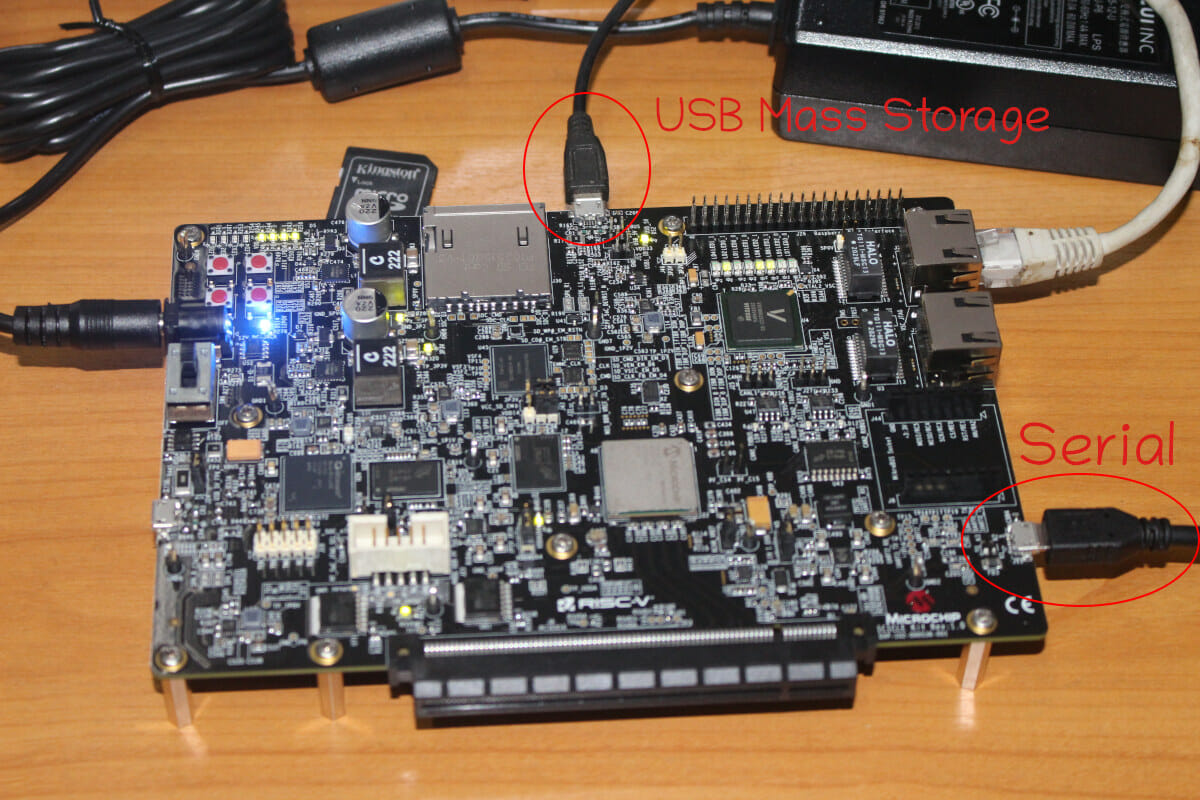

Getting Started with the Yocto Linux BSP for Polarfire SoC FPGA Icicle Kit

Last month I received Microchip PolarFire SoC FPGA Icicle development kit that features PolarFire SoC FPGA with a Penta–core 64-bit RISC-V CPU subsystem and an FPGA with 254K LE, and booted it into the pre-installed Linux operating systems based on OpenEmbedded. Today, I’ll show how to get started with the Yocto BSP and run the EEMBC CoreMark benchmark, and I’ll check out the FPGA with Libero SoC Design Suite in a couple of weeks. Operating Systems supported by PolarFire SoC FPGA My initial idea was to focus this part of the review on Linux on RISC-V status, checking some system information, running some benchmarks (e.g. SBC-Bench), compiling the Linux kernel, and installing services like a LEMP stack (Linux, Nginx (pronounced Engine-X), MySQL, PHP) which could be used for WordPress hosting for instance. But then I looked at the operating systems supported with Microchip PolarFire SoC FPGA. There’s a Yocto Linux […]

UP Xtreme i11 Edge Compute Enabling Kit supports 5G, WiFi 6, Myriad X AI accelerator cards

UP! Bridge the Gap, a brand belonging to AAEON Technology, has started taking pre-orders for the UP Xtreme i11 Edge Compute Enabling Kit, a mini PC based on the UP Xtreme i11 Edge Tiger Lake SBC that was first introduced last year, and formally launched last month. The mini PC is offered with Celeron 6305E up to Intel Core i7-1185GRE processor, optional DDR4 and SSD, M.2 sockets for 5G, WiFi 6, or an AI accelerator card based on Movidius Myriad X VPU., serial ports, as well as a Phoenix terminal connector to access some of the GPIOs. UP Xtreme i11 Edge Compute Enabling Kit specifications: Tiger Lake “E”/”GRE” SoC (one or the other) Intel Core i7-1185G7GRE quad-core/8-thread processor @ up to 4.4 GHz with 96 EU Intel Iris Xe Graphics; up to 28W TDP (cTDP 15W) Intel Core i5-1145G7GRE quad-core/8-thread processor @ up to 4.1 GHz with 80 EU Intel […]

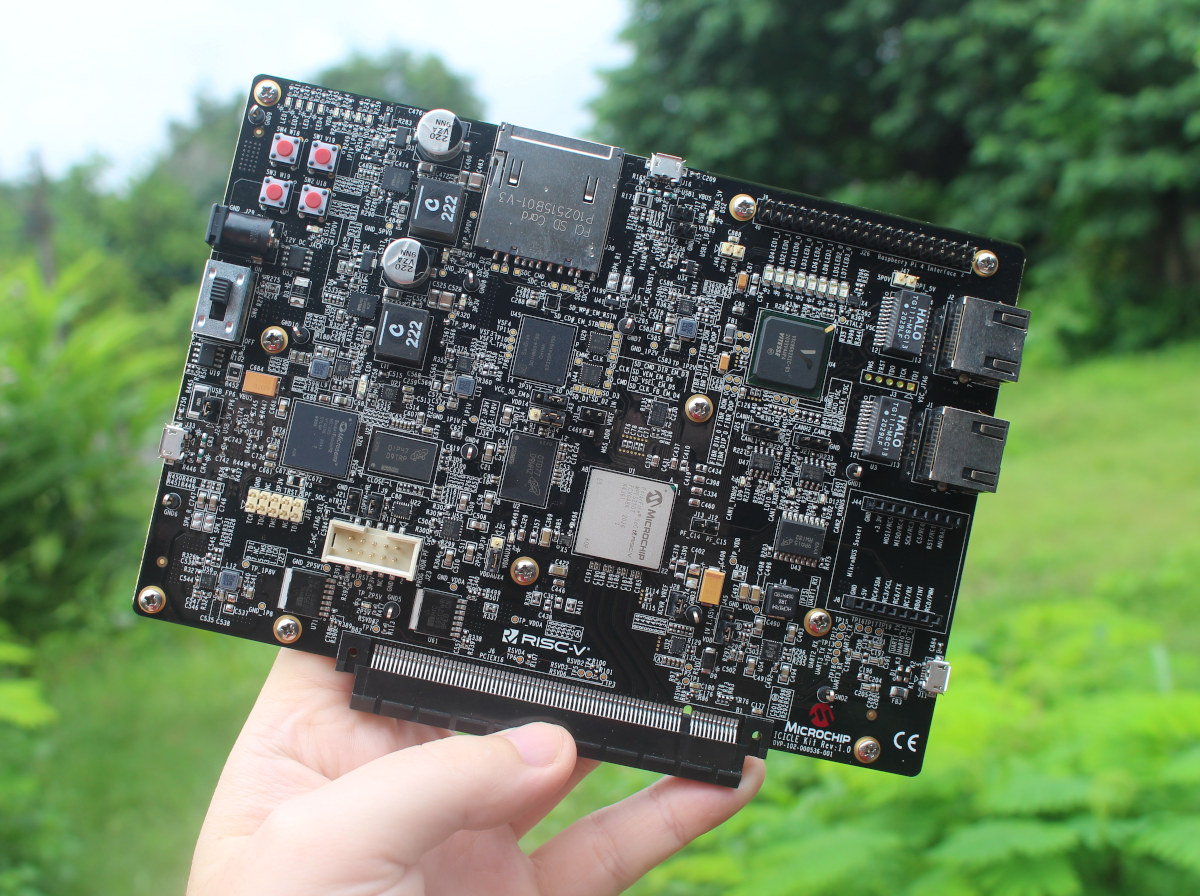

A first look at Microchip PolarFire SoC FPGA Icicle RISC-V development board

Formally launched on Crowd Supply a little over a year ago, Microchip PolarFire SoC FPGA Icicle (codenamed MPFS-ICICLE-KIT-ES) was one of the first Linux & FreeBSD capable RISC-V development boards. The system is equipped with PolarFire SoC FPGA comprised a RISC-V CPU subsystem with four 64-bit RISC-V (RV64GC) application cores, one 64-bit RISC-V real-time core (RV64IMAC), as well as FPGA fabric. Backers of the board have been able to play with it for several months ago, but Microchip is now sending the board to more people for evaluation/review, and I got one of my own to experiment with. That’s good to have a higher-end development board instead of the usual hobbyist-grade board. Today, I’ll just have a look at the kit content and main components on the board before playing with Linux and FPGA development tools in an upcoming or two posts. Microchip PolarFire SoC FPGA Icicle Unboxing The board […]

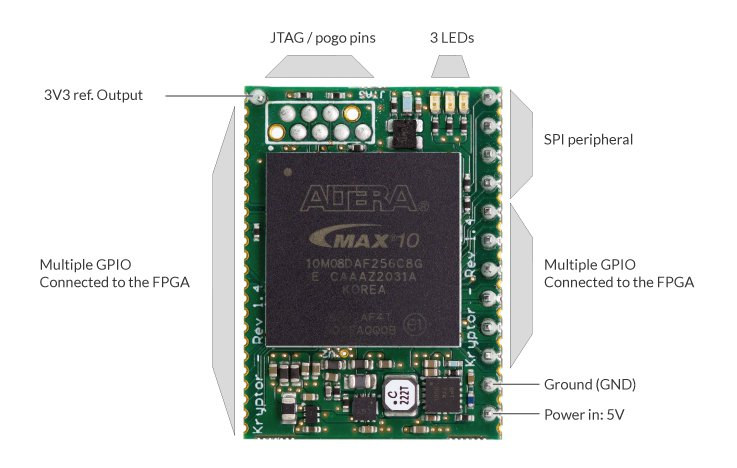

Kryptor FPGA – Tiny MAX10 FPGA board works as a hardware security module (Crowdfunding)

Kryptor FPGA, sometimes just called Kryptor, is a compact Intel/Altera MAX10 FPGA development board mostly designed for encryption, and acting as a dedicated Hardware Security Module (HSM) with a custom soft-core from Skudo OÜ. But obviously, you could also use the FPGA board for other purposes. Hardware encryption can be quite more secure than software-based encryption with reduced attack surfaces, especially since data processing can be done in the FPGA RAM. The HSM can be used to encrypt files, videos, emails, IoT messages, etc… from various hardware platforms including Arduino and Raspberry Pi boards. Contrary to closed-sourced commercial solutions, the soft-core is open-source and as such can be verified by third parties to make sure there aren’t any backdoors or security flaws. Kryptor FPGA specifications: FPGA – Intel/Altera MAX10 8K LE ( 10M08DAF256C8G) FPGA @ 100 MHz with 8000 logic elements (LE), 1376 Kb flash, 378 Kb total RAM, up […]

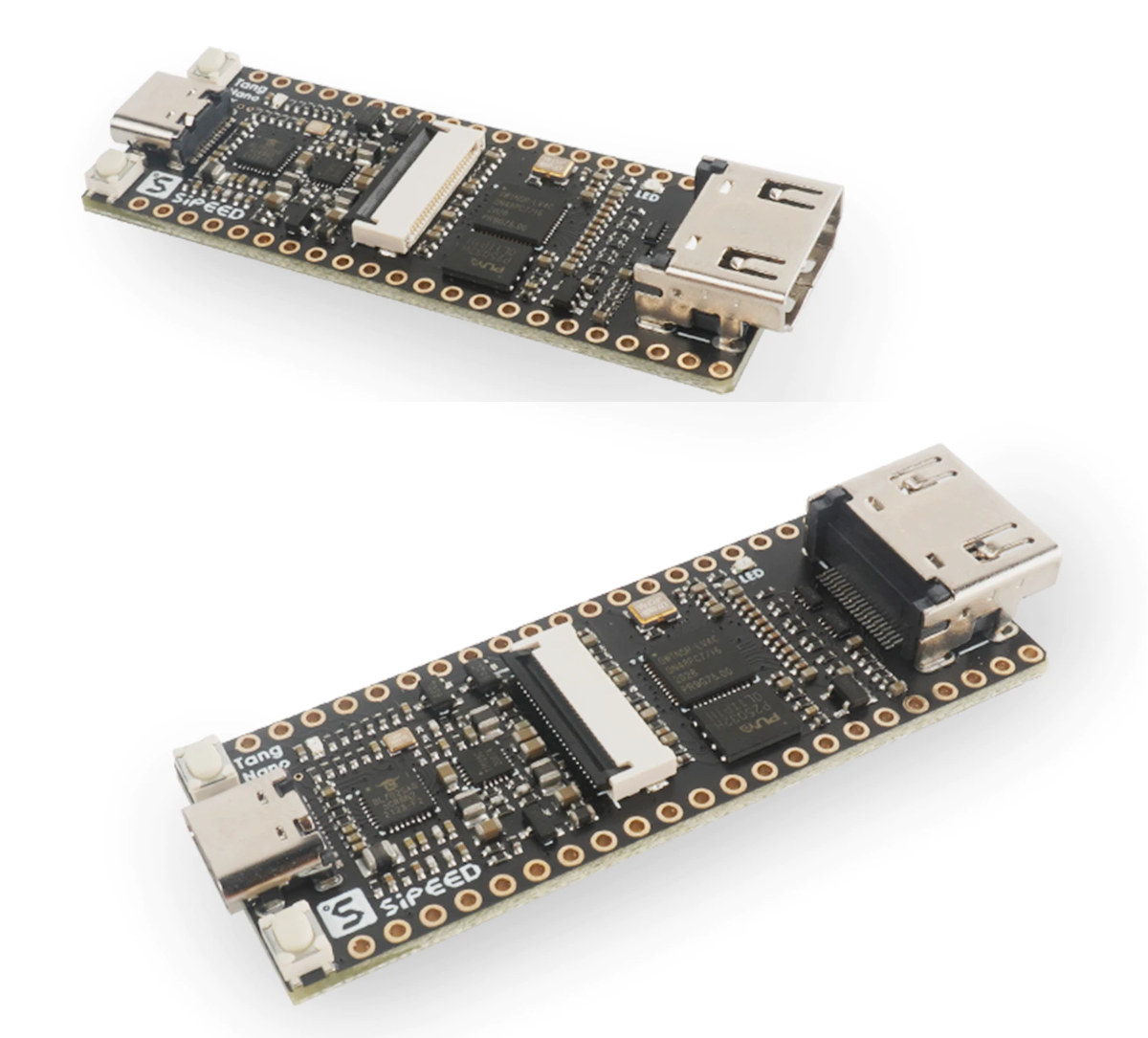

$18 Tang Nano 4K FPGA board comes with HDMI output, optional camera

Sipeed’s Tang Nano 4K FPGA board is an upgrade to the company’s Tang Nano FPGA board with a more powerful GOWIN GW1NSR-LV4C FPGA with 4608 LUT (instead of 1152) and a Cortex-M3 microcontroller embedded into the chip. Like the previous board, the new Tang Nano 4K features a USB-C port for power and downloading the bitstream, but replace the RGB LCD interface with an HDMI port, and adds support for an optional OV2640 camera. Tang Nano 4K board specifications: FPGA – GOWIN GW1NSR-LV4C aka GW1NSR-4C (See PDF datasheet for details) with 4608 logical units (LUTs) 3456 registers 16 multiplier parameters 180Kbit block SRAM, 64Mbit PSRAM 2x PLL Up to 44x user I/O Arm Cortex-M3 hard processor Storage – 32 Mbit NOR flash Video Output – HDMI port Camera I/F – DVP camera connector for OV2640 camera sensor up to 1600 x 1200 (UXGA) resolution USB – USB Type-C port for […]