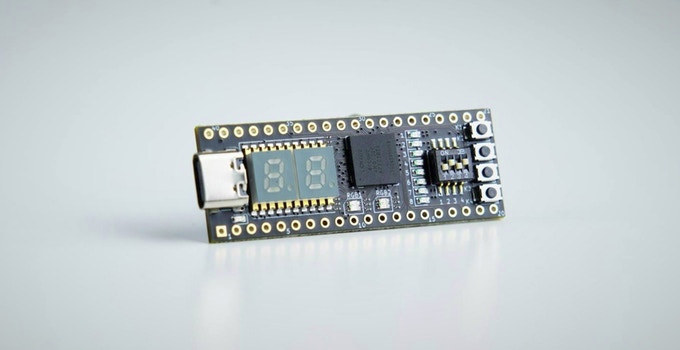

STEPFPGA MXO2Core miniature FPGA development board is based on Lattice MXO2-4000 FPGA, and designed for education with an easy-to-use Web IDE, instead of the more traditional tools that can be frustrating to use, and detailed tutorials. The board also comes with a 2-digit segment display, some LEDs, push buttons, and a 4-way DIP switch, as well as two rows of twenty pins for I/O expansion, and a USB Type-C port used for power, programming, or mass storage. STEPFPGA MXO2Core specifications: FPGA – Lattice Semi MachXO2 X02-4000 FPGA with 4320 LUTs Display – 2-digit segment display USB – 1x USB Type-C port for power, programming (UART), and mass storage Expansion – 2x 20-pin headers with up to 36x GPIOs, SPI, I2C, 3.3V, VBUS, GND; breadboard-compatible Misc – 2x RGB LEDs, 8x red LEDs, 4-way DIP switch, 4x push buttons Power Supply – 5V via a USB port Dimensions – Small four-layer […]

MNT Pocket Reform 7-inch modular mini laptop takes a range of Arm (and FPGA) modules

MNT Pocket Reform is an open-source hardware mini laptop with a 7-inch Full HD display, an ortholinear mechanical keyboard, and trackball, that follows the path of its older and bigger sibling: the MNT Reform 2 laptop initially launched with an NXP i.MX 8M quad-core Arm Cortex-A53 module. The new laptop will not only support a similar “NXP i.MX 8M Plus” module but also a range of other Arm modules namely an NXP Layerscape LS1028A module with up to 16GB RAM, the Raspberry Pi CM4 module via an adapter, Pine64 SOQuartz (RK3566, up to 8GB RAM), as well as based on AMD Xilinx Kintex-7 FPGA for industrial use. MNT Pocket Reform specifications: Available system-on-modules Standard: NXP i.MX 8M Plus quad-core Arm Cortex-A53 @ 1.8GHz with 4 or 8 GB DDR4, Vivante GC7000UL GPU, 2.3 TOPS NPU NXP Layerscape LS1028A dual-core Arm Cortex-A72 with 8 or 16GB DDR4, Vivante GC7000UL GPU Raspberry […]

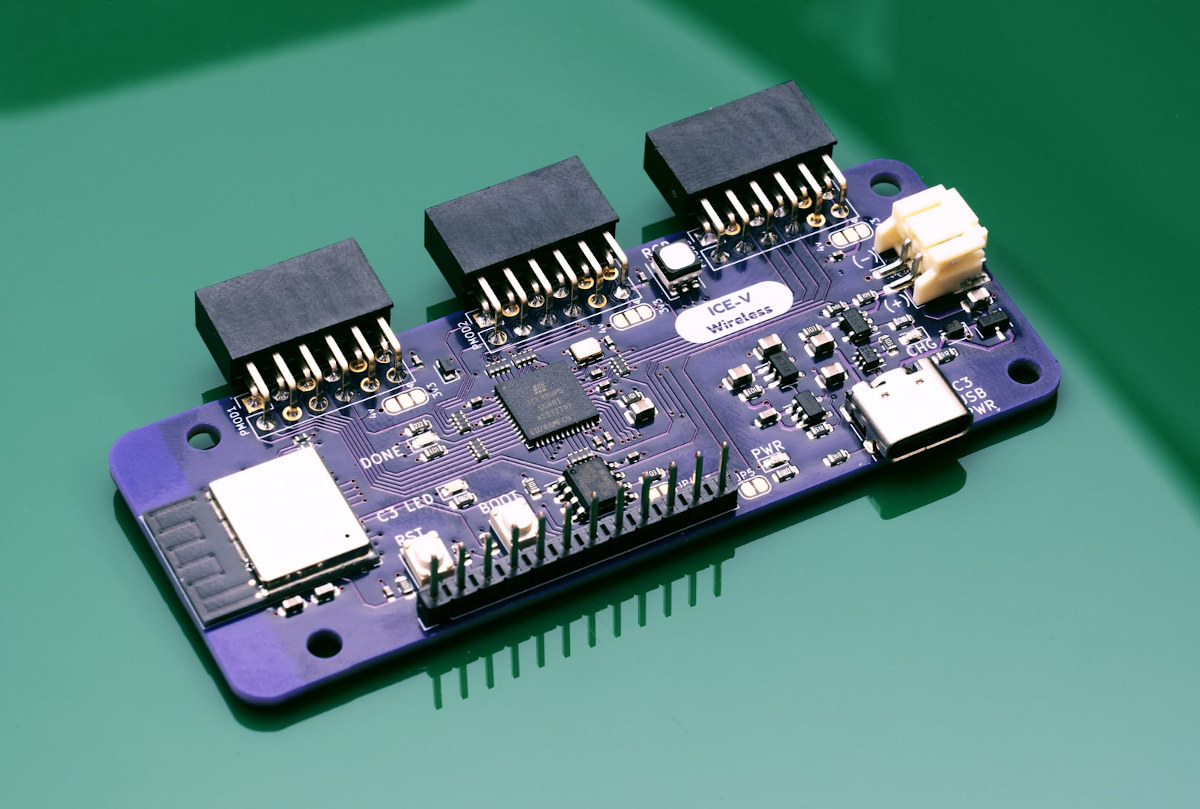

ICE-V Wireless FPGA board combines Lattice Semi iCE40 UltraPlus with WiFi & BLE module

Lattice Semi ICE40 boards are pretty popular notably thanks to the availability of open-source tools. ICE-V Wireless is another ICE40 UltraPlus FPGA board that also adds wireless support through an ESP32-C3-MINI-1 module with WiFi 4 and Bluetooth LE connectivity. Designed by QWERTY Embedded Design, the board also comes with 8MB PSRAM, offers three PMOD expansion connectors, plus a header for GPIOs, and supports power from USB or a LiPo battery (charging circuit included). ICE-V Wireless specifications: FPGA – Lattice Semi ICE40UP5K-SG48 FPGA with 5280 LUTs, 120 Kbits EBR RAM, 1024 Kbits PSRAM External RAM – 8MB PSRAM Wireless – ESP32-C3-MINI-1 module with 2.4 GHz WiFi 4 and Bluetooth LE through ESP32-C3 RISC-V processor, 4MB flash. USB – 1x USB Type-C port for power, programming, and JTAG debugging of the ESP32-C3 module Expansions 3x PMOD connectors connected to the FPGA I/O connector with 7x ESP32-C3 GPIO lines (serial, ADC, I2C) and […]

Open-source hardware USB Type-C industrial camera features Lattice Crosslink NX FPGA

Gaurav Singh, acting as Circuit Valley, has designed an open-source hardware USB 3.0 Type-C industrial camera with three boards: one to capture data through a CMOS sensor, another based on a Lattice Crosslink NX FPGA to handle image processing, and finally, a board equipped with an Infineon FX3 USB 3.0 controller for sending the video data to the host. This design allows the DIY camera to be extremely flexible, as for instance, you could keep the FPGA and USB board, and simply change the sensor board for a better/different camera. A 3D printable enclosure is also provided, and the camera supports C-mount lenses, so the lens can also be easily changed as required. Here’s what the final result looks like. Camera specifications: Sensor board Sensor for example Sony IMX290, IMX327, or IMX462 Oscillator FPGA/Host board interface – High-density connector with I2C, 4-lane MIPI with clock, I2C, a few other control […]

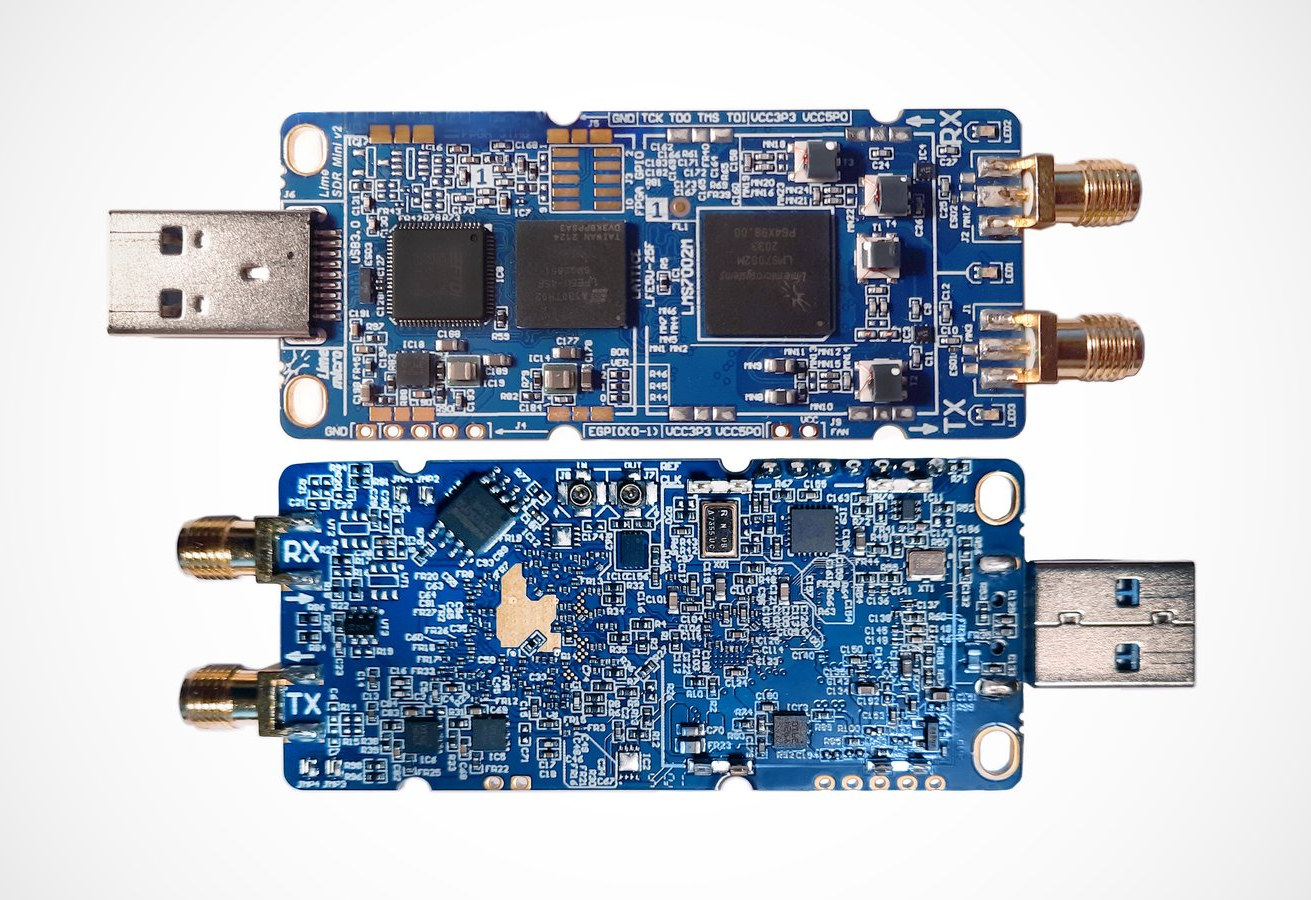

LimeSDR Mini 2.0 USB SDR board gets an upgrade to Lattice Semi ECP5 FPGA (Crowdfunding)

The LimeSDR Mini is an open-source hardware full-duplex USB SDR board based on Intel Altera Max 10 Altera FGPA that was introduced in 2017 on Crowd Supply and raised close to $2 million US dollars. Since it has been used in various projects including digital TV transmitters. Lime Microsystems is now back on Crowd Supply with the similar-looking LimeSDR Mini 2.0 replacing the MAX 10 FPGA with 16K logic gates with a more powerful and capable Lattice Semiconductor ECP5 FPGA with 44K logic gates while keeping the company’s LMS7002 RF transceiver. LimeSDR Mini 2 specifications: FPGA – Lattice Semi ECP5 (LFE5U-45F) with 44K logic gates, 108 sysMEM blocks (18kb), 1,944 Kb embedded memory, 351 Kb distributed RAM bits Storage – 4 MB flash memory for data; 2x128KB EEPROM for RF transceiver MCU firmware and data RF Lime Microsystems LMS7002M RF transceiver Tx & Rx SMA connectors Frequency range – 10 […]

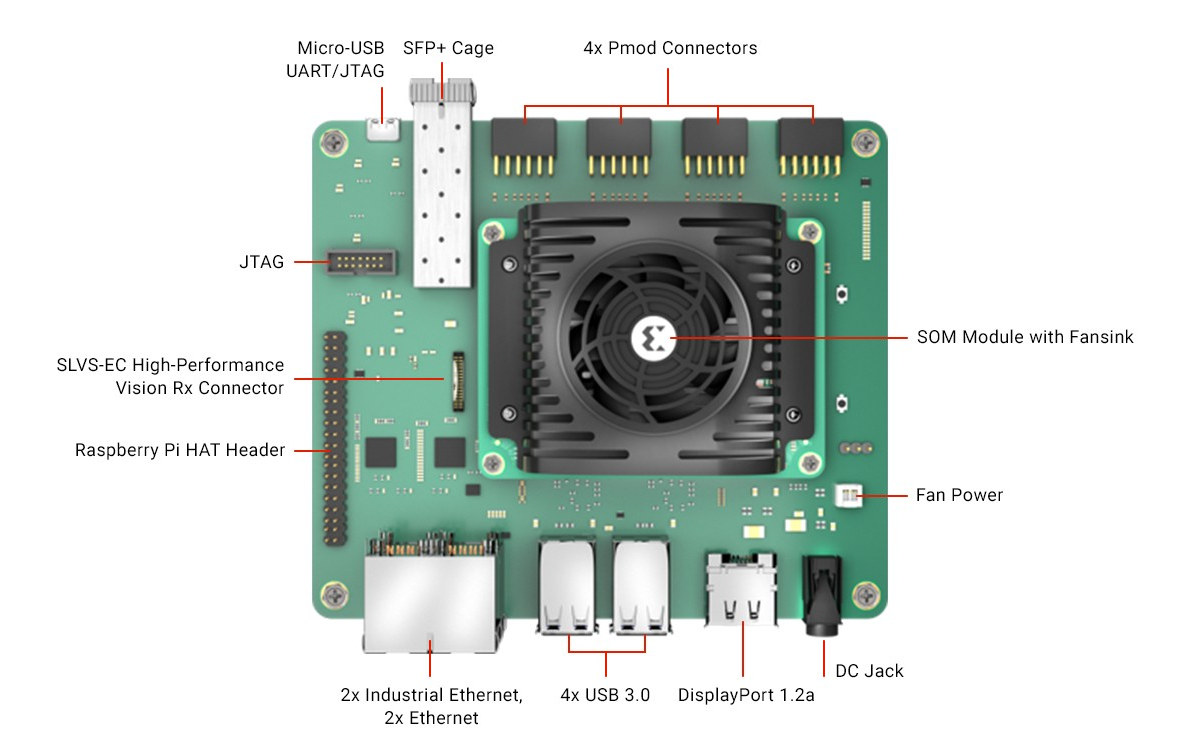

$349 AMD Kria KR260 Robotics Starter Kit takes on NVIDIA Jetson AGX Xavier devkit

AMD Xilinx Kria KR260 Robotics Starter Kit features the Kria K26 Zynq UltraScale+ XCK26 FPGA MPSoC system-on-module (SoM) introduced last year together with the Kria KV260 Vision AI Starter Kit. Designed as a development platform for robotics and industrial applications, the KR260 is said to deliver nearly 5x productivity gain, up to 8x better performance per watt and 3.5x lower latency compared to Nvidia Jetson AGX Xavier or Jetson Nano kits. We’ll have a better look at the details below. Kria KR260 Robotics Starter Kit specifications: SoM – Kria K26 module with: MPSoC – Xilinx Zynq Ultrascale+ custom-built XCK26 with quad-core Arm Cortex-A53 processor up to 1.5GHz, dual-core Arm Cortex-R5F real-time processor up to 600MHz, Mali-400 MP2 GPU up to 667MHz, 4Kp60 VPU, 26.6Mb On-Chip SRAM, 256K logic cells, 1,248 DSP slices, 144 Block RAM blocks, 64 UltraRAM blocks System Memory – 4GB 64-bit DDR4 (non-ECC) Storage – 512 Mbit […]

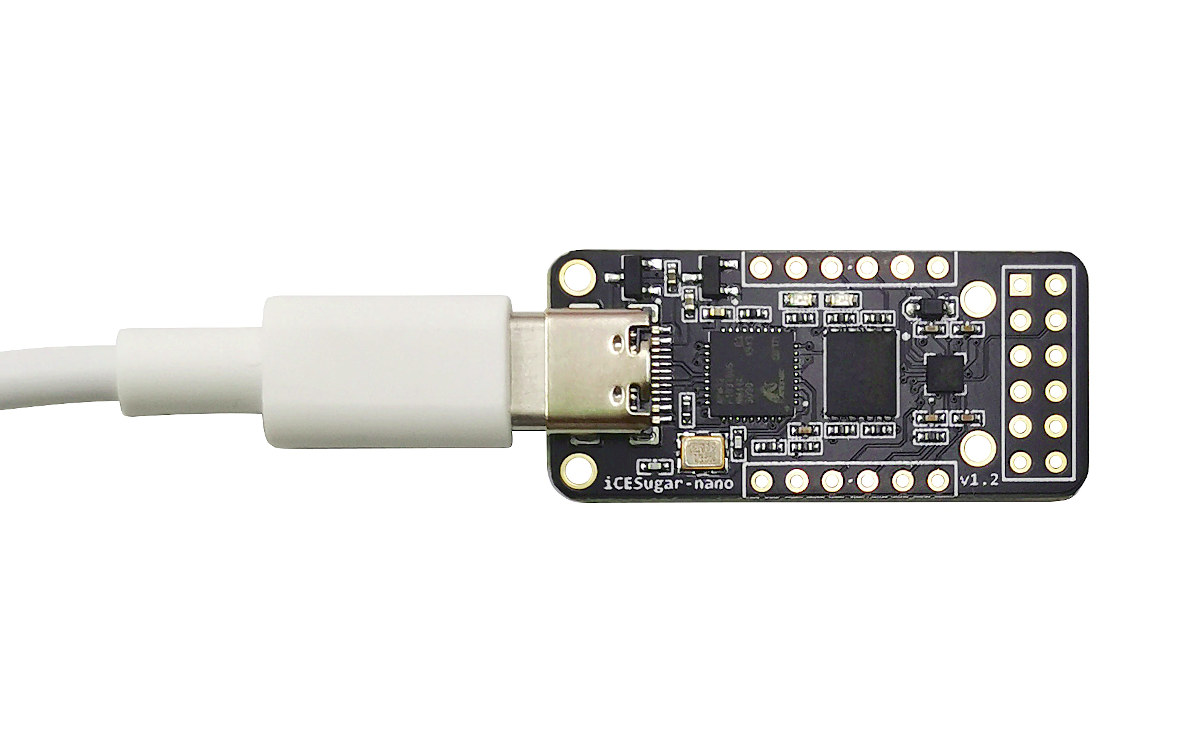

iCESugar-nano is a $19 iCE40LP1k FPGA board with 3x PMOD connectors

Muse Lab’s iCESugar-nano is a tiny FPGA board based on Lattice Semi iCE40LP1K-CM36 programmable via its USB-C port through on-board iCELink debugger, and exposing I/Os for three standard PMOD connectors. The board is fully supported by Yosys open-source toolchain ( Yosys+ nextpnr + IceStorm), and the onboard debugger supports drag-and-drop programming so that you can just drag the FPGA bitstream into the virtual disk to program it through a USB Type-C cable. iCESugar-nano specifications: FPGA – Lattice Semi iCE40LP1k FPGA with 1280 LUT/8KB SRAM/PLL Storage – 2MB SPI flash (W25Q16) USB – 1x USB Type-C port for power and programming Expansion – 14x usable IOs with 1x 12-pin PMOD connectors and 2x 6-pin PMOD connectors Debugging – On-board iCELink debugger based on Arm Mbed DAPLink Misc – Adjustable clock (8/12/36/72MHz), LED Power Supply – 5V via USB-C port Dimensions – 3.9 x 1.8 cm Documentation, schematic PDF, links to tools, […]

ZUBoard 1CG – A low-cost AMD Xilinx Zynq UltraScale+ ZU1CG MPSoC FPGA development board

Avnet ZUBoard 1CG is a development board featuring the new entry-level AMD Xilinx Zynq UltraScale+ ZU1CG dual-core Cortex-A53 MPSoC with 81K FPGA system logic cells, equipped with 1GB LPDDR4 RAM, as well as SYZYGY connectors and mikroBus expansion for Click boards. Priced at $159, the board may offer a good opportunity to get started with Zynq UltraScale+ MPSoC, as it’s quite cheaper than boards based on ZU3 devices such as Ultra96-V2 or MYD-CZU3EG. Avnet says the board is suitable for artificial intelligence, machine learning, embedded vision, embedded processing, and robotics applications. ZUBoard 1CG specifications: SoC – AMD/Xilinx ZU+ MPSoC ZU1CG with Dual Cortex-A53 APU @ up to 1.3 GHz and dual Cortex-R5 RPU @ up to 533 MHz 256KB On-chip Memory 81,900 FPGA Logic Cells System Memory – 1GB LPDDR4 with on-chip ECC Storage – 256Mbit QSPI flash, microSD card, both bootable Networking – 10/100/1000M Gigabit Ethernet RJ45 port USB […]