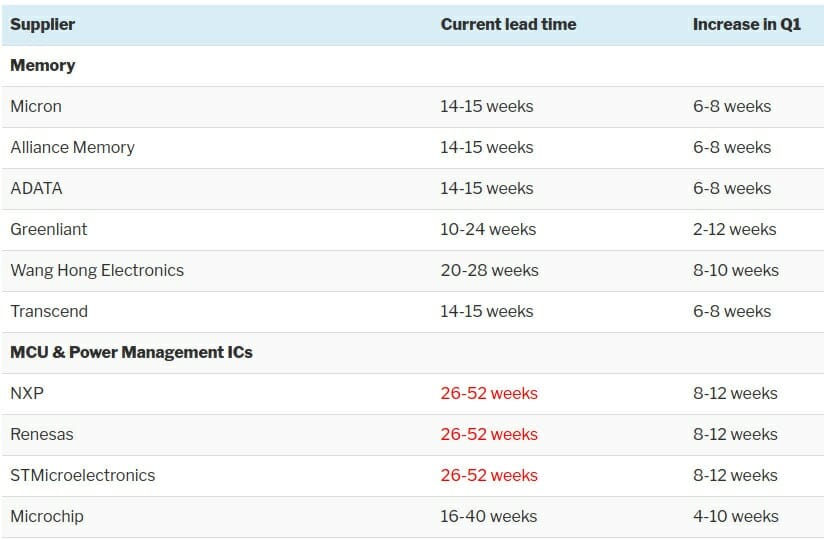

As we previously mentioned previously there is a serious chip shortage that will lead to supply issues and higher prices for single board computers and other electronics products. A few days ago, Hardkernel had o increase the price for ODROID boards using DDR4 memory with increases of $3 to $4 for ODROID-N2+, ODROID-C4, and ODROID-HC4 boards. But besides price increase, some semiconductors will not be available at any price with extended periods as lead times of up to 52 weeks have been reported as shown in the table below, obtained from a trusted, anonymous source, which I have translated from Chinese. Every manufacturer is impacted, but items highlighted in red are severely impacted. Since include processors from Qualcomm, STMicroelectronics, and NXP, as well as Broadcom wireless chips which are found in nearly every SBC with WiFi or Bluetooth through Ampak modules. Here’s the source image in Chinese for reference. Jean-Luc […]

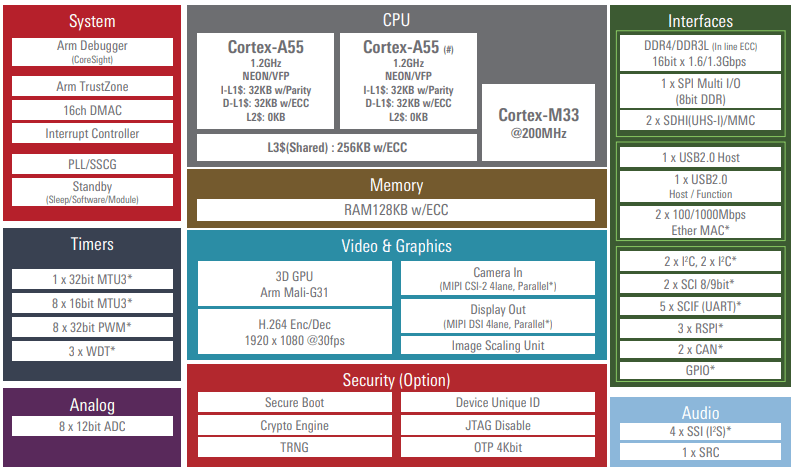

Renesas RZ/G2L MPUs Feature Cortex-A55 & Cortex-M33 Cores for AI Applications

Renesas Electronics Corporation announced RZ/G2L MPUs, allowing enhanced processing for an extensive variety of AI applications. The RZ/G2L group of 64-bit MPUs includes three new MPU models featuring Arm Cortex-A55, and an optional Cortex-M33 core. These are RZ/G2L, RZ/G2LC, and RZ/G2UL MPUs. The Cortex-A55 CPU core typically delivers approximately 20 percent improved processing performance compared with the previous Cortex-A53 core, and according to Renesas, is around six times faster in “essential processing for AI applications”. The company already has four mid to high-end design level MPUs including RZ/G2E, RZ/G2N, RZ/G2M, and RZ/G2H, with combinations of Cortex-A53 and Cortex-A57 cores. The new RZ/G2L group of three MPUs forms the entry-level design with Cortex-A55. Hence, the seven MPU models together provide scalability from entry-level to high-end design. Common Key Features in RZ/G2L, RZ/G2LC, and RZ/G2UL MPUs Up to 2x Cortex-A55 cores Cortex-M33 core Camera interface (MIPI-CSI) Display interface (Parallel-IF) USB 2.0 interface […]

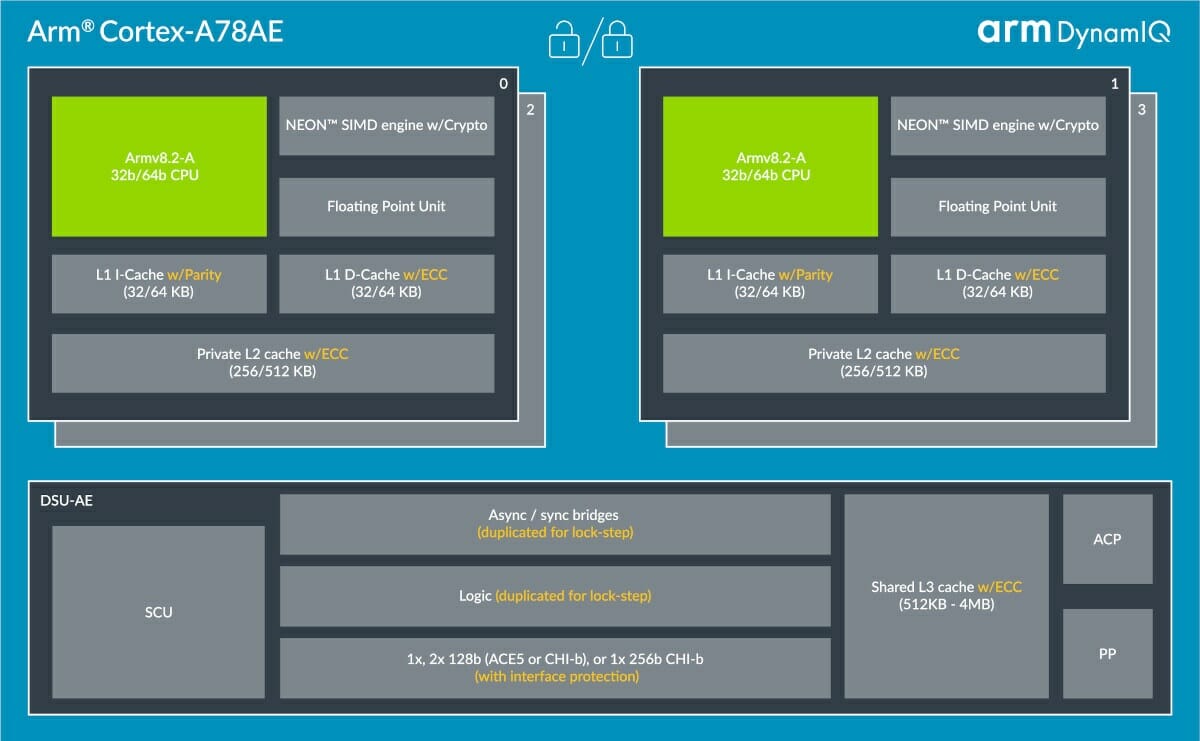

Arm Announces Cortex-A78AE CPU, Mali-G78AE GPU & Mali-C71AE ISP for autonomous automotive & industrial applications

Arm has announced new CPU, GPU, and ISP specifically designed for autonomous automotive and industrial applications with respectively Cortex-A78AE CPU, Arm Mali-G78AE GPU, and Arm Mali-C71AE ISP. Arm Cortex-A78AE CPU Key features and specifications: Architecture – Armv8.2-A (AArch32 at ELO only) Extensions – Armv8.1, Armv8.2, and Armv8.3 extensions (LDAPR instructions only), RAS extensions, Armv8.4 Dot Product, Cryptography extensions, RAS extensions Microarchitecture Up to 4x CPU cores per cluster Out of order pipeline Neon / Floating Point Unit included with INT8 Dot Product and IEEE FP16 Optional Cryptography Unit 48-bit Physical Addressing (PA) Memory system and external interfaces 32kB to 64kB L1 I-Cache / D-Cache 256kB to 512kB L2 Cache Optional 512kB to 4MB L3 Cache ECC Support LPAE Bus interfaces – AMBA ACE or CHI Optional ACP, peripheral port Functional Safety Support – ASIL D Systematic1 and ASIL D Diagnostic2 Security – TrustZone Interrupts – External GICv4 Generic timer – […]

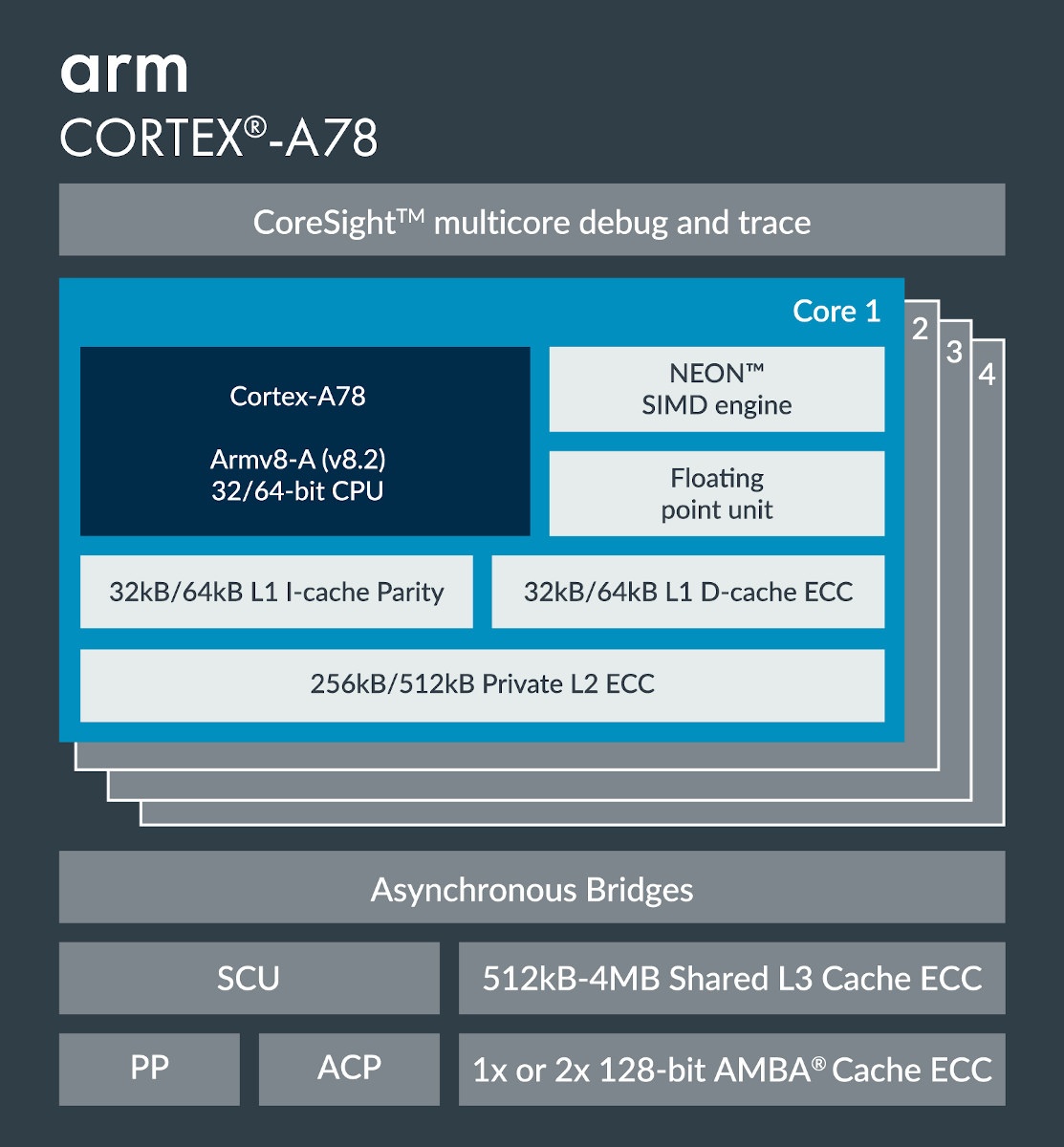

Arm Announces Cortex-A78 CPU, Mali-G78 GPU, Ethos-N78 NPU and Custom Cortex-X1 Core

Arm has just announced its 2020 Arm Mobile IP portfolio with no less than five IP blocks including Arm Cortex-A78 CPU, Arm Mali-G78 and G68 GPUs, Arm Ethos-N78 neural processing unit, and the custom Cortex-X program starting with Cortex-X1, the most powerful Arm core to date. Arm Cortex-A78 CPU Cortex-A78 highlights: Architecture – Armv8-A (Harvard) Extensions – Armv8.1, Armv8.2, Cryptography, and RAS; Armv8.3 (LDAPR instructions only) ISA support – A64, A32, and T32 (at EL0 only) Microarchitecture Pipeline – Out of order Superscalar Neon / Floating Point Unit Optional cryptography Unit Max number of CPUs in cluster – 4 Physical Addressing (PA) – 40-bit Memory system and external interfaces 32KB to 64KB L1 I-Cache / D-Cache 256KB to 512KB L2 Cache Optional 512KB to 4MB L3 Cache ECC and LPAE support Trustzone security Cortex-A78 delivers 20% extra performance compared to Cortex-A77 at the same power budget (one Watt), but peak […]

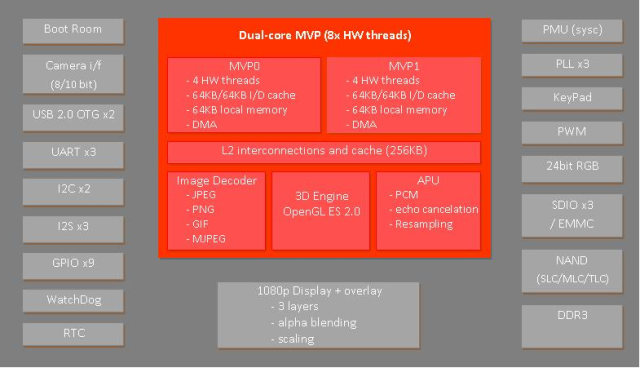

ICube MVP SoCs Combine CPU and GPU into a Single Unified Processing Unit (UPU)

ICube is a fabless semiconductor company developing SoCs featuring a Unified Processing Unit (UPU) that takes care of the tasks usually handle by separate CPU and GPU on typical SoCs. The UPUs are based on MVP (Multi-thread Virtual Pipeline) instruction set architecture, and are themselves called MVP cores. The company has now two SoCs based on UPU MVP cores: IC3128 and IC3228. IC3128 is a single core / 4 thread SoC, and IC3228 is a dual MVP core / 8 threads SoC. Let’s have a look at IC3228 technical specifications: CPU function 4-way simultaneous multi-threading (SMT) in each core Symmetric-multi-processing (SMP), dual MVP cores 64KB I-cache, 64KB D-cache and 64KB local memory in each core, 256KB shared L2 cache Homogeneous parallel programs Support Pthread, OpenMP GPU function Data parallel, Task parallel, and/or Function parallel computing Multi-standard media processor Programmable unified shader Support OpenGL ES 2.0 70 million triangles / sec, […]

Embedded Linux Optimization Techniques – ELCE 2011

Benjamin Zores, Alcatel-Lucent, describes different optimization techniques (focusing on hardware choice and software architecture) that can be used to improve the performance of embedded linux at Embedded Linux Conference Europe 2011. Abstract: This presentation provides a series of techniques that can be used for Linux embedded systems fine-grain tuning and performances optimization. Embedded systems are, by definition, always limited in terms of resources while people keep on trying to use desktop-oriented software on top of it. This talk presents a series of tips that can be used to actually measure, find and isolate bottlenecks in your system, whether it is by complete system profiling or software architecture optimization. Focus is also made on the traditional caveats that need to be avoided for your system not to be slow by design. You can also download the presentation slides. Jean-Luc Aufranc (CNXSoft)Jean-Luc started CNX Software in 2010 as a part-time endeavor, before […]