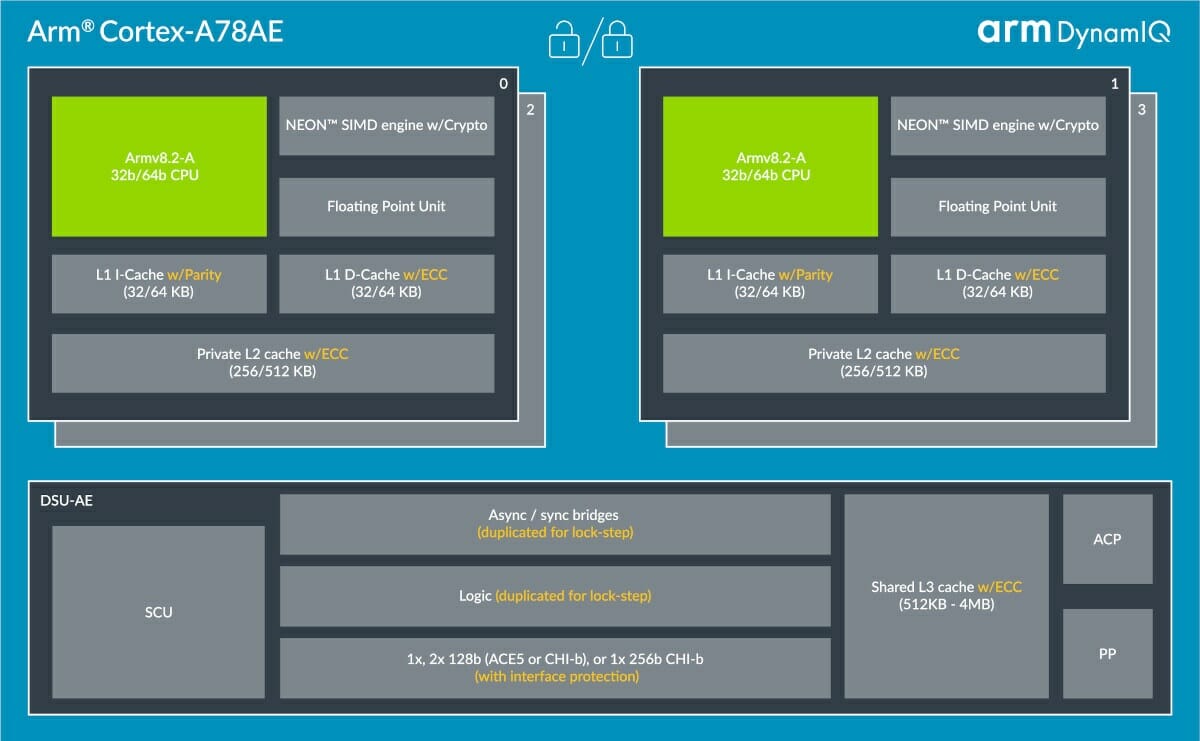

Arm has announced new CPU, GPU, and ISP specifically designed for autonomous automotive and industrial applications with respectively Cortex-A78AE CPU, Arm Mali-G78AE GPU, and Arm Mali-C71AE ISP. Arm Cortex-A78AE CPU Key features and specifications: Architecture – Armv8.2-A (AArch32 at ELO only) Extensions – Armv8.1, Armv8.2, and Armv8.3 extensions (LDAPR instructions only), RAS extensions, Armv8.4 Dot Product, Cryptography extensions, RAS extensions Microarchitecture Up to 4x CPU cores per cluster Out of order pipeline Neon / Floating Point Unit included with INT8 Dot Product and IEEE FP16 Optional Cryptography Unit 48-bit Physical Addressing (PA) Memory system and external interfaces 32kB to 64kB L1 I-Cache / D-Cache 256kB to 512kB L2 Cache Optional 512kB to 4MB L3 Cache ECC Support LPAE Bus interfaces – AMBA ACE or CHI Optional ACP, peripheral port Functional Safety Support – ASIL D Systematic1 and ASIL D Diagnostic2 Security – TrustZone Interrupts – External GICv4 Generic timer – […]

Arm Announces Cortex-A78 CPU, Mali-G78 GPU, Ethos-N78 NPU and Custom Cortex-X1 Core

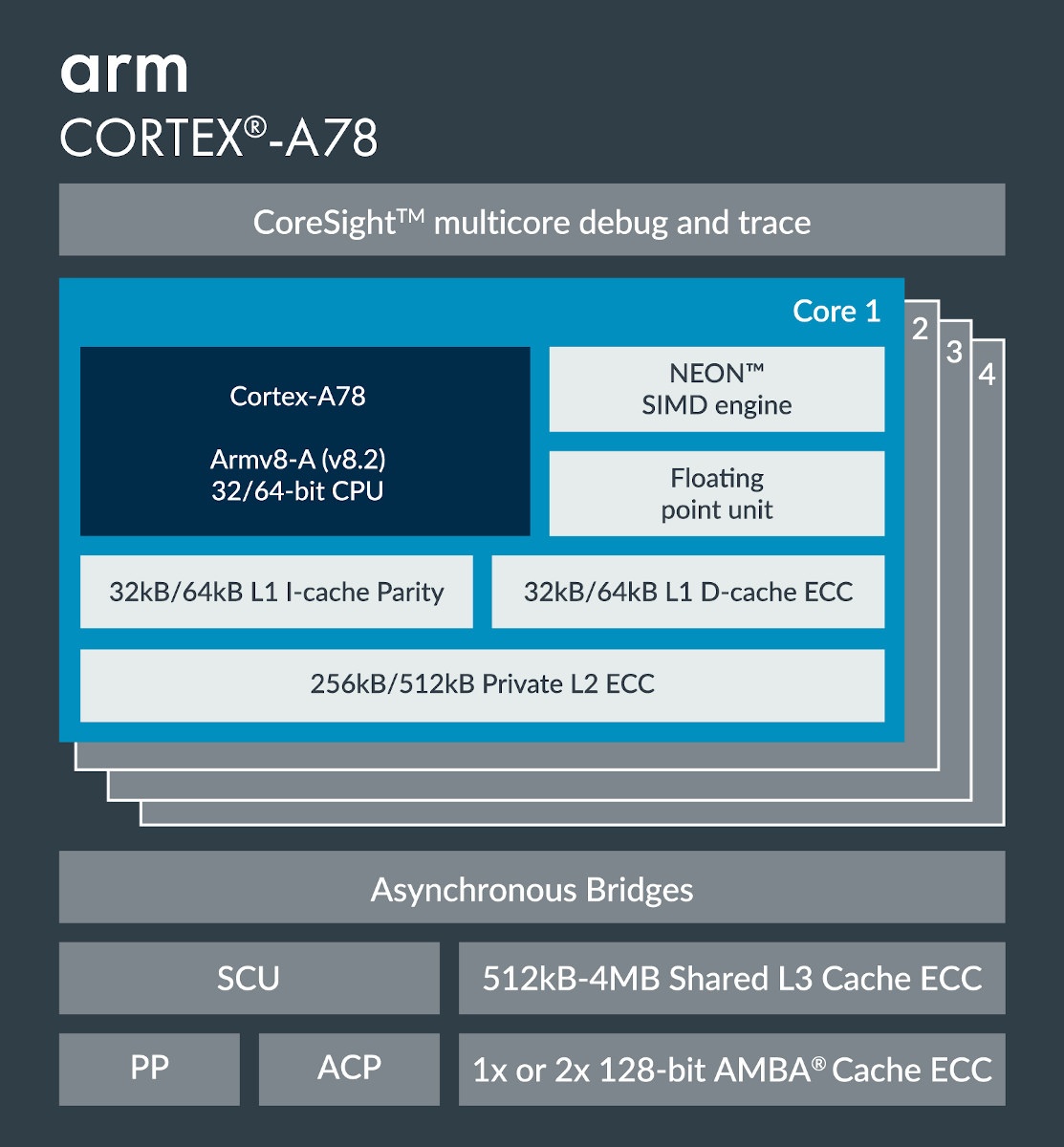

Arm has just announced its 2020 Arm Mobile IP portfolio with no less than five IP blocks including Arm Cortex-A78 CPU, Arm Mali-G78 and G68 GPUs, Arm Ethos-N78 neural processing unit, and the custom Cortex-X program starting with Cortex-X1, the most powerful Arm core to date. Arm Cortex-A78 CPU Cortex-A78 highlights: Architecture – Armv8-A (Harvard) Extensions – Armv8.1, Armv8.2, Cryptography, and RAS; Armv8.3 (LDAPR instructions only) ISA support – A64, A32, and T32 (at EL0 only) Microarchitecture Pipeline – Out of order Superscalar Neon / Floating Point Unit Optional cryptography Unit Max number of CPUs in cluster – 4 Physical Addressing (PA) – 40-bit Memory system and external interfaces 32KB to 64KB L1 I-Cache / D-Cache 256KB to 512KB L2 Cache Optional 512KB to 4MB L3 Cache ECC and LPAE support Trustzone security Cortex-A78 delivers 20% extra performance compared to Cortex-A77 at the same power budget (one Watt), but peak […]