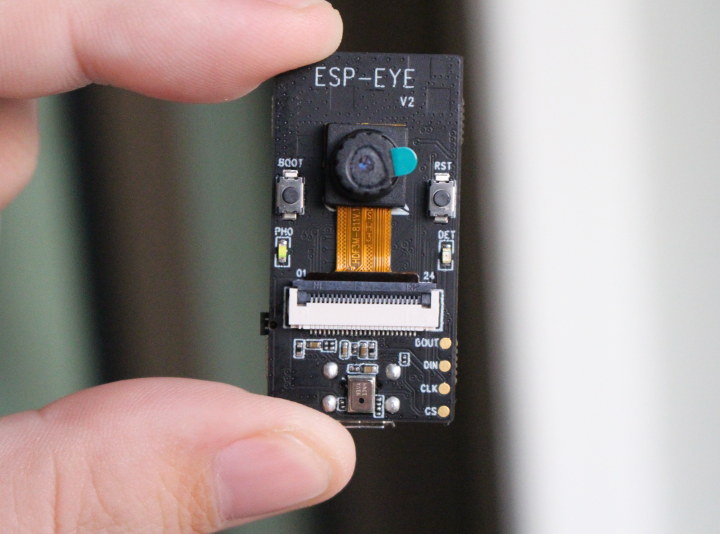

Sometimes last month, Espressif Systems contacted me to send a mysterious new development kit together with a 10-year anniversary T-shirt, an offer I found hard to decline 🙂 So I got a new year present this morning delivered by DHL… The letter lists the main specifications of ESP-EYE development board: WiSoC- ESP32 dual core Tensilica LX6 processor with WiFi and Bluetooth Memory – 8MB PSRAM Storage – 4MB flash Camera – 2MP OV2640 camera Audio – Microphone USB – 1x micro USB port for power and programming Misc – Reset, boot and function buttons, 2x LEDs Dimensions – 41 x 21 mm It reminds me of ESP32-CAM camera board, except it adds a microphone, it’s even smaller, and as an official Espressif board, software support might be better. AI features such as face recognition or detection, and voice wake-up are supported out of the box. The board ships with a […]

MediaTek Helio P90’s APU 2.0 Quadruples AI Performance

Mediatek has launched another of their Helio P-series processor. We’ve gotten used to getting incremental improvements when it comes with CPU and GPU performance, but now companies are able to deliver massive improvement for neural network accelerators, and MediaTek Helio P90 can deliver four times (4.6x) the A.I. performance over Helio P60/P70 thanks to its APU 2.0. MediaTek Helio P90 key features & specifications: CPU – 2x Arm Cortex-A75 processors @ 2.2GHz and 6x Arm Cortex-A55 processors @ 2.0GHz using DynamIQ technology GPU – Imagination PowerVR GM 9446 GPU @ 970 MHz NPU – MediaTek APU 2.0 fusion AI architecture with 1127 GMACs (2.25TOPs) MediaTek CorePilot for sustainable peak performance, longer battery life and lower operating temperature System Memory – Up to 8GB of LPDDR4x memory @ 1866MHz Storage – UFS 2.1 Display – Full HD+ (2520×1080) resolution, 21:9 aspect ratio Camera Up to 48MP single camera or 24+16MP dual […]

Qualcomm Snapdragon 855 Specifications Published

Qualcomm Tech Summit 2018 started yesterday, and while the company mentioned Snapdragon 855, they focused on the benefit of 5G technology. Today is another day, and this time the company released details specifications about the new 5G mobile platform. Snapdragon 855 specifications: CPU – 8x Qualcomm Kryo 485 64-bit cores @ up to 2.84 GHz; 7nm Process Technology; based on leaks, tri-cluster configuration: 1+3+4 Visual Subsystem Adreno 640 GPU OpenGL ES 3.2, OpenCL 2.0 FP, Vulkan 1.1 API support HDR gaming Hardware-accelerated H.265 and VP9 decoder. HDR Playback Codec support for HDR10+, HDR10, HLG and Dolby Vision Volumetric VR video playback 8K 360 VR video playback Qualcomm Artificial Intelligence Engine Qualcomm Hexagon 690 Processor Qualcomm Hexagon Vector Accelerator Qualcomm Hexagon Tensor Accelerator Qualcomm Hexagon Voice Assistant Qualcomm All-Ways Aware Hub Qualcomm Adreno 640 GPU Qualcomm Kryo 485 CPU System Memory – 4×16-bit, LPDDR4x, up to 16GB @ 2133 MHz Display […]

VIA ALTA DS 3 Edge AI system Features Snapdragon 820E Processor

VIA has recently introduced ALTA DS 3 Edge AI system, a mini PC for the retail market powered by Qualcomm Snapdragon 820E processor, and targeting intelligent digital signage, kiosk, and access control devices that require real-time image and video capture, processing, and display capabilities. VIA Alta DS 3 Edge AI system specifications: SoC – Qualcomm Snapdragon 820E quad core 64-bit Kryo CPU processor @ up to 2.15 GHz, Adreno 530 GPU @ 624 MHz supporting OpenGL ES 3.1/GEP, GL4.4, DX11.3/4, OpenCL 2.0, Renderscript-Next System Memory – 4GB POP LPDDR4 RAM Storage – 16GB eMMC flash memory, M.2 slot for M.2 2280 NVMe SSD (PCIe 1 Lane), SD card slot Video Output – 2x HDMI ports: one HDMI 2.0 port and one HDMI 1.4 port via dual DSI to HDMI converter Video Playback – H.264, H.265 (HEVC 8/10-bit) video decoding up to 4K@60fps Audio – WCD9335 Audio Codec; 3.5mm Line OUT […]

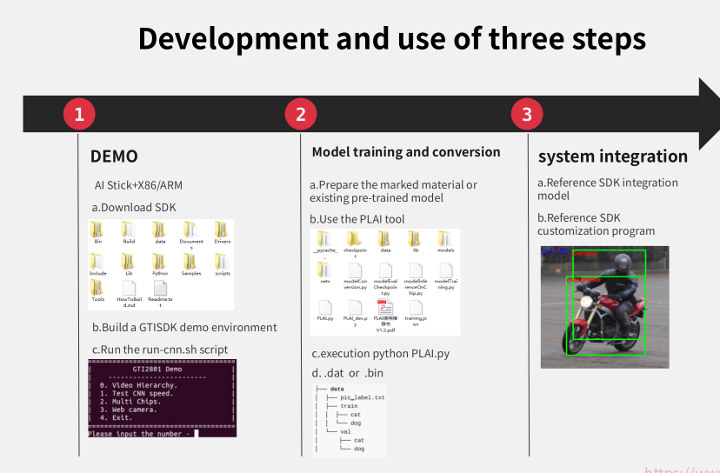

Orange Pi AI Stick 2801 Neural Compute Stick SDK & Documentation Released

We covered the launch of Orange Pi AI Stick 2801 neural compute stick a few days ago, the first easily available Gyralcon Lightspeeur based USB stick, and noted that while the hardware was there, we had no details about software development kit and documentation at the time. I’ve got some more information now. First, the company release an English presentation about the neural stick, and while it’s not technical documentation, it provides insights into what it is capable of, and an overview about the workflow. More importantly, Shenzhen Xunlong Software also released Orange Pi AI Stick SDK and user manual for x86 PC, as well as cat/dog data and pre-trained models to get started. However, if you want to perform training with your own data, you’ll need to purchase the stick plus PLAI model transformation and training tools sold on Aliexpress for $218 plus shipping, that’s $69 for the hardware, […]

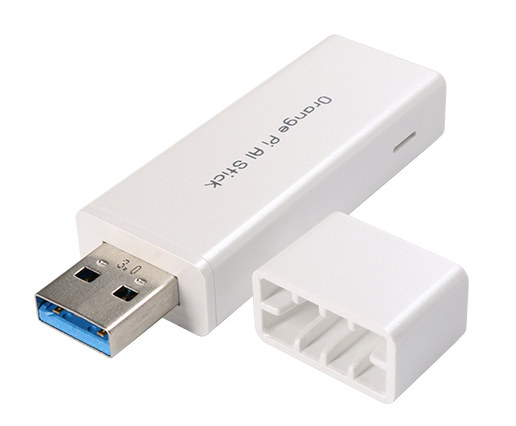

$69 Orange Pi AI Stick 2801 Features Lightspeeur 2801S Neural Processor

Intel is not the only company selling neural compute sticks to accelerate artificial intelligence workloads at low power, as Gyrfalcon introduced their Laceli AI Compute Stick based on their own Lightspeeur 2801S matrix processor earlier this year, but it was not exactly easy to buy. Even the company’s latest PLAI Plug USB3.0 dongle (new name for Laceli AI Compute Stick?) and PLAI WiFi AI wireless accessory announced just a few days ago are not that easy to purchase, as they require you to fill a form with your project details before being able to buy anything. But thanks to Shenzhen Xunlong Software, the Orange Pi boards maker, it’s now much easier to experiment with the technology since they launched Orange Pi AI Stick 2801, based on the same Lightspeeur 2801S ASIC found in PLAI Plug, but sold directly on Aliexpress for $69 plus shipping ($73.97 in total here). Orange Pi […]

Intel Neural Compute Stick 2 with Myriad X VPU Finally Announced

Intel Neural Compute Stick was first introduced in early 2017 as a USB compute that allows AI inference at the edge with low power consumption. The stick is based on Myriad Movidius 2 VPU (Vision Processing Unit), and was found to significantly improve inference performance on Raspberry Pi 3 board over a proprietary GPU accelerated solution. However, a little later last year, Intel also announced Movidius Myriad X VPU with claims of up to 10 times DNN performance over Myriad 2 VPU. But so far, we would only see solutions launched with the latter, and it looks like Intel is finally ready to bring Myriad X VPU to the market with the company announcing Intel Neural Compute Stick 2 at Intel’s artificial intelligence (AI) developer conference in Beijing taking place on November 14 and 15. Intel NCS 2 (Neural Compute Stick 2) specifications: Processor – Intel Movidius Myriad X Vision Processing […]

Samsung Exynos 9820 Application Processor Supports 2 Gbps LTE, 8K Videos, UFS 3.0 Storage

Samsung has just unveiled a new high-end Exynos processor that comes with an enhanced NPU (Neural Processing Unit), and an LTE Advanced Pro modem supporting 2.0 Gbps downloads. Exynos 9820 is a tri-cluster octa-core processor with two custom Arm cores, two Cortex-A75 cores, and four Cortex-A55 cores coupled with an Arm Mali-G76 MP12, and manufactured using Samsung’s latest 8nm LPP FinFET process, which reduces power consumption by up to 10 percent compared to 10nm LPP process. Samsung Exynos 9820 key features and specifications: CPU – Dual-core custom CPU + dual-core Cortex-A75 + quad-core Cortex-A55 GPU – ARM Mali-G76 MP12 Integrated NPU Memory I/F – LPDDR4x Storage I/F – UFS 3.0, UFS 2.1 Display – WQUXGA (3840×2400), 4K UHD (4096×2160) Cellular Connectivity LTE Modem – LTE-Advanced Pro Cat.20 8CA 2Gbps (DL) / Cat.20 3CA 316Mbps (UL) 4×4 Multiple-Input, Multiple-Output (MIMO), 256-QAM (Quadrature Amplitude Modulation), and Enhanced Licensed-Assisted Access (eLAA) technology. Camera […]