Manufactured with a 4nm processor, the MediaTek Dimensity 7200 is an octa-core Armv9 processor designed for mainstream smartphones. with two Cortex-A715 cores, six Cortex-A510 cores, a Mali-G610 MC4 GPU, as well as 5G, WiFi 6E, and Bluetooth 5.3 connectivity. So far, I had only seen Armv9 SoCs with a mix of Cortex-A510 “LITTLE” cores, Cortex-A710/A715 “big” core, and Cortex-X2 or Cortex-X3 “flagship cores” as found in the Dimensity 9200 processor, but the Dimensity 7200 is one of the first Armv9 processors – one other being the Snapdragon 7 Gen 1 – without a Cortex-X core in order to provide a more affordable solution. MediaTek Dimensity 7200 specifications: CPU 2x Arm Cortex-A715 up to 2.8GHz 6x Arm Cortex-A510 2MB L3 cache GPU – Arm Mali-G610 MC4 with MediaTek HyperEngine 5.0 APU – MediaTek APU 650 AI accelerator DPU/VPU – MediaTek MiraVision 765 engine for display and 4K HDR video decoding/encoding Memory […]

Arm unveils Cortex-X3 and Cortex-A715 Armv9 cores, improves Cortex-A510 efficiency

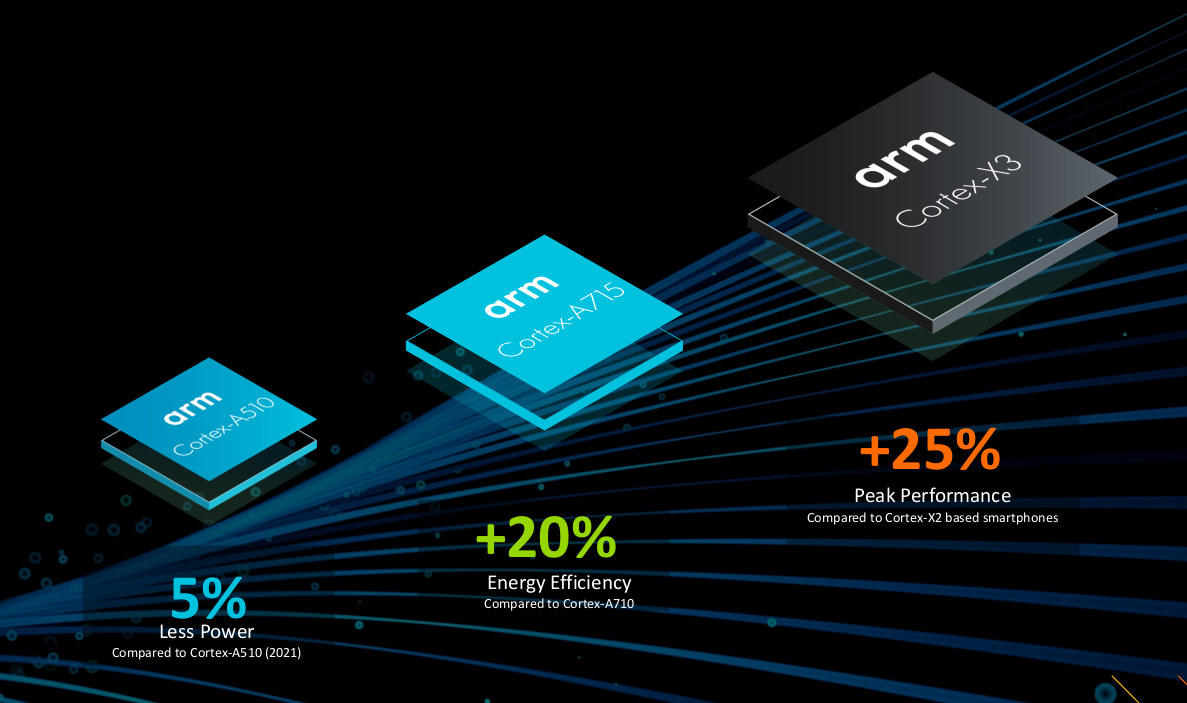

Besides announcing the new Immortalis-G715, Mali-G715, and Mali-G615 GPUs, Arm has also introduced the second-generation of Armv9 cores with the Cortex-A715 and Cortex-X3 cores with respectively a 20% energy-efficiency improvement (and smaller 5% performance uplift) over the Cortex-A710 core and a 25% peak performance boost against the Cortex-X2 flagship core. The announcement also includes a “refresh” of the Cortex-A510 core announced last year with a 5% improvement in efficiency and the same level of performance. The Cortex-X3 will also be used in (Windows 11) laptop processors with the single-thread performance improved by up to 34% in that case. Armv9 mobile SoC (Total Compute) in 2023 Future Armv9 flagship mobile SoC worked on this year, and released in 2023 should have a combination of Cortex-X3, Cortex-A715, and Cortex-A510 cores, an Immortalis-G715 GPU, a new DSU-110 “DynamIQ Shared Unit” that supports 50% more cores in CPU clusters (or up to 12 cores […]

Snapdragon 8 Gen 1 Mobile Platform features 3 GHz Cortex-X2 core, 10 Gbps 5G modem

A couple of weeks ago, MediaTek introduces the Dimensity 9000 5G processor with a Cortex-X2 core clocked at 3 GHz, and it was just a matter of time before Qualcomm announces its own Armv9 processor. So here we are with the “Snapdragon 8 Gen 1 Mobile Platform” equipped with an octa-core CPU subsystem comprised of one Cortex-X2 core clocked at 3 GHz, Cortex-A710 and Cortex-A510 cores, LP-DDR5 memory, as well as an integrated Snapdragon X65 5G modem capable of 10 Gbps download speeds, and all of that manufactured with the latest 4nm Samsung process. Snapdragon 8 Gen 1 (SM8450) specifications: Octa-core Kryo CPU subsystem (details courtesy of Anandtech since Qualcomm will not usually reveal this information) 1x Arm Cortex-X2 core @ 3.0GHz with 1024KB L2 cache 3x Arm Cortex-A710 cores @ 2.5GHz with 512KB L2 cache each 4x Arm Cortex-A510 cores @ 1.80GHz in two clusters, each with an unspecified […]

Dimensity 9000 – MediaTek’s 4nm, 3 GHz octa-core Armv9 processor for flagship 5G smartphones

MediaTek is the top mobile SoC vendor in terms of unit shipped, well ahead of the competition, but the company’s processors were mostly found in entry-level, mid-range, and “premium” smartphones, while flagship smartphones usually feature application processors from Qualcomm, Samsung, or Apple. But MediaTek has upped the ante with the introduction of the Dimensity 9000 smartphone processor featuring an octa-core Armv9 CPU subsystem, including one Cortex-X2 core clocked at up to 3.05 GHz, a Mali-G710 MC10 GPU, 5G connectivity, and manufactured with the bleeding edge 4nm TSMC manufacturing process. Dimensity 9000 specifications: Octa-core CPU subsystem 1x Arm Cortex-X2 “Ultra Core” at 3.05 GHz 3x Arm Cortex-A710 “Super Cores” at up to 2.85 GHz 4x Arm Cortex-A510 “Efficiency Cores” up to 1.80GHz 8MB L3 cache GPU – Mali-G710 MC10 @ 850 MHz with support for Vulkan, (software) raytracing AI Accelerator – 5th generation APU (AI processing unit) with up to 4x […]

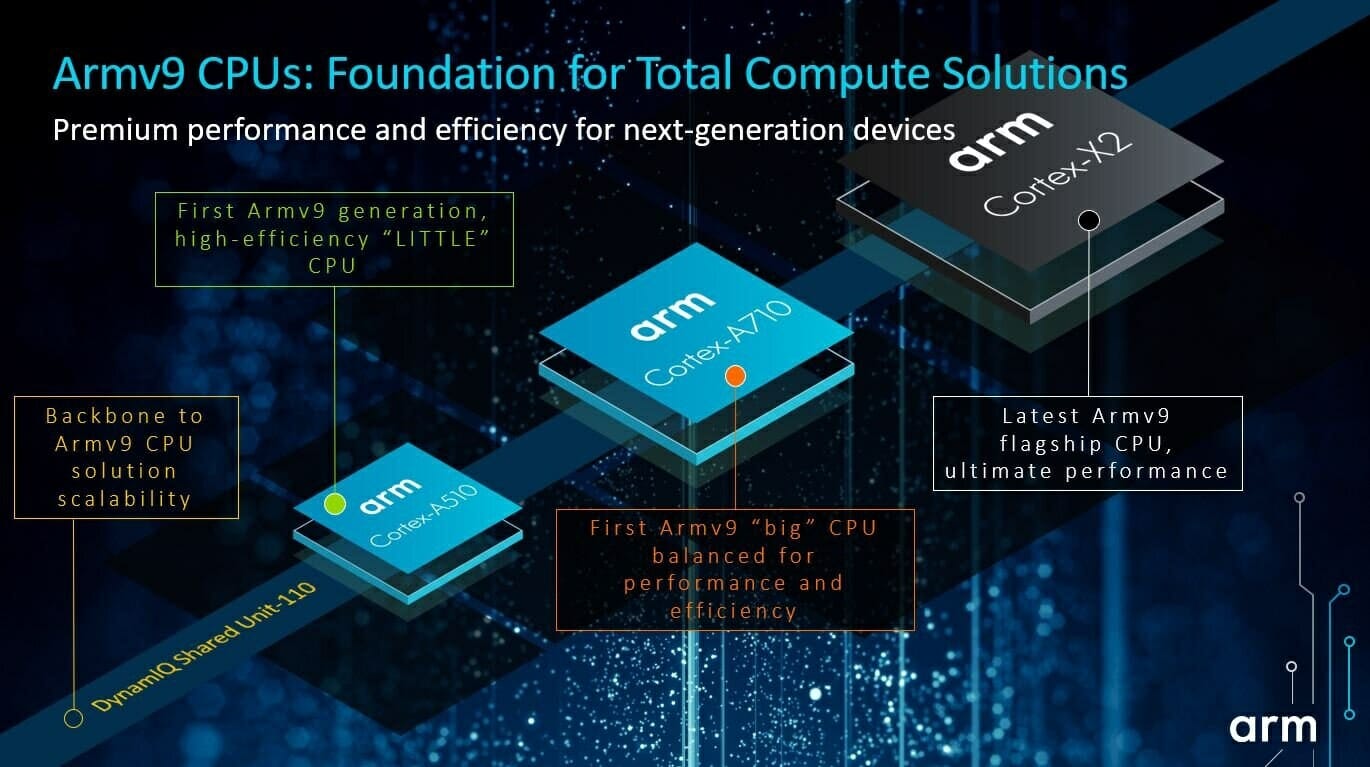

First Armv9 cores unveiled – Cortex-A510, Cortex-A710, Cortex-X2

Armv9 architecture was announced in Q1 2021, building upon Armv8 but adding blocks and instructions for artificial intelligence, security, and “specialized compute”, i.e. hardware accelerators or instructions optimized for specific tasks. The company has now introduced the first three Armv9 cores with Cortex-X2, Cortex-A710, and Cortex-A510 cores, providing updates to respectively Cortex-X1, Cortex-A78, and Cortex-A55 cores. The company calls those new cores “Arm Total Compute solutions”. Arm Cortex-X2 flagship core is the company’s most powerful CPU so far with 30% performance improvements over Cortex-X1 and will be found in premium smartphones and laptops. Arm Cortex-A710 “big” CPU core provides a 30% energy efficiency gain and 10% uplift in performance compared to Cortex-A78, while Arm Cortex-A510, high efficiency “LITTLE” Armv9 core delivers up to 35% performance improvements and over 3x uplift in ML performance compared to Cortex-A55 announced four years ago, or about the same performance as the “big” Cortex-A73 cores […]

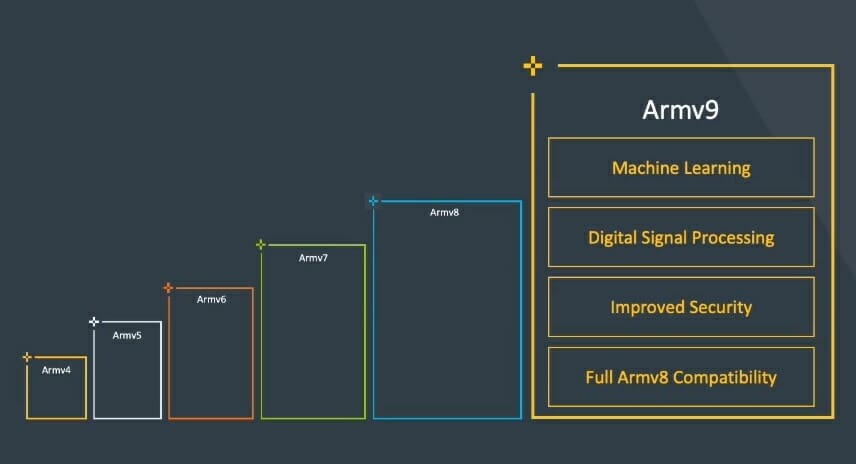

Armv9 architecture to focus on AI, security, and “specialized compute”

Armv8 was announced in October 2011 as the first 64-bit architecture from Arm. while keeping compatibility with 32-bit Armv7 code. Since then we’ve seen plenty of Armv8 cores from the energy-efficient Cortex-A35 to the powerful Cortex-X1 core, as long as some custom cores from Arm partners. But Arm has now announced the first new architecture in nearly ten years with Armv9 which builds upon Armv8 but adds blocks for artificial intelligence, security, and “specialized compute” which are basically hardware accelerators or instructions optimized for specific tasks. Armv9 still supports Aarch32 and Aarch64 instructions, NEON, Crypto Extensions, Trustzone, etc…, and is more an evolution of Armv8 rather than a completely new architecture. Some of the new features brought about by Armv9-A include: Scalable Vector Extension v2 (SVE2) is a superset of the Armv8-A SVE found in some Arm supercomputer core with the addition of fixed-point arithmetic support, vector length in multiples […]