Linus Torvalds announced the release of Linux Kernel 3.17 on Sunday: So the past week was fairly calm, and so I have no qualms about releasing 3.17 on the normal schedule (as opposed to the optimistic “maybe I can release it one week early” schedule that was not to be). However, I now have travel coming up – something I hoped to avoid when I was hoping for releasing early. Which means that while 3.17 is out, I’m not going to be merging stuff very actively next week, and the week after that is LinuxCon EU… What that means is that depending on how you want to see it, the 3.18 merge window will either be three weeks, or alternatively just have a rather slow start. I don’t mind getting pull requests starting now (in fact, I have a couple already pending in my inbox), but I likely won’t start processing […]

ARM Announces mbed OS for ARM Cortex-M Micro-controllers and mbed Device Server for the Cloud

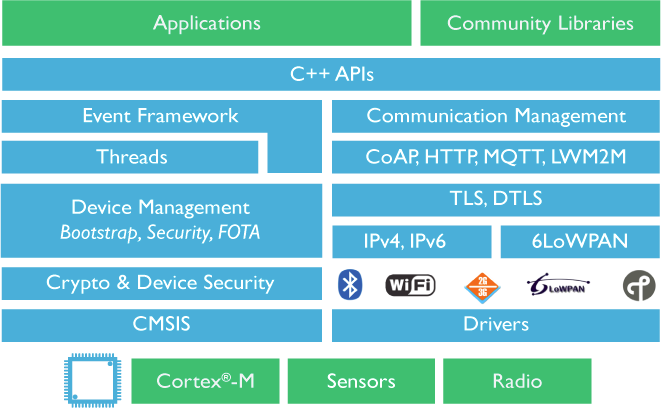

ARM has just announced two new software products for mbed development boards at ARM Techcon 2014: mbed OS, an operating system for Cortex-M MCUs, and mbed Device Server to handle IoT data in the cloud. Together with existing mbed hardware, these form what ARM now calls mbed IoT Device Platform. mbed OS is a free operating system for ARM Cortex-M processor with security, communication and device management features necessary to enable IoT devices. It will provide a C++ application framework, and the software stack includes support for Bluetooth Smart, 2G, 3G, LTE and CDMA cellular technologies, Thread, Wi-Fi, 802.15.4 / 6LoWPAN, TLS/DTLS, CoAP, HTTP, MQTT and Lightweight M2M. No need to look for your mbed board, planning to try it out just yet however, as mbed OS (alpha) will be available to partners in Q4 2014, and there will be alpha and beta releases during the course of 2015, before […]

STMicro STM32F4 (Cortex M4) vs STM32F7 (Cortex M7) Graphics Demo

STMicro announced their latest STM32F7 micro-controller family based on ARM Cortex M7 last week. As ARM Techcon 2014 is now taking place, the company has uploaded an infomercial on their YouTube account, where STMicro and ARM representatives are interviewed about the new family, and talk about its performance, power consumption, target applications, business prospects, and so on. But there’s also an a short demo with two development kits one with a STM32F4 cortex M4 micro-controller, and the other with a STM32F7 micro-controllers. Since both MCU families are pin-to-pin compatible, the hardware is identical except for the MCU. Both kits are pre-loaded with a 3D graphics demo (ray tracer), and the board with STM32F7 completes the demo in about half the time of the one with STM32F439, allegedly with about the same power consumption (7 coremarks / mW). The video is about 8 minutes long, and the demo starts at 1:25. […]

Linaro 14.09 Release with Kernel 3.17 and Android 4.4.4

Linaro 14.09 has just been released with Linux kernel 3.17-rc4 (baseline), Linux 3.10.54 & 3.14.19 (LSK), and Android 4.4.2 & 4.4.4. Linaro has kept working on their member boards such as IFC6410 (Qualcomm), D01 (Huawei/Hisilicon), Ardnale (Samsung), and Juno (ARM). They’ve also announced they’ll change the tools to build GCC by using cbuild2 instead of cbuild1 for next release, and they’ve enabled a build with gcov (for code coverage analysis) which may mean they’ll work on reducing the kernel size by getting rid off unused code. I’ve also noticed the Arndale and Arndale Octa Ubuntu images are now based on Linux LSK with Mali GPU support since last month. Here are the highlights of this release: Linux Linaro 3.17-rc4-2014.09 GATOR version 5.19 updated topic from Qualcomm LT (ifc6410 board support) and HiSilicon LT updated Versatile Express ARM64 support (FVP Base and Foundation models, Juno) from ARM LT. updated Versatile Express […]

ARM Introduces Cortex-M7 MCU Core for IoT, Wearables, Industrial and Automotive Applications

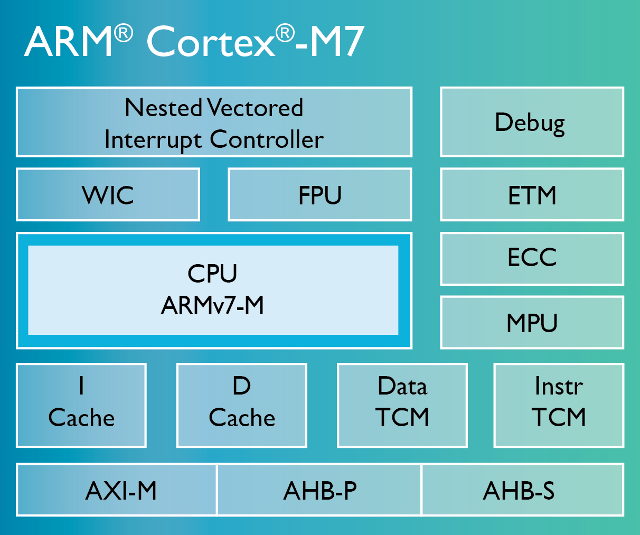

ARM has just announced Cortex-M7 processor based on ARMv7-M architecture, with double the compute and digital signal processing (DSP) capability of ARM Cortex M4. The latest ARM MCU core targets IoT and wearables applications for the automotive, industrial, and consumer markets including motor control, industrial / home / factory automation, advanced audio, image processing, connected vehicle applications, and so on. Cortex-M7 comes with enhanced DSP instructions, a better FPU (FPv5 with single and double precision support), and tight coupled memory compared to Cortex-M4, according to an Anandtech article. ARM Cortex-M7 also achieves 5 CoreMark/MHz against 3.41 CoreMark/MHz for Cortex M4, and up to 3.23 DMIPS/MHz against up to 1.95 DMIPS/MHz. ARM Cortex-M7 features listed in the press release: Six stage, superscalar pipeline delivering 2000 Coremarks at 400MHz in a 40LP process. AXI interconnect (supports 64-bit transfer) and fully integrated optional caches for instruction and data allowing efficient access to large […]

Linaro 14.08 Release with Kernel 3.16 and Android 4.4.4

I’m a little late for that one, as Linaro 14.08 was released last Thursday. Nevertheless, this release features Linux kernel 3.16 (baseline), Linux 3.10.52 (LSK), and Android 4.4.4. As usual Linaro has worked on member hardware such as Qualcomm based IFC6410 and ARM Juno &Vexpress boards. They’ve also committed changes for LLVM, big Endian, and added a workload generator tool (rt-app) to the Ubuntu and Android image. This tool has been developed and used by the power management working group, presumably to measure and optimize power consumption under various loads. Here are the highlights of this release: Linux Linaro 3.16-2014.08 GATOR version 5.19 (new version) updated topic from Qualcomm LT (ifc6410 board support) updated Versatile Express ARM64 support (FVP Base and Foundation models, Juno) from ARM LT (Landing Team) updated Versatile Express patches from ARM LT updated LLVM topic (follows the community llvmlinux-latest branch) Big endian support (the 2014.05 topic […]

Embedded Linux Conference Europe 2014 Schedule – IoT, ARM vs x86, Optimization, Power Management, Debugging…

The Embedded Linux Conference Europe (ELC 2014), CloudOpen, and LinuxCon Europe will jointly take place at the Congress Centre Düsseldorf, in Germany on October 13 – 15, 2014. The 3-day events will consists of keynotes, presentations, and tutorials. Each day will open with two or three keynotes by speakers including Jim Zemlin (Executive Director, Linux Foundation), and Jono Bacon (XPRIZE), followed by presentation and tutorials. There will be 45 presentations for ELCE, 58 for LinuxCon, and 47 for CloudOpen, I’ll make a virtual schedule with a few sessions part of the Embedded Linux Conference Europe “track”. Monday, October 13 11:15 – 12:05 – Performance Analysis Using the Perf Suite by Mans Rullgar, Consultant When faced with a performance problem, the initial steps towards a solution include identifying the sections of code responsible and the precise reasons they are time-consuming. To this end, the ‘perf’ profiling tools provide valuable insight into the […]

AllWinner A80 OptimusBoard Octa-core big.LITTLE Development Board is Now Available … for $169

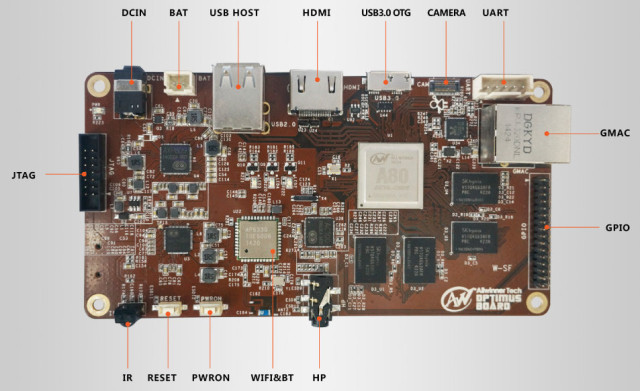

A80 OptimusBoard powered by AllWinner A80 octa-core processor with four Cortex A15 and four Cortex A7 in big.LITTLE configuration had been announced at the end of 2013, and after numerous delays, several boards have recently been sent to developers and companies such as miniNodes, Linuxium, and others. The company behind the board is actually Shenzhen Merrii Technology (aka WITS), which had done all earlier development kits for AllWinner, and they’ve now made the board available for purchase on Aliexpress. Unfortunately the company has decided to leave to low cost development boards market to the likes of Cubieboard8 and PCDuino8, as A80 OptimusBoard sells for $345 plus about $30 for shipping by courier.[Update: they now offer it for $169] SoC – AllWinner Ultra Core A80 4x Cortex 15, 4x Cortex A7 big.LITTLE processor with Imagination Technologies PowerVR GC6230 GPU with 64-cores, and support for OpenGL ES 1.1/2.0/3.0, Directx 9.3 System Memory […]