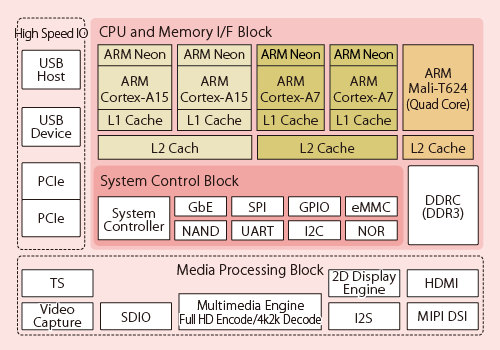

I like to check the ARM Linux kernel mailing list from time to time, as you may discover a few upcoming ARM processors. This week I found out Exynos 5433 and Exynos 7 are actually two different processors (thanks David!), and that AMD had submitted code for their 64-bit ARM Opteron A1100 SoC for servers. I also noticed a patchset for Fujitsu MB86S7X SoCs, and since I don’t often mention Japanese silicon vendors, probably because they now mainly deal mostly with the embedded market that gets very little press, and most information is in Japanese, I decide to have a look. There seems to be four SoC parts in MB86S7x family with MB86S70 quad core processor with two ARM Cortex A15 and two ARM Cortex A7 cores in big.LITTLE configuration, and MB86S73 with two ARM Cortex A7 cores only, as well as MB86S71/72 with 2x A15 and 2x A7, with […]

NXP Introduces LPC54100 Single & Dual Core Cortex M4F/M0+ MCU Family and LPCXpresso54102 Development Kit

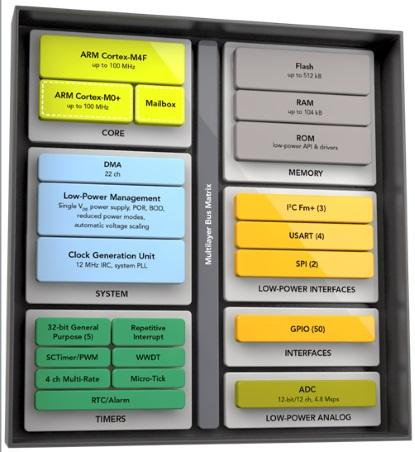

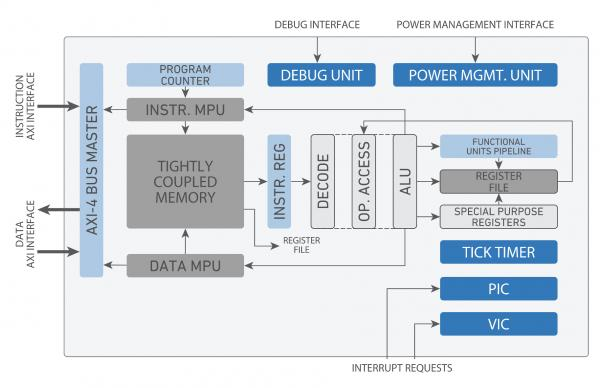

NXP has recently introduced LPC54100 Series microcontrollers with a Cortex-M4F core up to 100MHz, and optionally an ARM Cortex M0+ core for always-on sensor processing applications, as well as LPCXpresso 54102 board. Typical applications include mobile, portable health and fitness, home and building automation, fleet management and asset tracking, robotics and gaming. Key features of LPC54100 series MCUs: CPU – 32-bit ARM Cortex-M4F up to 100 MHz, optional 32-bit ARM Cortex-M0+ coprocessor On-chip RAM – 104 KB internal RAM On-chip Storage – Up to 512 KB on-chip Flash Interfaces 3 fast-mode plus I²C, 4 UART, 2 SPI, 39 GPIO ADC with up to 12-channels, 12 bits, and 4.8 Msps sample rate, full-spec (1.62 V to 3.6 V) Clock Sources – IRC, digital clock input, PLL, 32 kHz XTAL, WWDT Timers – 5x 32-bit general-purpose timers/counters, One-state configurable timer/PWM, RTC with alarm, and WWDT 22-channel DMA with 20-programmable triggers Power consumption […]

ARM Unveils Embedded Systems Education Kit Based on NXP LPC4088 Cortex M4 MCU

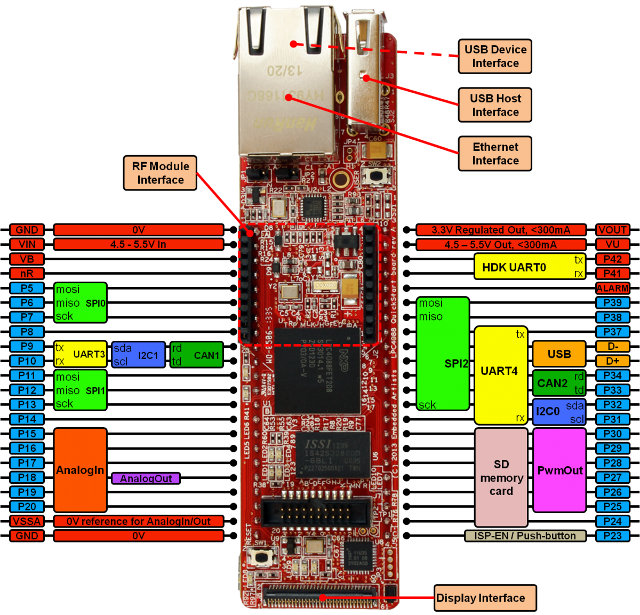

Following up on their first “Lab-In-a-Box” initiative based on Micro STM32F4-Discovery board and Wolfson audio card, ARM launched another low-cost toolkit, based on Embedded Artists LPC4088 QuickStart and Experiment boards, and called “Embedded Systems Education Kit”, to help university educators teach embedded systems design and programming concepts. The kit includes the following hardware, software tools, and teaching materials: Embedded Artists LPC4088 QuickStart Board and LPC4088 Experiment Base Board ARM Keil MDK-ARM Pro microcontroller development suite software licences Complete teaching materials including lecture note slides, demonstration code and hands-on lab manuals with solutions in source for four embedded system courses: ‘Efficient embedded systems design and programming’ teaches microcontroller fundamentals using NXP’s 32-bit ARM Cortex-M4 based LPC4088 microcontroller. ‘Rapid embedded system design and programming’ delivers embedded systems design training for the high-level ARM mbed API ‘OS design’ uses the royalty-free ARM Keil RTX RTOS to show how to design, program and optimize […]

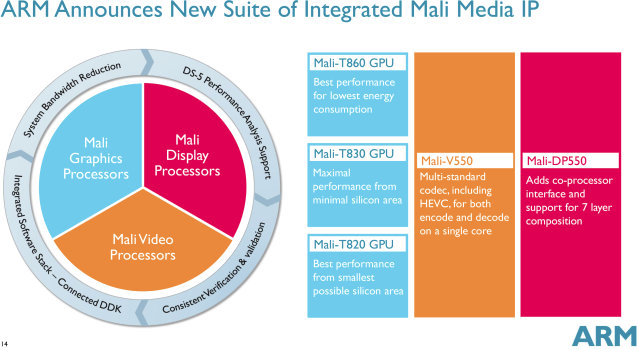

ARM Unveils Mali-T800 Series GPUs, Mali-V550 VPU, and Mali-DP550 Display Processor

ARM has just announced several new Mali media IP: three Mali-T800 series GPUs (Mali-T820, Mali-T830, and Mali-T830) based on Midgard architecture, as well as Mali-V500 video accelerator, and the Mali-DP550 display processor. Mali T800 Series GPU The new Mali T-8xx GPUs are based on the same Midgard architecture used in Mali T-6xx and T-7xx GPUs, but deliver better power efficiency thanks to technologies such as ARM Frame Buffer Compression (AFBC), and Adaptive Scalable Texture Compression (ASTC) for imput bandwidth reduction, as well as Transaction Elimination and Smart Composition. ARM provided some performance and energy-comparison between T800 and T600 series (but strangely nothing against T700): The Mali-T820 GPU is optimized for entry-level products, achieving up to 40 percent more performance density compared to the Mali-T622 GPU. The Mali-T830 GPU delivers up to 55 percent more performance than the Mali-T622 GPU. The Mali-T860 GPU provides higher performance and 45 percent more energy-efficiency […]

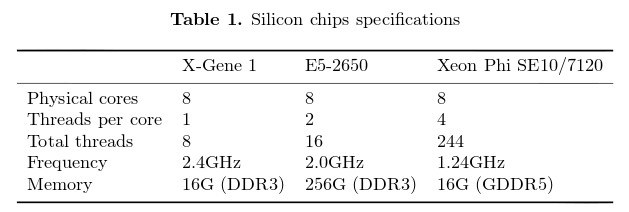

Applied Micro X-Gene (64-bit ARM) vs Intel Xeon (64-bit x86) Performance and Power Usage

A group of researcher at CERN have evaluated Applied Micro X-Gene 1 64-bit ARM XC-1 development board against Intel Xeon E5-2650 and Xeon Phi SE10/7120 systems, and one of them, David Abdurachmanov, presented their findings at ACAT’ 14 conference (Advanced Computing and Analysis Techniques) by listing some of the issues they had to port their software to 64-bit ARM, and performance efficiency of the three systems for data processing of High Energy Physics (HEP) experiments like those at the Large Hadron Collider (LHC), where performance-per-watt is important, as computing systems may scale to several hundred thousands cores. Intel Xeon Phi platform based on Many Integrated Cores (MIC) computer architecture was launched the HPC market, and contrary to the table above features 61 physical cores. Applied X-Gene 1 (40nm process) was used instead of X-Gene 2 built on 28-nm process which was not available at the time. The ARM platform ran […]

Beyond Semi Introduces 32-bit BA20 Core with Cortex M4 Performance Efficiency, and Cortex M0+ Silicon Area

Beyond Semiconductor and CAST have jointly announced BA20 32-bit embedded processor core with PipelineZero Architecture (zero-stage execution pipeline), that rivals with ARM Cortex A4 in terms of performance per MHz, while using about the same silicon area as an ARM Cortex M0+. which could be critical for applications such as wearables, sensors, and wireless communication, that may require both a small footprint and high performance efficiency. The company’s PipelineZero micro-archirtecture can execute one instruction per cycle, hence saving energy by doing more in less time, and by operating at lower clock rates. Key features listed for BA20 IP core: PipelineZero architecture for high performance efficiency with tiny silicon footprint 3.04 DMIPs/MHz (vs ARM Cortex M4: 1.25 DMIPS/MHz) 3.41 Coremarks/MHz (vs ARM Cortex M4: 3.40 CoreMarks/MHz) 2µW/MHz (vs ARM Cortex M0+: 3µW/MHz) 10K gates (0.01mm2) in 9-track 40G (vs 0.009mm2 for ARM Cortex M0+) BA2 ISA Extreme Code Density for less […]

Samsung Officially Announces Exynos 7 Octa big.LITTLE ARM Cortex A53/A57 Processor

Samsung started to commit code related to Exynos 7 processor to mainline kernel in August, but at the time details were scarce, and many tech websites referred to a Exynos 5433 64-bit processor from Samsung. Exynos 5433 for a Cortex A53/A57 SoC did not make much sense as the company recently announced Exynos 5430 based on Cortex A15 and A7 cores, so finally Exynos 5433 has been renamed to Exynos 7 Octa. Here’s what we know about Exynos 7 Octa from information on Exynos 7 Octa page and an older Anandtech article about Exynos 5433: CPU – 4x Cortex A57 cores @ 1.9 GHz , 4x Cortex A53 cores @ 1.3 GHz GPU – Mali-T760 @ 700 MHz Memory Controller – 2x 32-bit @ 825MHz (13.2GB/s b/w) Display – Up to WQHD (2560 x 1440) / WQXGA (2560 x 1600) resolutions Video – Advanced multimedia format codec (MFC) including support […]

Allwinner H8 Octa-core Processor is Designed for Game Consoles and OTT Boxes

Allwinner Technology has just introduced its new octa-core H8 System on Chip (SoC) for “high-end” gaming consoles and video OTT (over-the-top) boxes, right before the Hong Kong Electronics Fair taking place on October 13-16. The processor feature eight Cortex A7 cores clocked at up to 2.0 GHz, coupled with Imagination Technology PowerVR SGX544 GPU @ 700 MHz with support for OpenGL ES 2.0/1.1, OpenCL 1.1 APIs. Other key features includes: Multi-format 1080p@60fps video processing including H.265/HEVC codec. HDMI video output up to 1080P@60fps, with HDCP 2.0 support; support HDMI CEC Integrated 8M image signal processor USB – USB Host, and USB dual-role interfaces Gigabit Ethernet MAC Three SD/MMC controllers SmartColor technology to deliver higher image quality and better visual effects Manufactured with 28nm HPC (High-Performance Compact) process by TSMC. We don’t have the full details, but it does look very similar to Allwinner A83T announced last month, but except of […]